全加器、芯片及计算装置

本发明涉及集成电路,尤其涉及一种全加器、芯片及计算装置。

背景技术:

1、全加器是数字电路的一个基本计算单元,主要用于实现加法、乘法计算等,是计算电路中的重要组成部分,降低功耗和提高性能是全加器设计重要任务。因此,如何实现全加器的性能提高是目前业界亟待解决的重要课题。

技术实现思路

1、本发明提供一种全加器、芯片及计算装置,用以解决现有技术中如何实现全加器的性能提高的问题,实现全加器性能的提升。

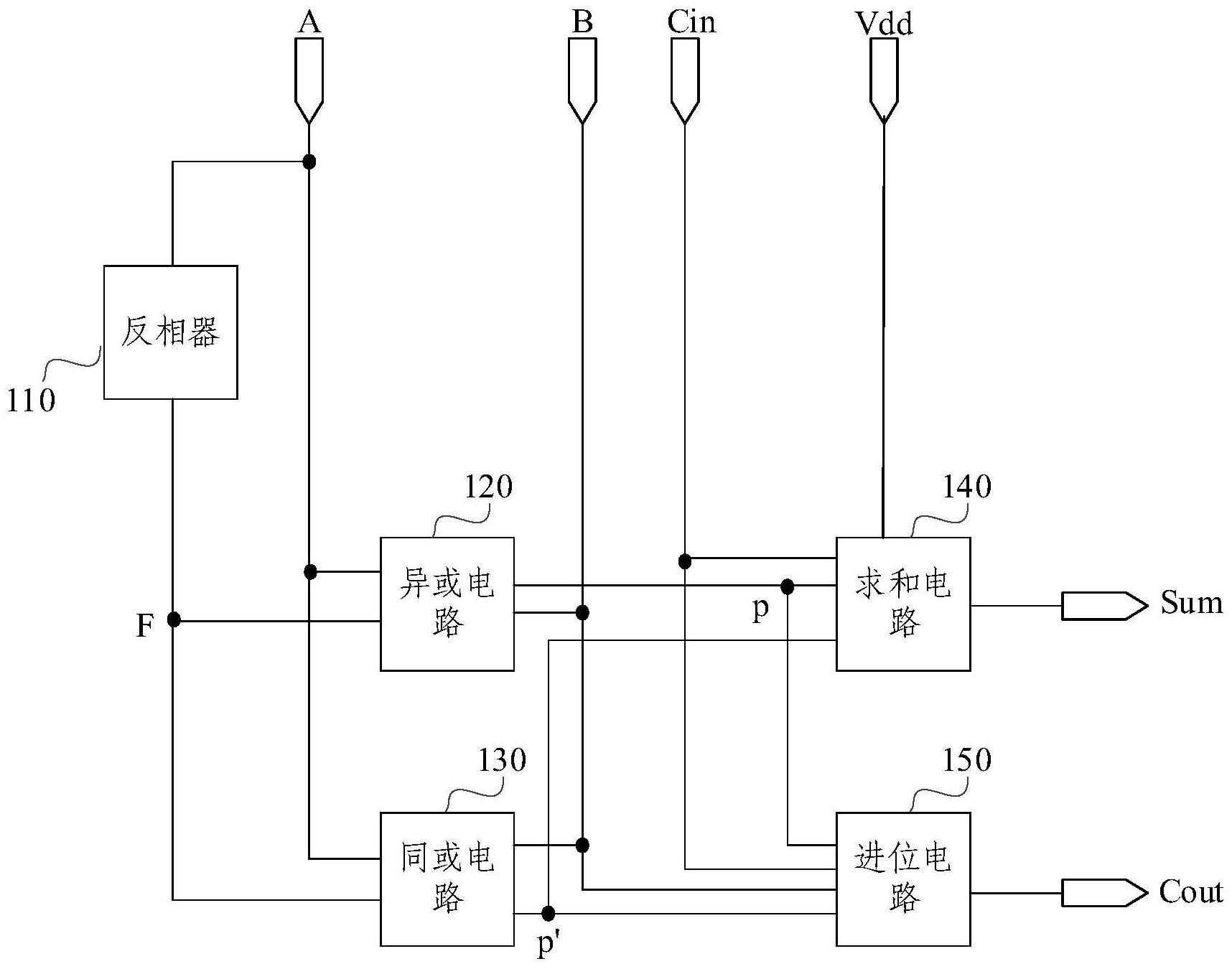

2、本发明提供一种全加器,包括:

3、反相器,分别与第一加数端和第一节点相连,用于对所述第一加数端输入的第一加数信号生成反相信号并提供给所述第一节点;

4、异或电路,分别与所述第一加数端、第二加数端、所述第一节点和第二节点相连,用于基于所述反相信号,对所述第一加数信号和所述第二加数端输入的第二加数信号进行异或计算得到进位传播信号并提供给所述第二节点;

5、同或电路,分别与所述第一加数端、所述第二加数端、所述第一节点和第三节点相连,用于基于所述反相信号,对所述第一加数信号和所述第二加数信号进行同或计算得到同或信号并提供给所述第三节点;

6、求和电路,分别与所述第二节点、所述第三节点、进位输入端、电源端以及和位输出端相连,用于基于所述进位传播信号、所述进位输入端提供的进位输入信号、所述同或信号以及所述电源端提供的电源信号生成所述和位输出端的和位输出信号;其中,在所述第一加数信号为高电平且所述第二加数信号为低电平的情况下,若所述进位输入信号为低电平,在所述同或信号和所述进位输入信号的控制下利用所述电源信号将所述和位输出信号上拉,若所述进位输入信号为高电平,将所述同或信号作为所述和位输出信号。

7、根据本发明提供的一种全加器,所述异或电路包括:第一开关晶体管、第二开关晶体管、第三开关晶体管、第四开关晶体管和第五开关晶体管;所述第一开关晶体管和所述第二开关晶体管为p型开关晶体管;所述第三开关晶体管、所述第四开关晶体管和所述第五开关晶体管为n型开关晶体管;

8、所述第一开关晶体管的栅极、所述第二开关晶体管的第一源极/漏极、所述第五开关晶体管的栅极分别与所述第一加数端相连;

9、所述第二开关晶体管的栅极、所述第一开关晶体管的第一源极/漏极、所述第三开关晶体管的第一源极/漏极以及所述第四开关晶体管的栅极分别与所述第二加数端相连;

10、所述第一开关晶体管的第二源极/漏极、所述第二开关晶体管的第二源极/漏极、所述第三开关晶体管的第二源极/漏极以及所述第四开关晶体管的第一源极/漏极分别与所述第二节点相连;

11、所述第四开关晶体管的第二源极/漏极与所述第五开关晶体管的第一源极/漏极相连;

12、所述第五开关晶体管的第二源极/漏极与接地端相连;

13、所述第三开关晶体管的栅极与所述第一节点相连。

14、根据本发明提供的一种全加器,所述求和电路包括:第一传输门、第六开关晶体管、第七开关晶体管和第八开关晶体管;其中,所述第六开关晶体管和第七开关晶体管为p型开关晶体管;所述第八开关晶体管为n型开关晶体管;

15、所述第六开关晶体管的栅极、第一传输门的输入端以及所述第八开关晶体管的栅极分别与所述进位输入端相连;

16、所述第六开关晶体管的第一源极/漏极与所述电源端相连,所述第六开关晶体管的第二源极/漏极与所述第七开关晶体管的第一源极/漏极相连;

17、所述第七开关晶体管的第二源极/漏极、所述第一传输门的输出端以及所述第八开关晶体管的第一源极/漏极分别与所述和位输出端相连;

18、所述第一传输门的第一控制端与所述第二节点相连;

19、所述第一传输门的第二控制端、所述第七开关晶体管的栅极以及所述第八开关晶体管的第二源极/漏极分别与所述第三节点相连;

20、在所述第一加数信号为高电平且所述第二加数信号为低电平的情况下,若所述进位输入信号为低电平,在所述同或信号和所述进位输入信号的控制下所述第六开关晶体管和所述第七开关晶体管导通所述电源端与所述和位输出端,以利用所述电源信号将所述和位输出信号上拉;

21、在所述第一加数信号为高电平且所述第二加数信号为低电平的情况下,若所述进位输入信号为高电平,在所述进位输入信号的控制下所述第八开关晶体管导通以将所述同或信号作为所述和位输出信号。

22、根据本发明提供的一种全加器,所述同或电路包括:第九开关晶体管、第十开关晶体管、第十一开关晶体管、第十二开关晶体管和第十三开关晶体管;其中,所述第九开关晶体管、第十开关晶体管和第十一开关晶体管为p型开关晶体管;所述第十二开关晶体管和第十三开关晶体管为n型开关晶体管;

23、所述第九开关晶体管的第一源极/漏极、所述第十开关晶体管的栅极、所述第十二开关晶体管的第一源极/漏极以及所述第十三开关晶体管的栅极分别与所述第二加数端相连;

24、所述第十一开关晶体管的栅极、所述第十二开关晶体管的栅极以及所述第十三开关晶体管的第一源极/漏极分别与所述第一加数端相连;

25、所述第九开关晶体管的第二源极/漏极、所述第十开关晶体管的第一源极/漏极、所述第十二开关晶体管的第二源极/漏极以及所述第十三开关晶体管的第二源极/漏极分别与所述第三节点相连;

26、所述第九开关晶体管的栅极与所述第一节点相连;

27、所述第十开关晶体管的第二源极/漏极与所述第十一开关晶体管的第一源极/漏极相连;

28、所述第十一开关晶体管的第二源极/漏极与所述电源端相连。

29、根据本发明提供的一种全加器,所述反相器包括:第十四开关晶体管和第十五开关晶体管;其中,所述第十四开关晶体管为p型开关晶体管;所述第十五开关晶体管为n型开关晶体管;

30、所述第十四开关晶体管的栅极以及所述第十五开关晶体管的栅极分别与所述第一加数端相连;

31、所述第十四开关晶体管的第一源极/漏极与所述电源端相连;

32、所述第十四开关晶体管的第二源极/漏极以及所述第十五开关晶体管的第一源极/漏极分别与所述第一节点相连;

33、所述第十五开关晶体管的第二源极/漏极与接地端相连。

34、根据本发明提供的一种全加器,还包括:进位电路;

35、所述进位电路,分别与所述第二节点、所述第三节点、所述进位输入端、所述第二加数端以及进位输出端相连,用于基于所述进位传播信号、所述同或信号、所述第二加数信号以及所述进位输入信号,生成所述进位输出端的进位输出信号。

36、根据本发明提供的一种全加器,所述进位电路包括:第二传输门和第三传输门;

37、所述第二传输门的第一控制端以及所述第三传输门的第二控制端分别与所述第二节点相连;

38、所述第二传输门的第二控制端以及所述第三传输门的第一控制端分别与所述第三节点相连;

39、所述第二传输门的输入端与所述第二加数端相连;

40、所述第三传输门的输入端与所述进位输入端相连;

41、所述第二传输门的输出端以及所述第三传输门的输出端分别与所述进位输出端相连。

42、根据本发明提供的一种全加器,所述p型开关晶体管为pmos;所述n型开关晶体管为nmos。

43、本发明还提供一种芯片,包括如上述任一种所述的全加器。

44、本发明还提供一种计算装置,包括如上述任一种所述的芯片。

45、本发明提供的全加器,利用反相器对第一加数信号生成反相信号并提供给第一节点,异或电路基于反相信号对第一加数信号和第二加数信号进行异或计算得到进位传播信号并提供给第二节点,同或电路基于反相信号对第一加数信号和第二加数信号进行同或计算得到同或信号并提供给第三节点,在第一加数信号为高电平且第二加数信号为低电平的情况下,若进位输入信号为低电平,求和电路可以在同或信号和进位输入信号的控制下利用电源信号将和位输出信号上拉,若进位输入信号为高电平,求和电路将同或信号作为和位输出信号,从而可以避免在第一加数信号为高电平且第二加数信号为低电平的情况下,因第二节点处的上拉延迟导致的和位输出信号的输出性能降低的问题,从而大大提升了全加器的性能。

- 还没有人留言评论。精彩留言会获得点赞!