一种处理器在片内存储器和FPGA内核中运行程序的方法与流程

本技术涉及计算机,尤其涉及一种处理器在片内存储器和fpga内核中运行程序的方法以及soc fpga芯片。

背景技术:

1、本领域中,可编程逻辑门阵列(field programmable gate array,fpga)芯片可以包括处理器、片内存储器和fpga内核。在系统级芯片(system on chip,soc)fpga芯片的设计中,为了减小soc fpga芯片的面积,片内存储器通常采用存储容量较小的存储器,使得片内存储器只能存储简单的程序的信息。在此种情况下,处理器无法运行比较复杂或者较大容量的程序。

技术实现思路

1、本技术提供一种处理器在片内存储器和fpga内核中运行程序的方法以及socfpga芯片,能够在不增加片外存储器的条件下,解决soc fpga芯片无法运行较大容量的程序的问题。

2、第一方面,本技术提供一种处理器在片内存储器和fpga内核中运行程序的方法。该方法可以应用于soc fpga芯片。所述soc fpga芯片中包括处理器、存储器控制模块、片内存储器和fpga内核,所述fpga内核中包括嵌入式存储器模块(embedded memoy blocks,emb)。其中,处理器可以包括x86处理器、arm处理器等。

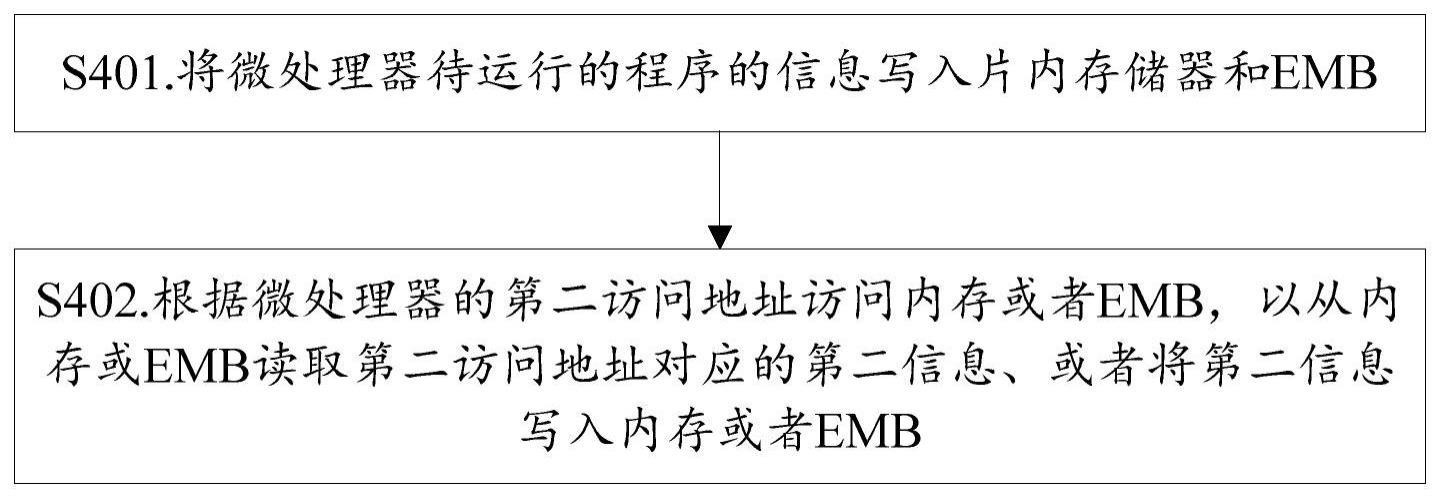

3、所述方法包括:存储器控制模块将所述处理器待运行的程序的信息写入所述片内存储器和所述emb;存储器控制模块根据所述处理器的访问地址访问所述片内存储器或者所述emb,以从所述片内存储器或所述emb读取所述访问地址对应的信息、或者将所述信息写入所述片内存储器或者所述emb。

4、上述实施方式中,将处理器待运行的程序信息写入片内存储器和emb,可以解决程序的容量大于片内存储器的容量的情况下,片内存储器无法满足程序在处理器上运行所需要的存储空间的问题。换言之,在该实施方式中,soc fpga芯片的处理器可以运行较大容量的程序。

5、在第一方面的一种可能的实施方式中,在将所述处理器待运行的程序信息写入所述片内存储器和所述emb之前,所述方法还包括:比较所述信息的容量和所述片内存储器的存储容量;在所述信息的容量大于所述片内存储器的存储容量的情况下,调用fpga内核中emb模块扩充所需存储容量,确定将所述信息写入所述片内存储器和所述emb。在所述信息的容量不大于所述片内存储器的存储容量的情况下,确定将所述信息写入所述片内存储器。

6、其中,在确定将所述信息写入所述片内存储器和所述emb的情况下,可以确定各个信息对应的访问地址,访问地址介于片内存储器或者emb的地址范围。

7、上述实施方式中,通过比较程序需要的容量和片内存储器的存储容量的大小,可以确定是否需要使用emb存储该程序的信息。

8、在第一方面的一种可能的实施方式中,将所述信息写入所述片内存储器和所述emb包括:接收访问地址和所述访问地址对应的信息;若所述访问地址介于所述片内存储器对应的地址范围,将所述信息写入所述片内存储器;若所述访问地址介于所述emb对应的地址范围,将所述信息写入所述emb。其中,soc fpga芯片所在计算设备的非易失性存储器的存储控制器将程序的信息及其对应的访问地址,经过soc fpga芯片内部的系统总线发送给soc fpga芯片内部的存储器控制模块。或者,调试设备将程序的信息及其对应的访问地址发送给soc fpga芯片内部的调试模块,调试模块将程序的信息及其对应的访问地址,经过soc fpga芯片内部的系统总线发送给soc fpga芯片内部的存储器控制模块。

9、上述实施方式中,可以根据各个信息对应的地址,将程序的一部分信息写入片内存储器,将一部分信息写入emb。。

10、在第一方面的一种可能的实施方式中,所述根据所述处理器的访问地址访问所述片内存储器或者所述emb,包括:接收所述处理器发送的所述访问地址;若所述访问地址介于所述片内存储器对应的地址范围,从所述片内存储器读取所述信息;若所述访问地址介于所述emb对应的地址范围,从所述emb读取所述信息。

11、在第一方面的一种可能的实施方式中,所述根据所述处理器的访问地址访问所述片内存储器或者所述emb,包括:接收所述处理器发送的所述访问地址和所述信息;若所述访问地址介于所述片内存储器对应的地址范围,将所述信息写入所述片内存储器;若所述访问地址介于所述emb对应的地址范围,将所述信息写入所述emb。

12、上述实施方式中,存储器控制模块可以根据处理器发送的地址,确定从片内存储器或者emb中读取信息、或者向片内存储器或者emb写入信息。

13、在第一方面的一种可能的实施方式中,所述存储器控制模块包括总线接口、内存储器接口和emb存储器接口;所述总线接口与所述处理器连接,所述片内存储器接口与所述片内存储器连接,所述emb存储器接口与所述emb连接。

14、上述实施方式中,存储器控制模块通过内存储器接口和emb存储器接口与片内存储器和emb连接,使得片内存储器可以根据处理器发送的访问地址访问片内存储器或者emb。例如,当处理器发送的访问地址介于片内存储器对应的地址范围时,存储器控制模块根据该访问地址通过片内存储器接口访问片内存储器;当处理器发送的访问地址介于emb对应的地址范围时,存储器控制模块根据该访问地址通过emb存储器接口访问emb。

15、第二方面,本技术提供一种存储器控制模块。该存储器控制模块可以应用于socfpga芯片中,所述soc fpga芯片中包括处理器、片内存储器和fpga内核,所述fpga内核中包括嵌入式存储器模块emb。该存储器控制模块包括:第一单元和第二单元。

16、其中,第一单元用于将处理器运行的程序的信息写入所述片内存储器和所述emb。

17、其中,第二单元用于根据所述处理器的访问地址访问所述片内存储器或者所述emb,以从所述片内存储器或所述emb读取所述访问地址对应的信息,或者,将所述信息写入所述片内存储器或者所述emb。

18、在第二方面的一种可能的实施方式中,在将所述处理器待运行的程序的信息写入所述片内存储器和所述emb之前,所述方法还包括:比较所述信息的容量和所述片内存储器的存储容量的情况下;在所述信息的容量大于所述片内存储器的存储容量,确定将所述信息写入所述片内存储器和所述emb;在所述信息的容量等于或小于所述片内存储器的存储容量的情况下,确定将所述信息写入所述片内存储器。

19、在第二方面的一种可能的实施方式中,所述第一单元具体用于,接收访问地址和所述访问地址对应的信息;若所述访问地址介于所述片内存储器对应的地址范围,将所述信息写入所述片内存储器;若所述访问地址介于所述emb对应的地址范围,将所述信息写入所述emb。

20、在第二方面的一种可能的实施方式中,所述第二单元具体用于,接收所述处理器发送的所述访问地址;若所述访问地址介于所述片内存储器对应的地址范围,从所述片内存储器读取所述信息;若所述访问地址介于所述emb对应的地址范围,从所述emb读取所述信息。

21、在第二方面的一种可能的实施方式中,所述第二单元具体用于,接收所述处理器发送所述访问地址和所述信息;若所述访问地址介于所述片内存储器对应的地址范围,将所述信息写入所述片内存储器;若所述访问地址介于所述emb对应的地址范围,将所述信息写入所述emb。

22、在第二方面的一种可能的实施方式中,所述存储器控制模块包括总线接口、片内存储器接口、和emb存储器接口;所述总线接口与所述处理器连接,所述片内存储器接口与所述片内存储器连接,所述emb存储器接口与所述emb连接。

23、第三方面,本技术提供一种soc fpga芯片,其特征在于,所述芯片中包括处理器、存储器控制模块、片内存储器和fpga内核,所述fpga内核中包括emb,所述存储器控制模块与所述处理器、所述片内存储器和所述emb连接,所述存储器控制模块用于前述第一方面及其任一可选实施方式中的方法。

24、在第三方面的一种可能的实施方式中,所述存储器控制模块包括总线接口、片内存储器接口、和emb存储器接口;所述总线接口与所述处理器连接,所述片内存储器接口与所述片内存储器连接,所述emb存储器接口与所述emb连接。

25、第四方面,本技术提供一种计算设备,其特征在于,所述计算设备包括:第三方面及其可选实施方式所述的soc fpga芯片。

26、第五方面,本技术提供一种计算机可读存储介质,计算机可读存储介质片内存储器储有指令,当其在计算机上运行时,使得计算机执行上述第一方面或第一方面的任意一种可能的实现方式所提供的方法。

27、第六方面,本技术提供一种包含指令的计算机程序产品,当其在计算机上运行时,使得计算机执行上述第一方面或第一方面的任意一种可能的实现方式所提供的方法。

28、上述提供的任一种存储器控制模块、soc fpga芯片、计算设备或计算机存储介质或计算机程序产品,均用于执行上文所提供的方法,因此,其所能达到的有益效果可参考上文提供的对应方法中的对应方案的有益效果,此处不再赘述。

- 还没有人留言评论。精彩留言会获得点赞!