一种实现在线升级的系统的制作方法

本文涉及但不限于现场可编程逻辑门阵列技术,尤指一种实现在线升级的系统。

背景技术:

1、在航空航天、通信、工业控制、医疗、视频等领域,现场可编程逻辑门阵列(fpga)得到了大量广泛应用。在产品的设计阶段,可以通过联合测试工作组(jtag)下载线缆来更新烧写文件,但在产品成熟进行实际应用时,如果需要对其进行更新配置,则需要开箱拆机,不方便且效率低下,很难适应在线升级的要求。

2、上位机与fpga间以pcie(一种高速串行计算机扩展总线标准)通信接口连接最为常见,可应用于windows或linux环境下,因此可以通过pcie完成上位机对fpga的在线升级功能。相关技术中的升级方案有多种,包括通过外部器件对fpga进行升级或通过fpga直接对flash进行升级。通常的做法是上位机下发配置文件到fpga,然后fpga完成对配置文件的数据提取并存储在第三代双倍数据率同步动态随机存取存储器(ddr3)存储器,同时也需要用到大量的读写fifo缓存,然后通过编写spi总线控制器、flash读写控制器等模块再把缓存中的配置文件写入到外部flash;这种机制会消耗大量的fpga逻辑资源和ram资源,同时也增加了开发调试难度。

3、综上,如何降低资源消耗,实现配置文件的简易烧写,成为一个有待解决的问题。

技术实现思路

1、以下是对本文详细描述的主题的概述。本概述并非是为了限制权利要求的保护范围。

2、本发明实施例提供一种实现在线升级的系统,能够降低配置文件烧写的资源消耗。

3、本发明实施例提供了一种实现在线升级的系统,包括:上位机、现场可编程闸阵列fpga模块和串行外设接口spi闪存flash芯片;其中,

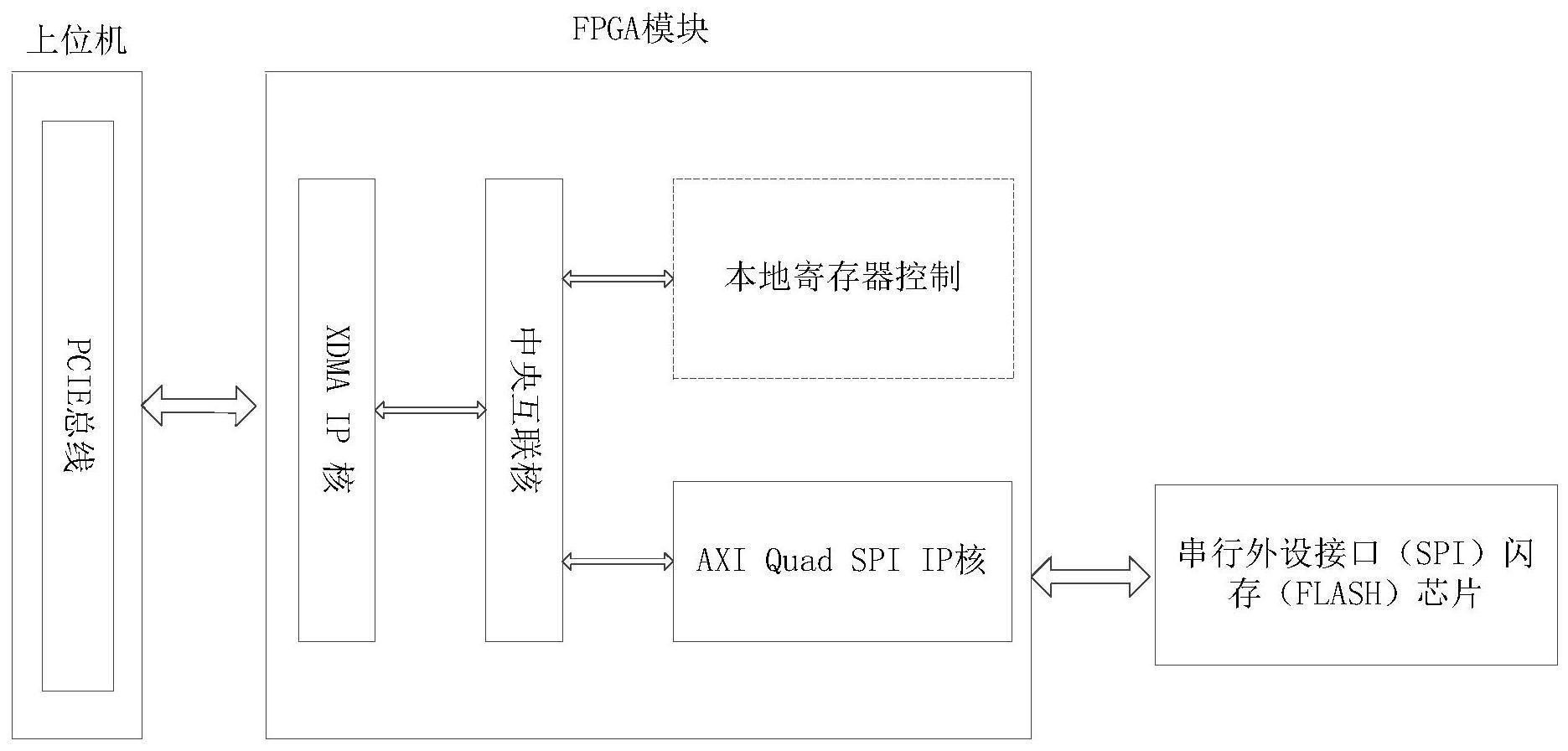

4、上位机与fpga模块之间通过pcie总线连接,fpga模块与spi flash芯片间通过双工quad模式连接;fpga模块包括预先搭建的:用于与pcie总线通信的xdma ip核、用于系统交互的高级可扩展接口axi中央互联interconnect ip核,用于对spi flash芯片执行读写操作的axi quad spi ip核;xdma ip核、中央互联核和axi quad spi ip核通过预设总线连接;

5、上位机设置为:通过pcie总线将使能qe命令通过fpga模块下发到spi flash芯片,以使能spi flash芯片的四线配置模式;通过控制fpga模块中的axi quad spi ip核,对spiflash芯片进行读写操作,将预先存储的配置文件烧写至spi flash芯片;

6、fpga模块设置为:将接收到的使能命令下发到spi flash芯片;通过自身包含的axi quad spi ip核,对spi flash芯片进行读写操作。

7、本申请技术方案包括:上位机、现场可编程闸阵列fpga模块和串行外设接口spi闪存flash芯片;其中,上位机与fpga模块之间通过pcie总线连接,fpga模块与spi flash芯片间通过双工quad模式连接;fpga模块包括预先搭建的:用于与pcie总线通信的xdma ip核、用于系统交互的高级可扩展接口axi中央互联interconnect ip核,用于对spi flash芯片执行读写操作的axi quad spi ip核;xdma ip核、中央互联核和axi quad spi ip核通过预设总线连接;上位机设置为:通过pcie总线将使能命令通过fpga模块下发到spi flash芯片,以使能spi flash芯片;通过控制fpga模块中的axi quad spi ip核,对spi flash芯片进行读写操作,将预先存储的配置文件烧写至spi flash芯片;fpga模块设置为:将接收到的使能命令下发到spi flash芯片;通过自身包含的axi quad spi ip核,对spi flash芯片进行读写操作。本发明实施例简化了在线升级功能逻辑,降低了配置文件烧写时的逻辑资源消耗。

8、本发明的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过在说明书、权利要求书以及附图中所特别指出的结构来实现和获得。

技术特征:

1.一种实现在线升级的系统,包括:上位机、现场可编程闸阵列fpga模块和串行外设接口spi闪存flash芯片;其中,

2.根据权利要求1所述的系统,其特征在于,所述预设总线包括:axi lite总线。

3.根据权利要求1所述的系统,其特征在于,所述axi quad spi ip核为所述quad模式。

4.根据权利要求1所述的系统,其特征在于,所述quad模式包括quad spi四线模型,所述使能命令包括:四线使能qe命令。

5.根据权利要求1所述的系统,其特征在于,所述fpga模块设置为将接收到的使能命令下发到spi flash芯片,包括:

6.根据权利要求1-5任一项所述的系统,其特征在于,所述上位机还设置为:

7.根据权利要求1-5任一项所述的系统,其特征在于,所述上位机还设置:

8.根据权利要求1-5任一项所述的系统,其特征在于,所述配置文件包括:.bin文件。

9.根据权利要求1-5任一项所述的系统,其特征在于,所述系统还包括本地寄存器控制模块,所述上位机还设置为:

10.根据权利要求1-5任一项所述的系统,其特征在于,所述fpga模块设置为通过自身包含的axi quad spi ip核,对spi flash芯片进行读写操作,包括:

11.根据权利要求1-5任一项所述的系统,其特征在于,所述上位机还设置为:

技术总结

本文公开一种实现在线升级的系统,包括:上位机、现场可编程闸阵列(FPGA)模块和串行外设接口(SPI)闪存(FLASH)芯片;上位机通过PCIE总线连接FPGA模块,FPGA模块通过双工模式连接SPI FLASH芯片;FPGA模块包括通过预设总线连接的:与PCIE总线通信的XDMA IP核、用于系统交互的高级可扩展接口中央互联核,对SPI FLASH芯片执行读写操作的AXI Quad SPI IP核;上位机通过PCIE总线将使能(QE)命令通过FPGA模块下发到SPI FLASH芯片,以使能SPI FLASH芯片四线配置模式;通过控制FPGA模块中的AXI Quad SPI IP核,对SPI FLASH芯片进行读写,将配置文件烧写至SPI FLASH芯片;FPGA模块将QE命令下发到SPI FLASH芯片,通过AXI Quad SPI IP核对SPI FLASH芯片进行读写操作。本发明实施例简化了在线升级功能逻辑,降低了配置文件烧写时的逻辑资源消耗。

技术研发人员:马玉平,崔洋,纪德波

受保护的技术使用者:北京旋极信息技术股份有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!