一种基于FPGA动态可重构的串口波特率调节方法与流程

本申请涉及fpga可重构,具体涉及一种基于fpga动态可重构的串口波特率调节方法。

背景技术:

1、可重构技术是指在特定的时序配合下,利用基于sram编程功能的数字器件的特性,对芯片内部数字电路功能重新配置,进而实现编程器件逻辑功能的动态切换。可重构系统的最大特点是在不影响系统正常工作的前提下,根据不同的应用需求,动态改变编程器件的逻辑功能,该特点最大限度的提高了可编程数字器件硬件资源的使用效率以及系统的灵活性。

2、基于sram编程功能的数字器件fpga在上电初始化时要将配置数据写入片内ram中,当配置完成后fpga即可进入工作状态。基于现有fpga的器件特性,如果想要在fpga芯片上进行多种波特率的调节,只能是通过修改rtl代码,重新综合、编译,将生成的bit文件重新加载到fpga外挂的flash中,或者是通过外加arm或者dsp等处理器,在线去配置fpga内部预先设置好的寄存器参数模块,而对于fpga内部大面积的逻辑功能的修改,即进行多种波特率的调节,无法通过简单的配置寄存器实现,或者只有fpga的单处理系统可实现,但同时又无法保证内部逻辑功能改变的精确性。

技术实现思路

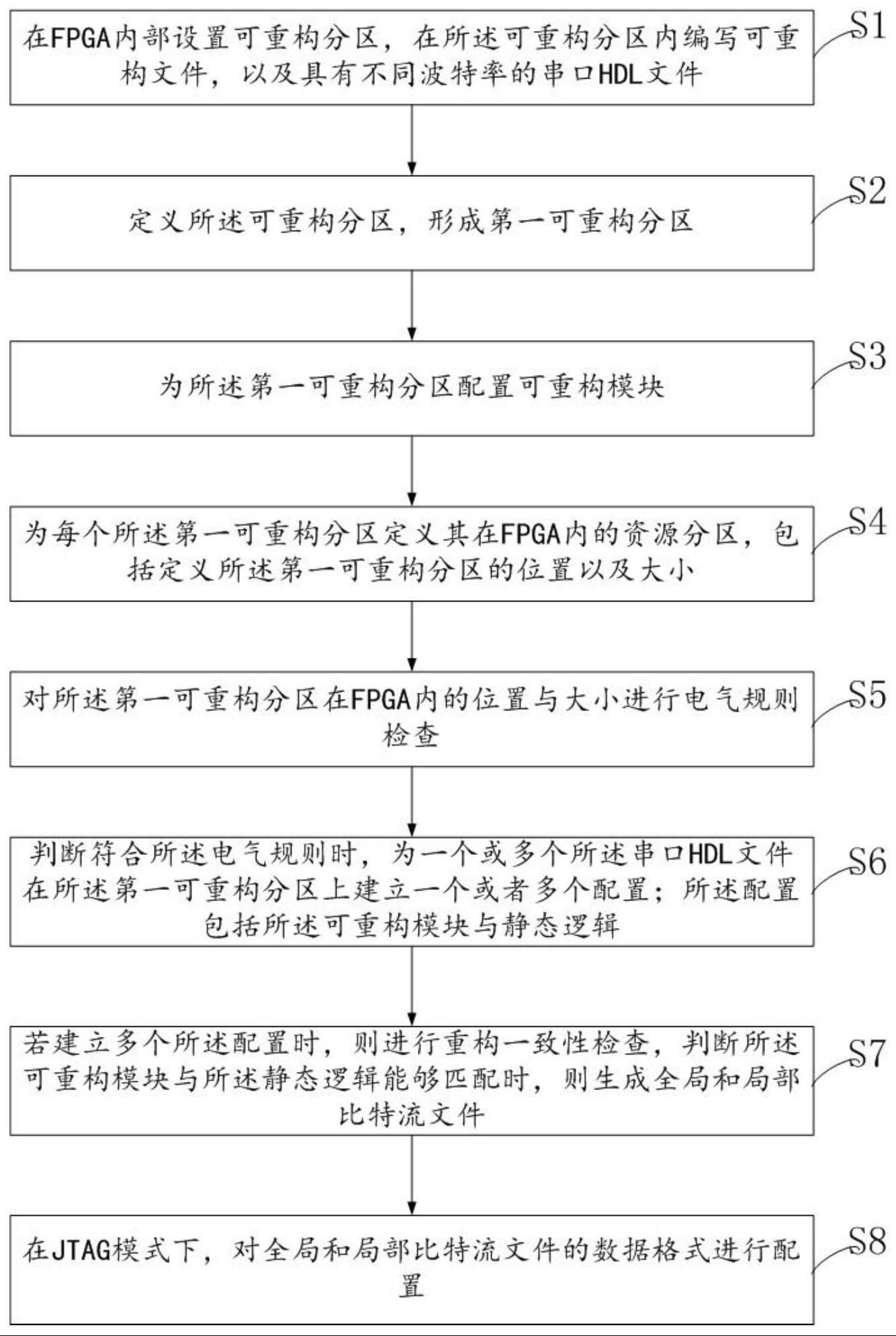

1、本申请的目的是针对以上问题,提供一种基于fpga动态可重构的串口波特率调节方法,包括如下步骤:

2、在fpga内部设置可重构分区,在所述可重构分区内编写可重构文件,以及具有不同波特率的串口hdl文件;

3、定义所述可重构分区,形成第一可重构分区;

4、为所述第一可重构分区配置可重构模块;

5、为每个所述第一可重构分区定义其在fpga内的资源分区,包括定义所述第一可重构分区的位置以及大小;

6、对所述第一可重构分区在fpga内的位置与大小进行电气规则检查;

7、判断符合所述电气规则时,为一个或多个所述串口hdl文件在所述第一可重构分区上建立一个或者多个配置;所述配置包括所述可重构模块与静态逻辑;

8、若建立多个所述配置时,则进行重构一致性检查,判断所述可重构模块与所述静态逻辑能够匹配时,则生成全局和局部比特流文件;

9、在jtag模式下,对全局和局部比特流文件的数据格式进行配置。

10、根据本申请实施例提供的技术方案,fpga内部的逻辑分为一个静态分区static和一个重构分区pr,在所述重构分区pr上设置所述可重构分区。

11、根据本申请实施例提供的技术方案,在所述在fpga内部设置可重构分区,在所述可重构分区内编写可重构文件,以及具有不同波特率的串口hdl文件步骤之后还包括:

12、在所述静态分区static上编写顶层静态hdl文件,并综合所述顶层静态hdl文件与不同波特率的串口hdl文件,形成网表文件。

13、根据本申请实施例提供的技术方案,在所述静态分区static上编写顶层静态hdl文件,并综合所述顶层静态hdl文件、可重构文件,与不同波特率的串口hdl文件,形成网表文件中具体包括:

14、使用编译器对所述顶层静态hdl文件、可重构文件与不同波特率的串口hdl文件进行综合,得到静态顶层hdl文件生成的第一网表文件,以及可重构文件与具有不同波特率的串口hdl文件共同生成的第二网表文件。

15、根据本申请实施例提供的技术方案,在定义所述可重构分区的时候,需要以可重构分区的设计原则为依据。

16、根据本申请实施例提供的技术方案,所述为所述第一可重构分区配置可重构模块之后,还包括:若有数个所述第一可重构分区时,至少为每个所述第一可重构分区配置一个所述可重构模块。

17、根据本申请实施例提供的技术方案,所述第一可重构分区的大小要满足配置在所述第一可重构分区内每个所述可重构模块的资源需求。

18、根据本申请实施例提供的技术方案,在所述电气规则检查之前还包括:对所述第一网表文件与所述第二网表文件进行相关的物理约束与时序约束,其中,所述物理约束指在fpga的所有资源平面进行可重构分区的定义。

19、根据本申请实施例提供的技术方案,若判断不符合所述电气规则时,则重新执行所述为每个所述第一可重构分区定义其在fpga内的资源分区,包括定义所述第一可重构分区的位置以及大小的步骤。

20、根据本申请实施例提供的技术方案,若判断所述可重构模块与所述静态逻辑无法匹配时,则重新执行所述对所述第一可重构分区在fpga内的位置与大小进行电气规则检查的步骤。

21、与现有技术相比,本申请的有益效果:本申请通过在fpga内部设置可重构分区,在可重构分区内编写可重构文件,和具有不同波特率的串口hdl文件,定义设置好的可重构分区,形成第一可重构分区,为第一可重构分区配置可重构模块,并定义第一可重构分区在fpga内的资源分区,包括大小与位置,在定义好大小与位置之后,需要进行电气规则检查,判断其是否符合电气规则,当符合电气规则时,为串口hdl文件在第一可重构分区上建立一个或者多个配置,配置建好之后,需要进行一致性检查,当判断到可重构模块与静态逻辑能够匹配时,则生成全局和局部的比特流文件,在jtag的模式下,对其数据格式进行配置;

22、在使用过程中,首先需要在fpga内部设置可重构分区,并编写可重构文件以及具有不同波特率的串口hdl文件,定义可重构分区并形成第一可重构分区,为第一可重构分区配置可重构模块,并定义其在fpga内的资源分区,包括定义其在fpga内的位置与大小,然后对其位置与大小进行电气规则检查,判断其位置与大小是否符合电气规则,若判断符合电气规则之后,则为一个或多个串口hdl文件建立一个或者多个配置,配置包括可重构模块与静态逻辑,如果建立的是多个配置,则需要对可重构模块与静态逻辑进行一致性检查,当两者能够匹配时,则生成全局和局部的比特流文件,在生成全局和局部的比特流文件之后,需要在jtag的模式下,对全局与局部的比特流文件的数据格式进行配置;

23、本申请通过在fpga内部设置可重构分区,并在可重构分区内编写可重构文件,以及具有不同波特率的串口hdl文件,并定义可重构分区,形成第一可重构分区,为其配置可重构模块,并定义其在fpga内的资源分区,主要包括第一可重构分区的位置与大小,并进行电气规则检查等,与现有技术相比,本申请将可重构技术应用到串口功能调节上,可以解决设备在不断电的情况下,能够在fpga芯片上对不同的波特率进行调节,即能够对fpga内部大面积的逻辑功能进行修改,无需通过外加ram或者dsp等处理器以在线配置fpga内部预先设置好的寄存器参数模块,可以保证fpga内部逻辑功能改变的精确性,本申请可以应用在单路串口和多路串口的情况下,灵活的动态切换各路串口的功能与静态逻辑的组合。

技术特征:

1.一种基于fpga动态可重构的串口波特率调节方法,其特征在于,包括如下步骤:

2.根据权利要求1所述的基于fpga动态可重构的串口波特率调节方法,其特征在于,fpga内部的逻辑分为一个静态分区static和一个重构分区pr,在所述重构分区pr上设置所述可重构分区。

3.根据权利要求2所述的基于fpga动态可重构的串口波特率调节方法,其特征在于,在所述在fpga内部设置可重构分区,在所述可重构分区内编写可重构文件,以及具有不同波特率的串口hdl文件步骤之后还包括:

4.根据权利要求3所述的基于fpga动态可重构的串口波特率调节方法,其特征在于,在所述静态分区static上编写顶层静态hdl文件,并综合所述顶层静态hdl文件、可重构文件,与不同波特率的串口hdl文件,形成网表文件中具体包括:

5.根据权利要求4所述的基于fpga动态可重构的串口波特率调节方法,其特征在于,在定义所述可重构分区的时候,需要以可重构分区的设计原则为依据。

6.根据权利要求5所述的基于fpga动态可重构的串口波特率调节方法,其特征在于,所述为所述第一可重构分区配置可重构模块之后,还包括:若有数个所述第一可重构分区时,至少为每个所述第一可重构分区配置一个所述可重构模块。

7.根据权利要求6所述的基于fpga动态可重构的串口波特率调节方法,其特征在于,所述第一可重构分区的大小要满足配置在所述第一可重构分区内每个所述可重构模块的资源需求。

8.根据权利要求7所述的基于fpga动态可重构的串口波特率调节方法,其特征在于,在所述电气规则检查之前还包括:对所述第一网表文件与所述第二网表文件进行相关的物理约束与时序约束,其中,所述物理约束是指在fpga的所有资源平面对可重构分区进行定义。

9.根据权利要求8所述的基于fpga动态可重构的串口波特率调节方法,其特征在于,若判断不符合所述电气规则时,则重新执行所述为每个所述第一可重构分区定义其在fpga内的资源分区,包括定义所述第一可重构分区的位置以及大小的步骤。

10.根据权利要求9所述的基于fpga动态可重构的串口波特率调节方法,其特征在于,若判断所述可重构模块与所述静态逻辑无法匹配时,则重新执行所述对所述第一可重构分区在fpga内的位置与大小进行电气规则检查的步骤。

技术总结

本申请提供一种基于FPGA动态可重构的串口波特率调节方法,包括如下步骤:在FPGA内设可重构分区,在其内编写可重构文件,和具有不同波特率的串口HDL文件;定义可重构分区,形成第一可重构分区;为第一可重构分区配置可重构模块;并定义其在FPGA内的资源分区的位置与大小;并进行电气规则检查;若符合,则建立一或多个包括可重构模块与静态逻辑的配置;当为多个时,则重构一致性检查,若通过检查时,则生成全局和局部比特流文件;在JTAG模式下,对全局和局部比特流文件的数据格式进行配置;本申请将可重构技术应用到串口功能调节上,可以解决设备在不断电的情况下,能够对可重构分区内不同的波特率进行调节。

技术研发人员:代红超

受保护的技术使用者:天津津航计算技术研究所

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!