一种快速检查stub测试孔的方法、装置及可读介质与流程

所属的技术人员能够理解,本发明的各个方面可以实现为系统、方法或程序产品。因此,本发明的各个方面可以具体实现为以下形式,即:完全的硬件实施方式、完全的软件实施方式(包括固件、微代码等),或硬件和软件方面结合的实施方式,这里可以统称为“电路”、“模块”或“系统”。根据本实施例的模块、子模块、单元、子单元中的任意多个、或其中任意多个的至少部分功能可以在一个模块中实现。根据本实施例的模块、子模块、单元、子单元中的任意一个或多个可以被拆分成多个模块来实现。根据本实施例的模块、子模块、单元、子单元中的任意一个或多个可以至少被部分地实现为硬件电路,例如现场可编程门阵列(fpga)、可编程逻辑阵列(pla)、片上系统、基板上的系统、封装上的系统、专用集成电路(asic),或可以通过对电路进行集成或封装的任何其他的合理方式的硬件或固件来实现,或以软件、硬件以及固件三种实现方式中任意一种或以其中任意几种的适当组合来实现。或者,根据本实施例的模块、子模块、单元、子单元中的一个或多个可以至少被部分地实现为计算机程序模块,当该计算机程序模块被运行时,可以执行相应的功能。在一个实施例中,本发明提供一种快速检查stub测试孔的设备可以包括至少一个处理单元、以及至少一个存储单元。其中,存储单元存储有程序代码,当程序代码被处理单元执行时,使得处理单元执行本说明书上述描述的根据本发明各种示例性实施方式的快速检查stub测试孔的中的步骤。例如,处理单元可以执行如图1所示的快速检查stub测试孔的方法的流程。在一个实施例中,本发明提供一种计算机可读介质,该存储有计算机可执行指令,计算机可执行指令用于执行本说明书上述描述的根据本发明各种示例性实施方式的快速检查stub测试孔的方法中的步骤。可读介质可以是可读信号介质或者可读存储介质。可读存储介质例如可以是——但不限于——电、磁、光、电磁、红外线、或半导体的系统、装置或器件,或者任意以上的组合。可读信号介质可以包括在基带中或者作为载波一部分传播的数据信号,其中承载了可读程序代码。可读信号介质还可以是可读存储介质以外的任何可读介质,该可读介质可以发送、传播或者传输用于由指令执行系统、装置或者器件使用或者与其结合使用的程序。可读介质上包含的程序代码可以用任何适当的介质传输,包括——但不限于——无线、有线、光缆、rf等等,或者上述的任意合适的组合。在一个实施例中,本发明提供一种计算机程序产品,该计算机程序产品包括计算机指令,该计算机指令存储在计算机可读存储介质中。计算设备的处理器可以从计算机可读存储介质读取该计算机指令,处理器执行该计算机指令,使得计算设备执行上述实施方式的快速检查stub测试孔的方法中的步骤。此外,尽管在附图中以特定顺序描述了本发明方法的操作,但是,这并非要求或者暗示必须按照该特定顺序来执行这些操作,或是必须执行全部所示的操作才能实现期望的结果。附加地或备选地,可以省略某些步骤,将多个步骤合并为一个步骤执行,和/或将一个步骤分解为多个步骤执行。应当理解的是,对本领域普通技术人员来说,可以根据上述说明加以改进或变换,而所有这些改进和变换都应属于本发明所附权利要求的保护范围。上面结合附图对本发明专利进行了示例性的描述,显然本发明专利的实现并不受上述方式的限制,只要采用了本发明专利的方法构思和技术方案进行的各种改进,或未经改进将本发明专利的构思和技术方案直接应用于其它场合的,均在本发明的保护范围内。

背景技术:

1、在平常的pcb layout设计中,制版厂为了快速的检测电路板中线路的开短路、不良线路、元器件的缺件、错件、元器件的缺陷、焊接不良等,会要求layout工程师设计时在一些信号上加上ict测试点,这类测试点有的是表贴的也有一些是加在过孔上的。

2、测试点的引入虽然方便了板厂进行pcba检测,但也给设计带来了风险。因为pcblayout设计不是一次就完成的,中途伴随方案更改,线路也要进行相应的调整,以i2c信号为例,后期由于拓扑的更改,走线方式发生了改变,layout工程师由于某种原因没有及时将更改前的错误线路上删除干净,如果这样直接生产的话,这个信号就会带有很长的stub,这个stub对板子的检测虽然没有影响,但是会影响信号的质量,造成信号传输出错,设备调试不通,故stub测试孔的后期检查是很重要的。

3、目前,cadence软件仅仅是提供了dangling vias的检查,dangling vias主要是用来检测pcb中多余的过孔,即stub过孔,这些stub过孔如果不删除不仅会影响制版效率,增加无用的钻孔,还会形成信号的stub,造成天线效应,严重影响信号质量,使数据丢包,设备无法正常使用。

4、但是,当stub过孔加上测试属性后cadence软件会默认这个一个正常的via过孔,从而在dangling vias的报表上无法报出此类stub测试孔。由于软件无法及时排查,为了保证设计质量只能去依靠人工将所有测试点都点亮,然后一个过孔一个过孔的整版去检查,这显然是不太现实的,因为需要测试点的一般都是上万pin的大规模项目,采用人工方式去一个个检查,费时费力没有效率,严重耽误项目进展,还存在人为因素导致检查不到位或是遗漏的情况。

技术实现思路

1、为了克服现有技术中采用人工方式去检查stub测试孔存在费时费力,严重耽误项目进展,还存在人为因素导致检查不到位或是遗漏的问题,本发明提供了一种快速检查stub测试孔的方法、装置及可读介质。

2、本发明技术方案如下所述:

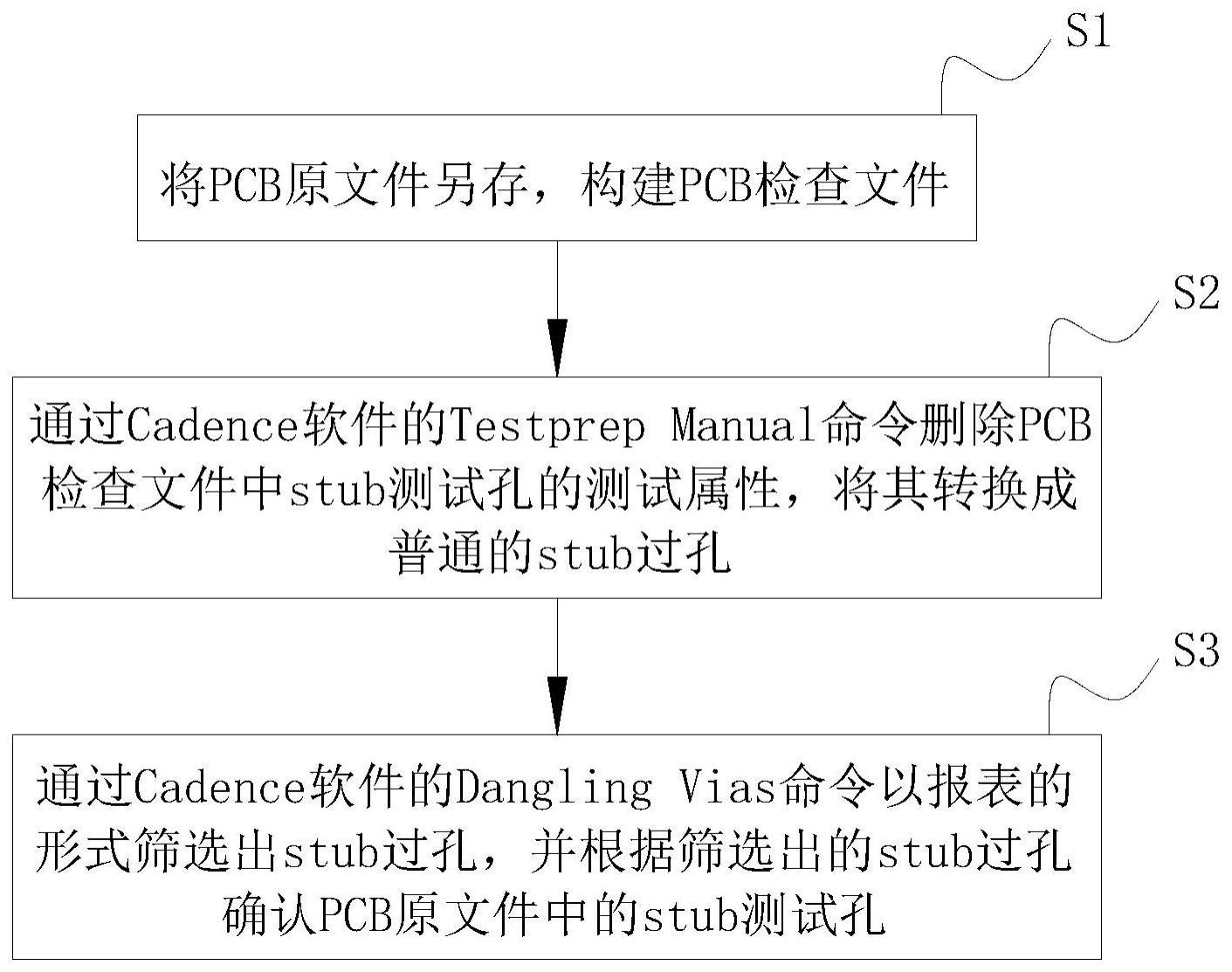

3、第一方面,本发明提供一种快速检查stub测试孔的方法,基于cadence软件,包括以下步骤:

4、步骤s1、将pcb原文件另存,构建pcb检查文件,pcb检查文件的版本格式与pcb原文件的版本格式一致;

5、步骤s2、通过cadence软件的testprep manual命令删除pcb检查文件中stub测试孔的测试属性,将其转换成普通的stub过孔;

6、步骤s3、通过cadence软件的dangling vias命令以报表的形式筛选出stub过孔,并根据筛选出的stub过孔确认pcb原文件中的stub测试孔。

7、根据上述方案的快速检查stub测试孔的方法,在步骤s1中,通过cadence软件的file-save as命令另存pcb原文件,构建pcb检查文件。

8、根据上述方案的快速检查stub测试孔的方法,pcb原文件和pcb检查文件的格式均为brd格式。

9、根据上述方案的快速检查stub测试孔的方法,在步骤s1中,构建完pcb检查文件后,关掉对pcb检查文件的动态铜皮和drc检查。

10、根据上述方案的快速检查stub测试孔的方法,在步骤s1中,通过cadence软件的status命令关掉对pcb检查文件的动态铜皮和drc检查。

11、根据上述方案的快速检查stub测试孔的方法,步骤s2包括以下子步骤:

12、步骤s201、打开testprep manual命令;

13、步骤s202、勾选显示界面的delet选项;

14、步骤s203、框选pcb检查文件的所有内容。

15、根据上述方案的快速检查stub测试孔的方法,在步骤s3中,确认pcb原文件中的stub测试孔后,将其删除。

16、第二方面,本发明提供一种快速检查stub测试孔的装置,包括:

17、至少一个处理器;以及

18、与所述至少一个处理器通信连接的存储器;其中,

19、所述存储器存储有可被所述至少一个处理器执行的指令,所述指令被所述至少一个处理器执行,以使所述至少一个处理器能够执行上述的快速检查stub测试孔的方法。

20、第三方面,本发明提供一种计算机可读介质,存储有计算机可执行指令,所述计算机可执行指令用于执行上述的快速检查stub测试孔的方法。

21、根据上述方案的本发明,其有益效果在于:

22、本发明提供的快速检查stub测试孔的方法,基于cadence软件,通过另存一个pcb检查文件,并将pcb检查文件中带测试属性的stub测试孔转换成可被dangling vias筛选出的不带测试属性的stub过孔,从而根据筛选的stub过孔确认pcb原文件中的stub测试孔,确认后在pcb原文件中将其删除即可,这样通过软件检查的准确率和工作效率与人工整版检查相比提升了许多,且操作简单、步骤少。

- 还没有人留言评论。精彩留言会获得点赞!