支持不同计算模式的单比特脉动阵列结构的制作方法

本发明涉及人工智能领域,具体为一种支持不同计算模式的单比特脉动阵列结构。

背景技术:

1、随着人工智能的兴起,深度学习在各个领域中的应用也越来越多。而深度学习中,与矩阵相乘相关的运算使用率极高。目前比较方便快捷的矩阵运算方式是用脉动阵列,而脉动阵列的基本思路为:在a*b=y的矩阵乘法运算中,固定矩阵b,使a在脉动阵列单元中流动而连续输出y;或者是使a和b在脉动阵列单元中流动而将结果y存储于脉动阵列单元中。本发明在前一种方式的基础上进行了改进,即在矩阵运算中,先将矩阵a存储于相应的阵列单元的寄存器中,输入矩阵b,计算结果在阵列单元中流动并经选择电路输出。

2、神经网络中经常会进行单比特的矩阵乘法,而单比特的矩阵乘法很多时候并不仅仅局限于常规的乘累加计算,很多时候会将乘法计算替换成同或,异或,与,与非等其他的计算并进行累加。

3、因此,亟需一种方案来提高脉动阵列对于不同计算模式的适应性。

技术实现思路

1、为克服上述现有技术的不足,本发明提供一种支持不同计算模式的单比特脉动阵列结构,用以提高脉动阵列对于不同计算模式的适应性。

2、本发明是根据如下技术方案实现的:

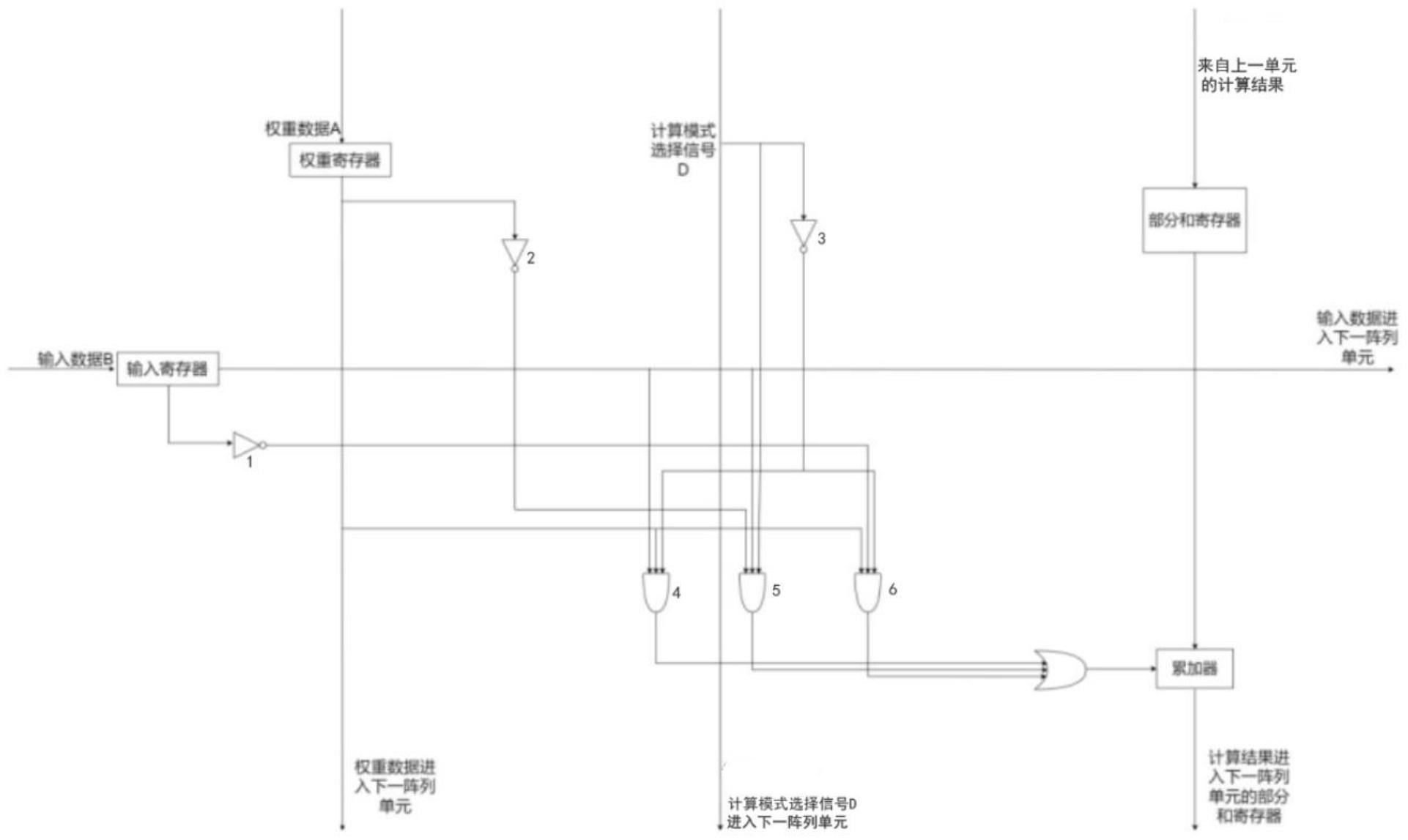

3、支持不同计算模式的单比特脉动阵列结构,包括选择电路和呈阵列排布的多个脉动阵列单元,各所述脉动阵列单元均包括输入寄存器、权重寄存器、部分和寄存器、第一非门、第二非门、第三非门、第一三输入与门、第二三输入与门、第三三输入与门、三输入或门和累加器;

4、所述输入寄存器的输出端连接第一非门的输入端,所述权重寄存器的输出端连接第二非门的输入端,所述第三非门的输入端输入内部选择信号;所述部分和寄存器的输入端与上一脉动阵列单元的累加器的输出端连接,所述部分和寄存器的的输出端连接累加器的第一输入端,所述累加器的第二输入端连接三输入或门的输出端,所述三输入或门的三个输入端分别连接第一三输入与门的输出端、第二三输入与门的输出端、第三三输入与门的输出端;所述第一三输入与门的输入端分别连接输入寄存器的输出端、权重寄存器的输出端、第三非门的输出端;所述第二三输入与门的输入端分别连接第二非门的输出端、输入寄存器的输出端及内部选择信号;所述第三三输入与门的输入端分别连接权重寄存器的输出端、第一非门的输出端、第三非门的输出端;

5、所述选择电路与脉动阵列结构中最后一行脉动阵列单元的累加器连接,根据外部选择信号将所述最后一行脉动阵列单元的累加器的计算结果进行按位取反后输出或直接输出。

6、可选地,所述单比特脉动阵列结构还包括选择电路,用于接入外部选择信号。

7、可选地,在外部选择信号=0,内部选择信号=0时,所述单比特脉动阵列结构进行单比特与运算。

8、可选地,在外部选择信号=0,内部选择信号=1时,所述单比特脉动阵列结构进行单比特异或运算。

9、可选地,在外部选择信号=1,内部选择信号=1时,所述单比特脉动阵列结构进行单比特同或运算。

10、可选地,在外部选择信号=1,内部选择信号=0时,所述单比特脉动阵列结构进行单比特与非运算。

11、可选地,所述的外部选择信号和内部选择信号在同一次计算中保持不变。

12、可选地,各行脉动阵列单元呈矩形阵列排布;

13、位于同一行的脉动阵列单元,当前列脉动阵列单元的输入寄存器的输出端连接下一列脉动阵列单元的输入寄存器的输入端;

14、位于同一列的脉动阵列单元,当前行脉动阵列单元的权重寄存器的输出端连接下一行脉动阵列单元的权重寄存器的输入端,当前行脉动阵列单元的累加器的输出端连接下一行脉动阵列单元的部分和寄存器的输入端。

15、与现有技术相比,本发明的有益效果在于:

16、本发明在原有脉动阵列的基础上进行了改动,先将矩阵a存储于相应的阵列单元的寄存器中,输入矩阵b,两个矩阵的计算结果在阵列单元中流动并经选择电路输出,使脉动阵列可以更好地支持异或、同或、与、与非四种不同类型的单比特矩阵乘法计算,可以有效提高脉动阵列对于不同类型的矩阵乘法的适应性。

技术特征:

1.支持不同计算模式的单比特脉动阵列结构,其特征在于,包括选择电路和呈阵列排布的多个脉动阵列单元,各所述脉动阵列单元均包括输入寄存器、权重寄存器、部分和寄存器、第一非门、第二非门、第三非门、第一三输入与门、第二三输入与门、第三三输入与门、三输入或门和累加器;

2.根据权利要求1所述支持不同计算模式的单比特脉动阵列结构,其特征在于,在外部选择信号=0,内部选择信号=0时,所述单比特脉动阵列结构进行单比特与运算。

3.根据权利要求1所述支持不同计算模式的单比特脉动阵列结构,其特征在于,在外部选择信号=0,内部选择信号=1时,所述单比特脉动阵列结构进行单比特异或运算。

4.根据权利要求1所述支持不同计算模式的单比特脉动阵列结构,其特征在于,在外部选择信号=1,内部选择信号=1时,所述单比特脉动阵列结构进行单比特同或运算。

5.根据权利要求1所述支持不同计算模式的单比特脉动阵列结构,其特征在于,在外部选择信号=1,内部选择信号=0时,所述单比特脉动阵列结构进行单比特与非运算。

6.根据权利要求1所述支持不同计算模式的单比特脉动阵列结构,其特征在于,所述外部选择信号和内部选择信号在同一次计算中保持不变。

7.根据权利要求1所述支持不同计算模式的单比特脉动阵列结构,其特征在于,各行脉动阵列单元呈矩形阵列排布;

技术总结

本发明公开一种支持不同计算模式的单比特脉动阵列结构,包括选择电路和呈阵列排布的多个脉动阵列单元。每个脉动阵列单元由一个输入寄存器,一个权重寄存器,三个非门,三个三输入与门,一个三输入或门,一个累加器和一个部分和寄存器组成,所述选择电路与脉动阵列结构中最后一行脉动阵列单元的累加器连接。本发明使用逻辑门对单比特的计算进行了处理,使用计算模式选择信号实现不同的计算方案,从而提高了脉动阵列对于不同计算模式的适应性。

技术研发人员:乔树山,张默寒,游恒,尚德龙,周玉梅

受保护的技术使用者:中科南京智能技术研究院

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!