一种数字信号处理装置及其EMIF接口扩展方法与流程

本发明涉及信号处理,具体是一种数字信号处理装置及其emif接口扩展方法。

背景技术:

1、按照传统设计,通用信号处理设备中数字信号处理器(dsp)的并口通常为一驱多,通常会包括flash、nvram以及多个fpga等,但随着机架整体性能的提升,对单个板卡的功耗与尺寸要求越来越高,在高密低功耗信号处理板的dsp选型时,但随着机架整体性能的提升,对板卡上主要芯片选型要求尺寸小、功耗低、运算能力强,对dsp与fpga选型至关重要。

2、但由于dsp芯片emif接口只引出了一个片选,传统架构存在以下问题:1)dsp的emif只能用于连接flash做启动用;2)dsp无法通过emif连接各自的nvram;3)dsp1与dsp2无法连接信号处理fpga1与控制fpga3,dsp3无法连接信号处理fpga2与控制fpga3。

技术实现思路

1、为克服现有技术的不足,本发明提供了一种数字信号处理装置及其emif接口扩展方法,解决现有技术存在的机载设备集成度低、可靠性低、机载设备敏感的功耗等问题。

2、本发明解决上述问题所采用的技术方案是:

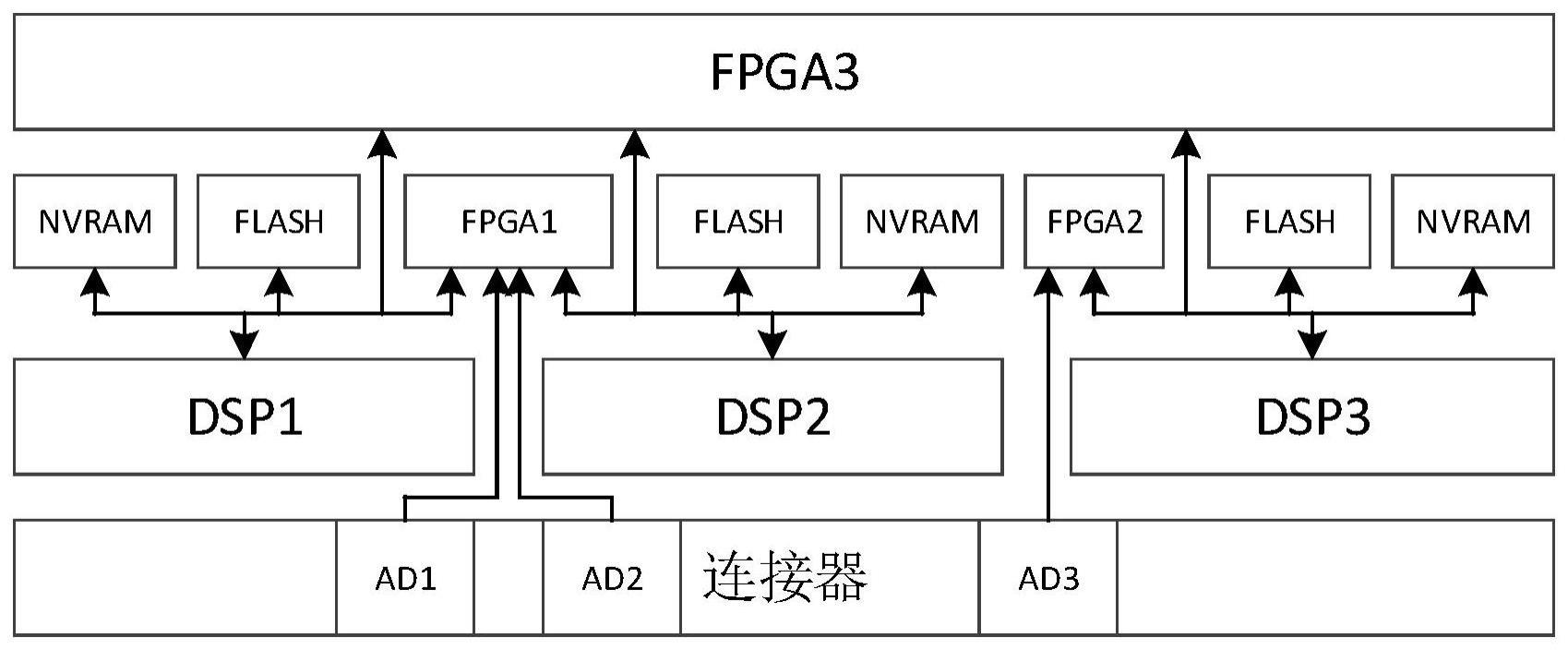

3、一种数字信号处理装置,包括:

4、3个ad通道,分别记为ad1、ad2、ad3;

5、3个dsp,分别记为dsp1、dsp2、dsp3;

6、2个信号处理fpga,分别记为fpga1、fpga2;

7、1个控制管理fpga,记为fpga3;

8、ad1、ad2分别与fpga1连接,ad3与fpga2连接;

9、dsp1的emif接口与fpga1、fpga3分别电连接,dsp2的emif接口与fpga1、fpga3分别电连接,dsp3的emif接口与fpga2、fpga3分别电连接。

10、作为一种优选的技术方案,dsp1的emif接口的全部地址线a[25:0]、全部数据线d[15:0]、全部控制线/cs/we/oe分别与fpga3电连接;

11、dsp1的emif接口的部分地址线a[22:0]、全部数据线d[15:0]以及部分控制线/we/oe分别与fpga1电连接;

12、dsp1的emif接口的高位地址线a[25:23]、片选信号/cs分别与fpga3电连接。

13、作为一种优选的技术方案,dsp2的emif接口的全部地址线a[25:0]、全部数据线d[15:0]、全部控制线/cs/we/oe分别与fpga3电连接;

14、dsp1的emif接口的部分地址线a[22:0]、全部数据线d[15:0]以及部分控制线/we/oe分别与fpga1电连接;

15、dsp2的emif接口的高位地址线a[25:23]、片选信号/cs分别与fpga3电连接。

16、作为一种优选的技术方案,dsp3的emif接口的全部地址线a[25:0]、数据线d[15:0]、控制线/cs/we/oe分别与fpga3电连接;

17、dsp3的emif接口的部分地址线a[22:0]、全部数据线d[15:0]、部分控制线/we/oe分别与fpga2电连接;

18、dsp3的的emif接口的高位地址线a[25:23]、片选信号/cs分别与fpga3电连接。

19、作为一种优选的技术方案,还包括3个nvram,分别记为nvram1、nvram2、nvram3,dsp1的emif接口与nvram1电连接,dsp2的emif接口与nvram2电连接,dsp3的emif接口与nvram3电连接。

20、作为一种优选的技术方案,还包括3个flash,分别记为flash1、flash2、flash3,dsp1的emif接口与flash1电连接,dsp2的emif接口与flash2电连接,dsp3的emif接口与flash3电连接。

21、作为一种优选的技术方案,ad1通过204b接口与fpga1连接。

22、作为一种优选的技术方案,ad2通过204b接口与fpga1连接。

23、作为一种优选的技术方案,ad3通过204b接口与fpga2连接。

24、一种数字信号处理装置的emif接口扩展方法,采用所述的一种数字信号处理装置。

25、本发明相比于现有技术,具有以下有益效果:

26、(1)本发明从数据空间上来看,将dsp的emif数据空间分为4个32mb空间,这样,dsp与fpga3进行配合,可以实现对每个器件访问的最大空间为256mb,只是对每个器件的访问是分块访问,访问空间大于32mb时,需要dsp先对待操作的数据进行切分,使得每一块数据最大为32mb,这样可保证对emif总线下所有器件可访问到全空间,且能做到空间连续性访问。

27、(2)同时,本发明在fpga3中对emif片选信号扩展时,fpga3内部逻辑做了时序逻辑的处理,无需dsp额外配置fpga3,只比不经过fpga3扩展场景多了一个fpga3工作时钟周期(该周期低于dsp的emif模块工作时钟周期),而dsp并口的时序参数配置的裕量已经能完全将此时间上的开销包含,并还有较多的时序裕量,从而保证了emif接口的时序。emif随机读时序如图4所示,dsp的emif模块默认工作时钟为125mhz,以nor flash的典型随机读时序进行时序确认,dsp典型的时序参数配置对nor flash的读写访问时序裕量充足。即,在扩展emif接口的条件下,dsp的emif接口速率不受影响。

技术特征:

1.一种数字信号处理装置,其特征在于,包括:

2.根据权利要求1所述的一种数字信号处理装置,其特征在于,dsp1的emif接口的全部地址线a[25:0]、全部数据线d[15:0]、全部控制线/cs/we/oe分别与fpga3电连接;

3.根据权利要求2所述的一种数字信号处理装置,其特征在于,dsp2的emif接口的全部地址线a[25:0]、全部数据线d[15:0]、全部控制线/cs/we/oe分别与fpga3电连接;

4.根据权利要求3所述的一种数字信号处理装置,其特征在于,dsp3的emif接口的全部地址线a[25:0]、数据线d[15:0]、控制线/cs/we/oe分别与fpga3电连接;

5.根据权利要求1所述的一种数字信号处理装置,其特征在于,还包括3个nvram,分别记为nvram1、nvram2、nvram3,dsp1的emif接口与nvram1电连接,dsp2的emif接口与nvram2电连接,dsp3的emif接口与nvram3电连接。

6.根据权利要求1所述的一种数字信号处理装置,其特征在于,还包括3个flash,分别记为flash1、flash2、flash3,dsp1的emif接口与flash1电连接,dsp2的emif接口与flash2电连接,dsp3的emif接口与flash3电连接。

7.根据权利要求1所述的一种数字信号处理装置,其特征在于,ad1通过204b接口与fpga1连接。

8.根据权利要求1所述的一种数字信号处理装置,其特征在于,ad2通过204b接口与fpga1连接。

9.根据权利要求1所述的一种数字信号处理装置,其特征在于,ad3通过204b接口与fpga2连接。

10.一种数字信号处理装置的emif接口扩展方法,其特征在于,采用权利要求1至9任一项所述的一种数字信号处理装置。

技术总结

本发明涉及信号处理技术领域,公开了一种数字信号处理装置及其EMIF接口扩展方法,该装置,包括:3个AD通道,分别记为AD1、AD2、AD3;3个DSP,分别记为DSP1、DSP2、DSP3;2个信号处理FPGA,分别记为FPGA1、FPGA2;1个控制管理FPGA,记为FPGA3;AD1、AD2分别与FPGA1连接,AD3与FPGA2连接;DSP1的EMIF接口与FPGA1、FPGA3分别电连接,DSP2的EMIF接口与FPGA1、FPGA3分别电连接,DSP3的EMIF接口与FPGA2、FPGA3分别电连接。本发明解决了现有技术存在的机载设备集成度低、可靠性低、机载设备敏感的功耗等问题。

技术研发人员:许虎,唐洪军,郑百衡,马力科,吴海燕,韩毅辉,程昊腾,何燕军

受保护的技术使用者:中国电子科技集团公司第十研究所

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!