基于C-SKY架构芯片降低GPIO中断响应时间的方法、芯片和装置与流程

本技术涉及计算机,特别是涉及一种基于c-sky架构芯片降低gpio中断响应时间的方法、降低gpio中断响应时间的芯片、基于c-sky架构芯片降低gpio中断响应时间的装置、服务器、存储介质和计算机程序产品。

背景技术:

1、gpio引脚(general-purpose input/output)是通用芯片中输入输出端口上的功能引脚,它具有输入、输出、中断检测等功能。其中中断检测功能是gpio引脚最重要的一项功能,芯片可以通过gpio引脚的交互中断而感知外部的变化,从而做出相应的动作。

2、在当gpio引脚产生中断时,状态寄存器会将对应引脚的中断状态进行保存,从而操作系统可以通过轮询状态寄存器的方式来检测gpio引脚的中断状态,并在发现某gpio引脚产生中断时,调用该gpio引脚的中断服务程序对其进行中断处理。但是目前通过轮询状态寄存器的方式,存在检测时间较长,效率不高的问题,从而增加了芯片应用的不稳定性。

技术实现思路

1、基于此,有必要针对上述技术问题,提供一种基于c-sky架构芯片降低gpio中断响应时间的方法、降低gpio中断响应时间的芯片、基于c-sky架构芯片降低gpio中断响应时间的装置、服务器、存储介质和计算机程序产品。

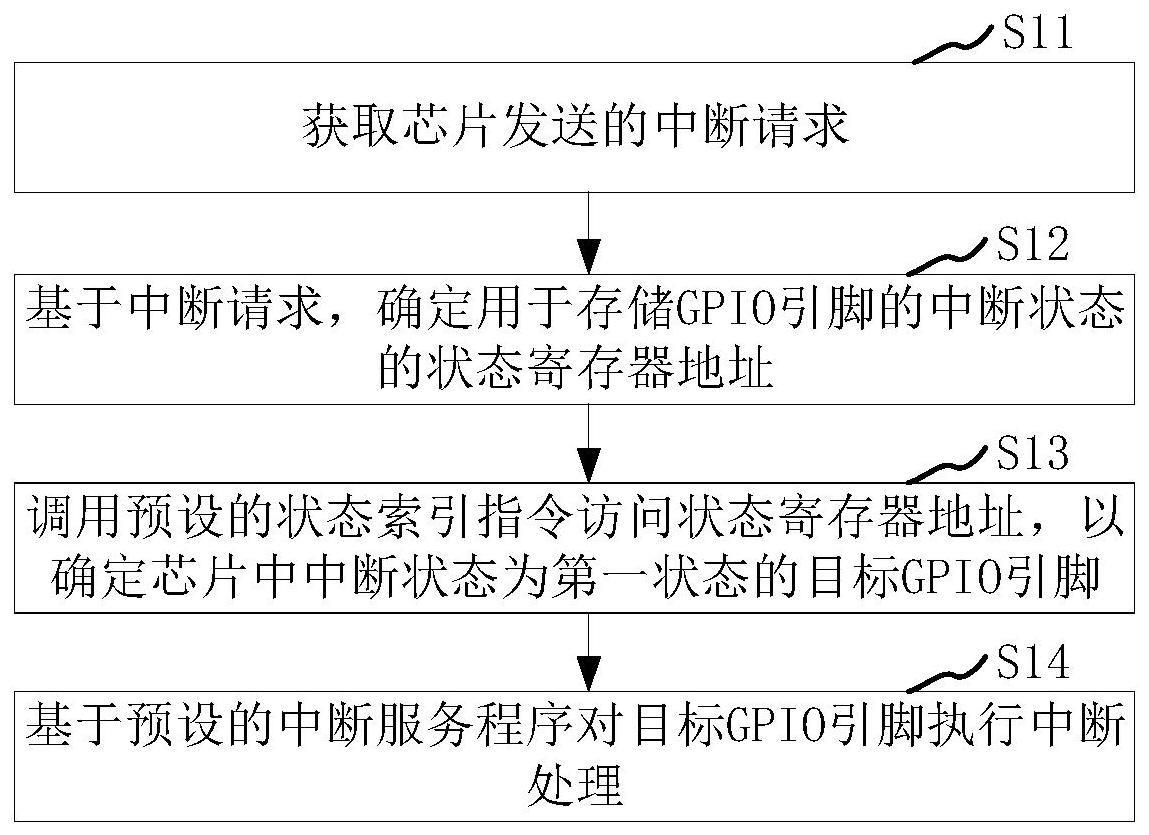

2、根据本公开实施例的第一方面,提供一种基于c-sky架构芯片降低gpio中断响应时间的方法,包括:

3、获取芯片发送的中断请求;所述芯片为基于c-sky架构开发的嵌入式芯片,所述中断请求用于指示对所述芯片中的gpio引脚执行中断处理,所述gpio引脚为所述芯片中的输入输出端口上设置的外部引脚;

4、基于所述中断请求,确定用于存储所述gpio引脚的中断状态的状态寄存器地址;所述中断状态包括用于表征所述gpio引脚处于中断响应的第一状态,所述状态寄存器地址为所述芯片中的状态寄存器的访问地址;

5、调用预设的状态索引指令访问所述状态寄存器地址,以确定所述芯片中所述中断状态为第一状态的目标gpio引脚;所述状态索引指令为单周期的查找指令,且所述状态索引指令用于降低所述gpio引脚的中断响应时间;

6、基于预设的中断服务程序对所述目标gpio引脚执行中断处理。

7、在一示例性实施例中,在所述状态寄存器中缓存有关于各个所述gpio引脚对应中断状态的状态值,且处于所述第一状态的gpio引脚的状态值为1;

8、所述调用预设的状态索引指令访问所述状态寄存器地址,以确定所述芯片中所述中断状态为第一状态的目标gpio引脚,包括:

9、调用预设的ff1指令访问所述状态寄存器地址,以在所述状态寄存器中,从引脚编号的最高位次向最低位次顺序查找所述状态值为1的gpio引脚;所述ff1指令为快速查找状态值1的指令,所述引脚编号为各所述gpio引脚之间唯一的数字编号;

10、响应于查找到第一个所述状态值为1的第一gpio引脚,将所述第一gpio引脚作为目标gpio引脚。

11、在一示例性实施例中,所述中断状态包括用于表征所述gpio引脚未处于中断响应的第二状态;在所述状态寄存器中缓存有关于各个所述gpio引脚对应中断状态的状态值,且处于所述第二状态的gpio引脚的状态值为0;

12、所述调用预设的状态索引指令访问所述状态寄存器地址,以确定所述芯片中所述中断状态为第一状态的目标gpio引脚,包括:

13、调用预设的ff0指令访问所述状态寄存器地址,以在所述状态寄存器中,从引脚编号的最高位次向最低位次顺序查找所述状态值为0的gpio引脚;所述ff0指令为快速查找状态值0的指令,所述引脚编号为各所述gpio引脚之间唯一的数字编号;

14、响应于查找到第一个所述状态值不为0的第二gpio引脚,将所述第二gpio引脚作为目标gpio引脚。

15、在一示例性实施例中,所述基于预设的中断服务程序对所述目标gpio引脚执行中断处理,包括:

16、确定对应于所述目标gpio引脚的引脚编号的目标中断服务程序;

17、调用所述目标中断服务程序基于所述引脚编号访问所述状态寄存器,以确定所述目标gpio引脚的中断类型,以及根据所述中断类型对进行中断处理。

18、在一示例性实施例中,所述基于所述中断请求,确定用于存储所述gpio引脚的中断状态的状态寄存器地址,包括:

19、对所述中断请求进行数据解析,以确定所述中断信号所在中断源的中断号;所述中断源表征所述中断信号发生的电路区域;

20、确定与所述中断号相绑定的输入输出端口的端口号;

21、确定与所述端口号相绑定的状态寄存器地址。

22、根据本公开实施例的第二方面,提供一种降低gpio中断响应时间的芯片,包括:检测电路、输入输出端口、中断控制器和处理器;所述输入输出端口上配置有多个gpio引脚;其中,

23、所述检测电路,用于在检测到存在gpio引脚的电平异常的情况下,生成中断信号,并将所述中断信号发送至所述中断控制器;

24、所述中断控制器,用于响应所述中断信号,以根据所述中断信号所在的中断源的中断号生成中断请求,并将所述中断请求发送给处理器;

25、所述处理器,用于响应所述中断请求,以在预存的中断向量表中查询与所述中断号相对应的中断向量,并基于所述中断向量调用对应于所述中断请求的中断处理程序以执行如上述所述的基于c-sky架构芯片降低gpio中断响应时间的方法;其中,所述中断向量为所述中断处理程序的调用地址。

26、在一示例性实施例中,所述检测电路,还用于对所述gpio引脚执行电平边沿检测或者电平翻转检测,以在检测到所述gpio引脚存在边沿跳变或者电平翻转的情况下,确定所述gpio引脚的电平异常;

27、其中,所述边沿跳变包括所述gpio引脚的电平发生上升沿跳变、下降沿跳变或者上升沿和下降沿同时跳变三种中的一种;

28、所述电平翻转包括所述gpio引脚的电平发生由低电平到高电平的翻转,或者由高电平到低电平的翻转。

29、根据本公开实施例的第三方面,提供一种基于c-sky架构芯片降低gpio中断响应时间的装置,包括:

30、请求获取单元,被配置为执行获取芯片发送的中断请求;所述芯片为基于c-sky架构开发的嵌入式芯片,所述中断请求用于指示对所述芯片中的gpio引脚执行中断处理,所述gpio引脚为所述芯片中的输入输出端口上设置的外部引脚;

31、地址确定单元,被配置为执行基于所述中断请求,确定用于存储所述gpio引脚的中断状态的状态寄存器地址;所述中断状态包括用于表征所述gpio引脚处于中断响应的第一状态,所述状态寄存器地址为所述芯片中的状态寄存器的访问地址;

32、引脚确定单元,被配置为执行调用预设的状态索引指令访问所述状态寄存器地址,以确定所述芯片中所述中断状态为第一状态的目标gpio引脚;所述状态索引指令为单周期的查找指令,且所述状态索引指令用于降低所述gpio引脚的中断响应时间;

33、中断处理单元,被配置为执行基于预设的中断服务程序对所述目标gpio引脚执行中断处理。

34、根据本公开实施例的第四方面,提供一种服务器,包括:

35、处理器;

36、用于存储所述处理器的可执行指令的存储器;

37、其中,所述处理器被配置为执行所述可执行指令,以实现如上述任一项所述的基于c-sky架构芯片降低gpio中断响应时间的方法。

38、根据本公开实施例的第五方面,提供一种计算机可读存储介质,所述计算机可读存储介质中包括计算机程序,当所述计算机程序由服务器的处理器执行时,使得所述服务器能够执行如上述任一项所述的基于c-sky架构芯片降低gpio中断响应时间的方法。

39、根据本公开实施例的第六方面,提供一种计算机程序产品,所述计算机程序产品中包括程序指令,所述程序指令被服务器的处理器执行时,使得所述服务器能够执行如上述任一项所述的基于c-sky架构芯片降低gpio中断响应时间的方法。

40、本公开的实施例提供的技术方案至少带来以下有益效果:

41、该方法先通过获取芯片发送的中断请求;其中,芯片为基于c-sky架构开发的嵌入式芯片,中断请求用于指示对芯片中的gpio引脚执行中断处理,gpio引脚为芯片中的输入输出端口上设置的外部引脚;基于中断请求,确定用于存储所述gpio引脚的中断状态的状态寄存器地址;所述中断状态包括用于表征所述gpio引脚处于中断响应的第一状态,所述状态寄存器地址为所述芯片中的状态寄存器的访问地址;调用预设的状态索引指令访问所述状态寄存器地址,以确定所述芯片中所述中断状态为第一状态的目标gpio引脚;所述状态索引指令为单周期的查找指令,且所述状态索引指令用于降低所述gpio引脚的中断响应时间;基于预设的中断服务程序对目标gpio引脚执行中断处理。这样,在一方面,先利用中断请求确定状态寄存器地址,再利用状态寄存器地址确定处于中断响应的目标gpio引脚,最后对目标gpio引脚执行中断处理,从而优化了对gpio引脚执行中断处理的流程,降低了人力和物力的消化;在另一方面,通过区别于现有技术中轮询状态寄存器的方式,调用预设的状态索引指令来访问状态寄存器,以确定处于中断响应的目标gpio引脚,能够有效缩短对异常引脚的索引时间,提升确定处于中断响应的目标gpio引脚的效率,进而减小了处理异常引脚的中断响应时间和提升对芯片应用的稳定性。

42、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

- 还没有人留言评论。精彩留言会获得点赞!