一种基于非易失性存储器的存内计算电路

本技术涉及电子电路领域,具体是一种基于非易失性存储器的存内计算电路。

背景技术:

1、在“后摩尔时代”,互补金属氧化物半导体(complementary metal oxidesemiconductor,简称cmos)器件的性能提升变得十分艰难。随着自动驾驶、物联网等新兴应用的发展,行业对计算系统性能提出了一系列新的要求。目前的计算平台主要基于冯诺依曼架构,即处理计算的逻辑单元与内存是分开的。在执行阶段,处理器根据指令通过总线从内存中获取数据,在完成计算后再将计算结果写回内存中。冯诺依曼架构将计算转换成程序指令的执行细节,简单易行地提高了数据处理的能力,提高了计算速度,奠定了现代计算机结构理论的基础。然而,随着数据量的指数增长,有限的数据带宽成为制约计算性能的重要因素。有限的数据带宽不仅增加了传输延迟,还会因数据在存储器和处理器之间频繁的移动导致大量的能量消耗。有限的带宽和较大的数据传输功耗形成了“冯诺依曼瓶颈”。在近几十年里,存储单元的存储速度只增长约10%,而处理单元的计算性能却高速增长60%。存储单元和处理单元存在一定的速度差异。当处理器的运算能力达到一定的程度时,由于访问存储器的速度无法跟上处理器对数据处理的速度,继续增加的处理器运算部件无法得到充分的利用,就形成了“存储墙问题”(memory wall)。

2、为解决上述问题,存内计算(in-memory computing,简称imc)平台被提出,即在内存阵列中执行逻辑运算的硬件设计。目前,各种存内计算架构都采用了成熟的内存技术,如sram(static random-access memory)和dram(dynamic random access memory)。基于sram的存内计算架构已经成功地展示了执行乘法和累积(multiply-and-accumulate,简称mac)操作的高效率,并且成功在神经网络计算中占据主导地位。然而,由于标准6晶体管sram的低密度限制了容量,导致基于sram的存内计算在大规模数据操作中的应用受到限制。基于dram的存内计算架构得益于更大的比特密度,可以避免上述缺点,但代价是其不断重复的刷新机制会增加能源消耗。

3、新兴的非易失性存储器(non-volatile memory,简称nvm)利用设备的固有物理特性来存储数据,这使得其位单元由一个晶体管和一个器件组成,即类似dram的高比特密度。非易失性存储器的非易失性可实现接近零泄漏和静态功耗,从而大大提高了性能。在不同的非易失性存储器中,自旋电子存储器提供了更高的读写操作速度,并已在汽车电子和可穿戴设备等领域实现了商业化。因此,它被认为最有希望成为下一代存储器。最近,基于磁随机存取存储器(magnetic random access memory,简称mram)的各种cim体系结构被提出。目前基于磁随机存取存储器的存内计算架构几乎都是数字存内计算方案,算法操作通过调度布尔逻辑来执行。虽然数字存内计算方案实现了高度并行和可靠的计算,但由于时序和控制更为复杂,其能源效率低于模拟存内计算方案(即基于交叉棒阵列欧姆定律的高度并行模拟乘法和累积操作)。mram不能应用模拟存内计算方案的主要原因是磁隧道结(magnetic tunnel junction,简称mtj)器件的隧道磁电阻比(tunnel magnetoresistanceratio,简称tmr)较低,这使得在传统交叉杆阵列中难以产生满足模拟计算需求的计算信号裕度。

4、具体地,现有技术提出了一个3晶体管2mtj(3t2mtj)的电路结构,参见图1所示。在传统的存内计算方案中,位单元既需要提供执行写/读操作的路径,也需要提供逻辑计算的路径。传统交叉阵列的计算路径采用标准位单元的读路径,避免了增加晶体管重建计算路径。但是,为了避免低tmr的影响,需要建立新的计算路径来对数组中的mtj进行拼接。参见图1所示,其提出了3t2mtj的存内计算单元结构,其中两个mtj存储的数据是互补的,例如,如果一个mtj存储'1',另一个mtj必须为'0'。当执行计算操作时,在操作位单元中连接字线(wl)的晶体管被关闭。同时,根据wll的输入打开与两个mtj直接相连的其中一个晶体管,与相邻位单元中的mtj形成串联路径进行计算。

5、但是,这种结构增加了写操作的难度。首先,为mtj执行写操作(iwrite)的电流需要流过三个晶体管。为了在相应的时间内(10ns内)完成写操作,它们的大小必须足够大,以确保通过mtj的电流是足够的(~80μa),这无疑会增加区域开销。其次,3t2mtj单元的写操作能量远大于1t1mtj单元,写操作也更加复杂。

技术实现思路

1、针对现有技术中的问题,本技术提供一种基于非易失性存储器的存内计算电路,能够高效地实现存内乘法累加计算,有效地降低存内逻辑运算的功耗与延迟,并提高了电路的面积效率。

2、为解决上述技术问题,本技术提供以下技术方案:

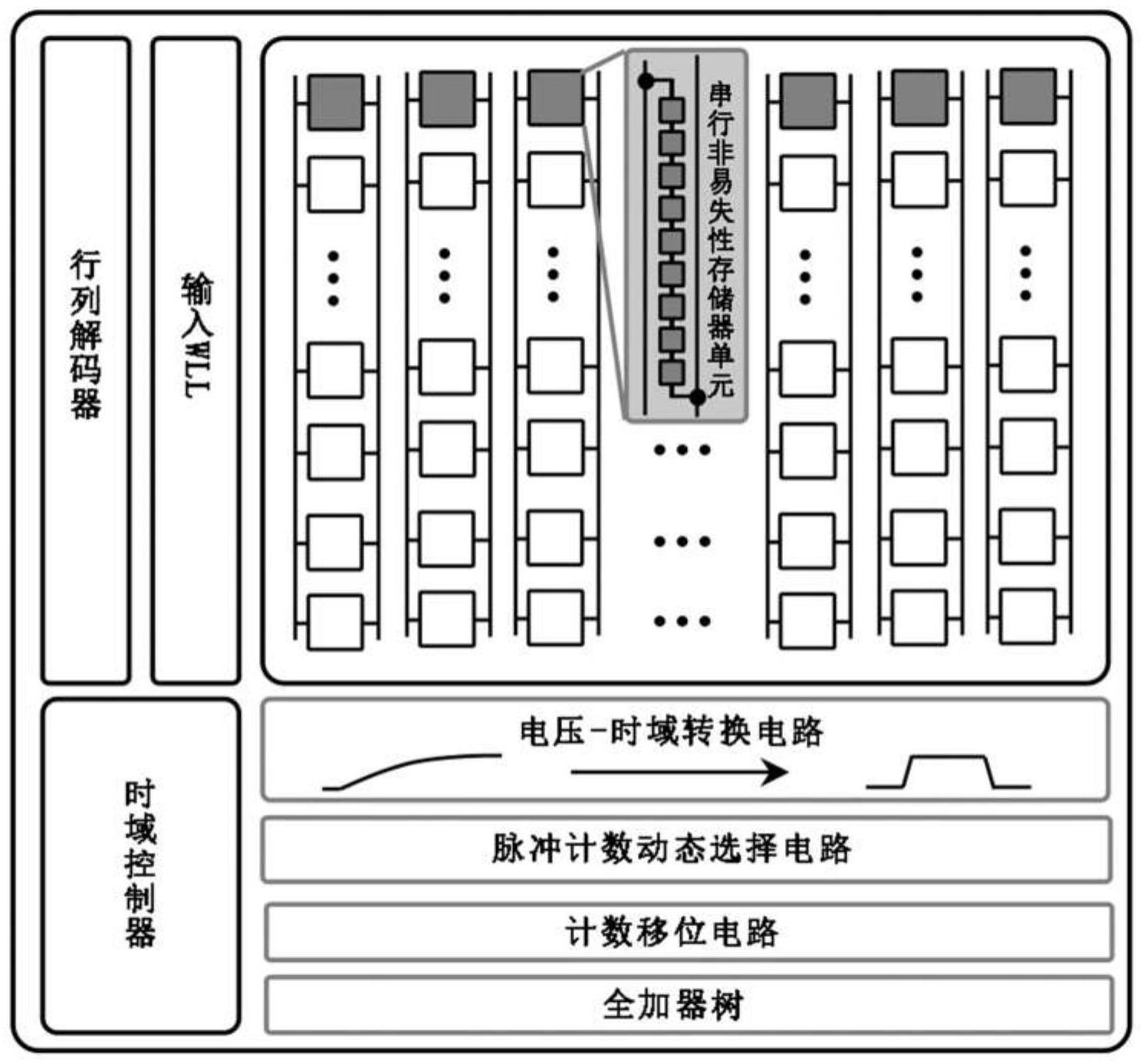

3、本技术提供一种基于非易失性存储器的存内计算电路,包括:非易失性存储器串联阵列、电压时域转换电路、脉冲计数动态选择电路、计数移位电路、全加器树及时域控制器;

4、其中,所述非易失性存储器串联阵列中的各存算列根据接收的输入信号,在所述时域控制器的控制下进行乘法累加运算生成电压升信号;其中,所述输入信号包括写输入信号与计算输入信号;

5、所述电压时域转换电路根据接收的电压升信号,在所述时域控制器的控制下进行电压时域转换生成时域信号;

6、所述脉冲计数动态选择电路根据接收的计算输入信号与时域信号,在所述时域控制器的控制下生成周期性方波信号;

7、所述计数移位电路根据接收的周期性方波信号,在所述时域控制器的控制下生成二进制乘法累加计算结果;

8、所述全加器树将各存算列对应的二进制乘法累加计算结果相加,得到存内计算输出结果。

9、进一步地,所述非易失性存储器串联阵列的各存算列包括多个串联的存内计算单元;所述各存算列均与电压总线相连。

10、进一步地,所述存内计算单元包括晶体管、传输门及磁隧道结;其中,所述传输门与所述磁隧道结并联后与所述晶体管串联。

11、进一步地,当所述计算输入信号为1信号时,所述传输门关闭,电流通过所述存内计算单元中的磁隧道结。

12、进一步地,当所述计算输入信号为0信号时,所述传输门打开,所述磁隧道结短路,电流不通过所述磁隧道结。

13、进一步地,当所述非易失性存储器串联阵列接收的是所述写输入信号时,所述写输入信号对应的电流仅通过所述晶体管与所述磁隧道结。

14、进一步地,所述脉冲计数动态选择电路包括依次串联的输入动态转换器、计数脉冲选择电路及自产生计数脉冲电路。

15、进一步地,所述计数移位电路包括多个串联的d边缘触发器。

16、进一步地,所述的基于非易失性存储器的存内计算电路,还包括行列解码器,用于根据接收的待计算数据生成对应的行列选择信号输出。

17、进一步地,所述的基于非易失性存储器的存内计算电路,还包括输入字线,用于将接收是行列选择信号转换为所述非易失性存储器串联阵列的输入信号。

18、针对现有技术中的问题,本技术提供的基于非易失性存储器的存内计算电路,能够高效地实现存内乘法累加计算,有效地降低存内逻辑运算的功耗与延迟,并提高了电路的面积效率。其中,存内计算单元中的两个晶体管组成的传输门可以将非易失存储器进行短路,实现全新的点积运算方式。基于非易失性存储器构建的全新的串联阵列结构,能够通过电阻求和的方式,实现乘法累加运算。基于触发器的计数移位电路,既可以进行计数操作,将带有乘法累加计算结果的脉冲信号转化为数字域信号,又可以将运算结果按照矩阵乘法进行权重移位。脉冲计数动态选择电路,能够根据输入中高电平的数量决定输出端口的信号输出。

- 还没有人留言评论。精彩留言会获得点赞!