一种电路验证方法、装置、电子设备及可读存储介质与流程

本发明涉及计算机,尤其涉及一种电路验证方法、装置、电子设备及可读存储介质。

背景技术:

1、随着计算机体系结构和硬件设计的复杂化,功能验证成为芯片开发中耗时的过程。验证工作占据了高达70%的开发周期。在验证环节中,其中一个瓶颈是寄存器转换级别(register-transfer level,rtl)电路的软件仿真。虽然软件仿真提供了完整的设计细节可见性以帮助调试,但对于复杂设计的长时间仿真而言,rtl仿真会非常耗时,这使得验证效率明显地降低。此外,软件仿真仍然依赖人工判断来检查波形和调试信息,以定位设计中的问题。

2、断言通常被用作一种高效的验证方法,以减轻数字电路功能验证中的调试工作量。超过75%的asic设计和近50%的fpga设计采用了基于断言的验证(assertion-basedverification, abv)。与传统的使用printf或display调试技术相比,abv可以同时执行自动监测和检查,以验证给定的硬件设计是否符合预期行为。一旦断言被违反,验证系统会自动标记问题。工程师们可以使用仿真软件调查断言失败的原因,并追溯到根本原因。在工业设计过程中,设计工程师通常添加断言以预防未来的意外行为,并识别潜在错误。断言在检查具有时序信息的复杂逻辑行为时非常有价值。

3、fpga作为硅前验证的标准方法和加速器,可以显著提升性能。然而,使用fpga调试rtl设计并不简单。目前供应商提供的调试工具如signaltap和ila,引入显著的面积开销,并且只能监视有限数量的内部信号。而且现有基于硬件对rtl进行测试的方案在指令集体系结构级别执行,缺乏设计细节的低级可见性,无法揭示设计内部错误和缺陷。断言适用于这个目的,但不幸的是,断言含有大量不可综合的关键字,不能直接用于硬件测试。

技术实现思路

1、本发明实施例提供一种电路验证方法、装置、电子设备及可读存储介质,可以解决fpga仿真缺乏设计细节,可见性低,以及软件仿真的验证效率低的问题。

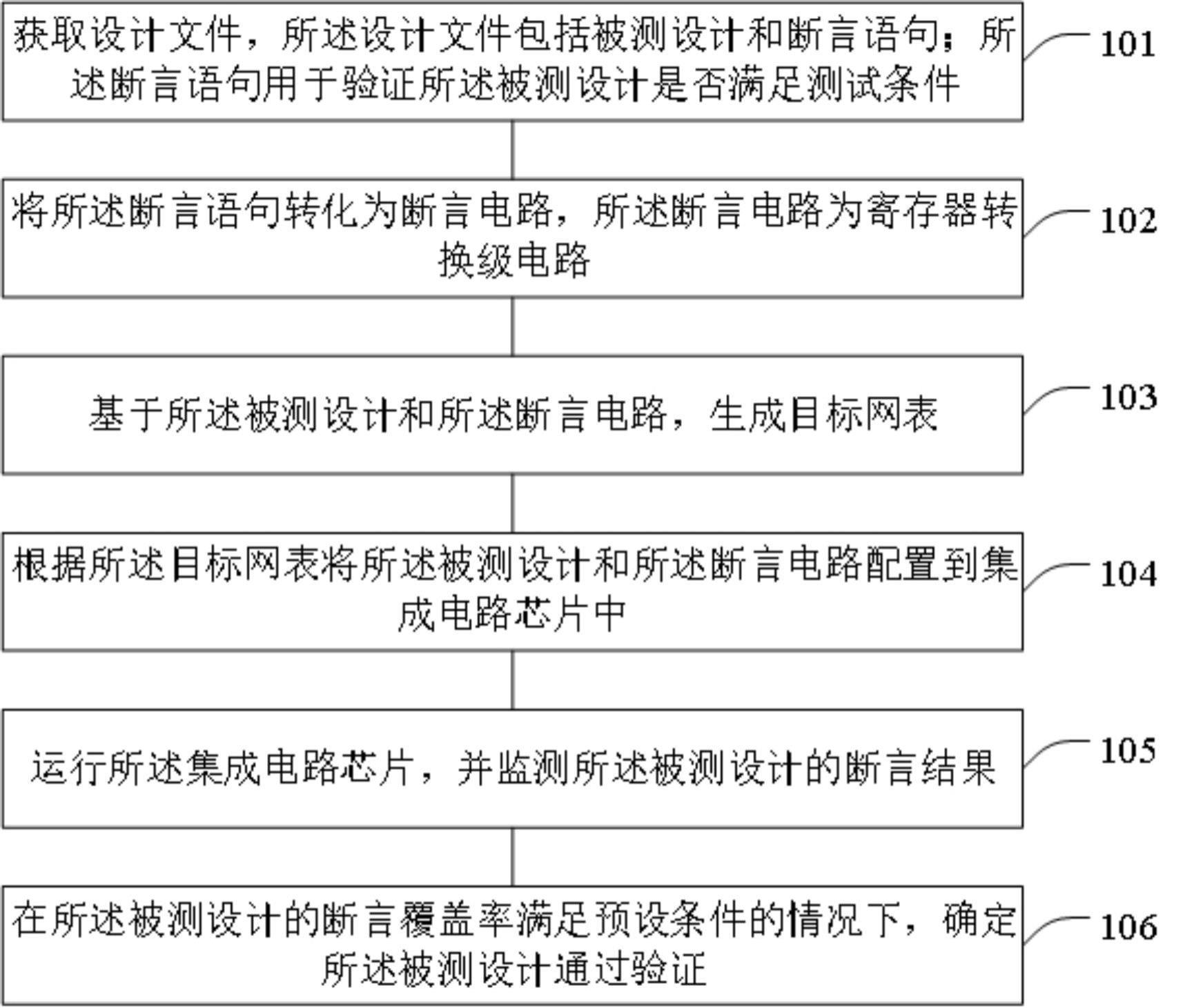

2、为了解决上述问题,本发明实施例公开了一种电路验证方法,所述方法包括:

3、获取设计文件,所述设计文件包括被测设计和断言语句;所述断言语句用于验证所述被测设计是否满足测试条件;

4、将所述断言语句转化为断言电路,所述断言电路为寄存器转换级电路;

5、基于所述被测设计和所述断言电路,生成目标网表;

6、根据所述目标网表将所述被测设计和所述断言电路配置到集成电路芯片中;

7、运行所述集成电路芯片,并监测所述被测设计的断言结果;

8、在所述被测设计的断言覆盖率满足预设条件的情况下,确定所述被测设计通过验证。

9、另一方面,本发明实施例公开了一种电路验证装置,所述装置包括:

10、文件获取模块,用于获取设计文件,所述设计文件包括被测设计和断言语句;所述断言语句用于验证所述被测设计是否满足测试条件;

11、断言转化模块,用于将所述断言语句转化为断言电路,所述断言电路为寄存器转换级电路;

12、网表生成模块,用于基于所述被测设计和所述断言电路,生成目标网表;

13、芯片配置模块,用于根据所述目标网表将所述被测设计和所述断言电路配置到集成电路芯片中;

14、断言监测模块,用于运行所述集成电路芯片,并监测所述被测设计的断言结果;

15、结果确定模块,用于在所述被测设计的断言覆盖率满足预设条件的情况下,确定所述被测设计通过验证。

16、再一方面,本发明实施例还公开了一种电子设备,所述电子设备包括处理器、存储器、通信接口和通信总线,所述处理器、所述存储器和所述通信接口通过所述通信总线完成相互间的通信;所述存储器用于存放可执行指令,所述可执行指令使所述处理器执行前述的电路验证方法。

17、本发明实施例还公开了一种可读存储介质,当所述可读存储介质中的指令由电子设备的处理器执行时,使得电子设备能够执行前述的电路验证方法。

18、本发明实施例包括以下优点:

19、本发明实施例提供了一种电路验证方法,将断言语句的转换为断言电路,该断言电路为可综合的寄存器转换级电路,可以直接用于硬件测试;根据断言电路和被测设计生成目标网表,进而根据目标网表将断言电路和被测设计配置到fpga中,利用断言电路来揭示被测设计内部状态和潜在问题,解决了fpga仿真缺乏设计细节的低级可见性的问题。并且,用硬件对被测设计进行调试加速,提升了被测设计的验证效率。

技术特征:

1.一种电路验证方法,其特征在于,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述将所述断言语句转化为断言电路,包括:

3.根据权利要求2所述的方法,其特征在于,所述对所述断言语句子树进行电路综合处理,得到断言电路,包括:

4.根据权利要求1所述的方法,其特征在于,所述基于所述被测设计和所述断言电路,生成目标网表,包括:

5.根据权利要求4所述的方法,其特征在于,所述基于所述信号连接信息、所述被测设计和所述断言电路,生成目标网表,包括:

6.根据权利要求1所述的方法,其特征在于,所述根据所述目标网表将所述被测设计和所述断言电路配置到集成电路芯片中,包括:

7.根据权利要求6所述的方法,其特征在于,所述集成电路芯片的静态区域中还配置有覆盖率监测器;所述运行所述集成电路芯片,并监测所述被测设计的断言结果,包括:

8.根据权利要求6所述的方法,其特征在于,所述方法还包括:

9.根据权利要求1所述的方法,其特征在于,在运行所述集成电路芯片,并监测所述被测设计的断言结果之后,所述方法还包括:

10.一种电路验证装置,其特征在于,所述装置包括:

11.根据权利要求10所述的装置,其特征在于,所述断言转化模块,包括:

12.根据权利要求11所述的装置,其特征在于,所述综合子模块,包括:

13.根据权利要求10所述的装置,其特征在于,所述网表生成模块,包括:

14.一种电子设备,其特征在于,所述电子设备包括处理器、存储器、通信接口和通信总线,所述处理器、所述存储器和所述通信接口通过所述通信总线完成相互间的通信;所述存储器用于存放可执行指令,所述可执行指令使所述处理器执行如权利要求1至9中任一项所述的电路验证方法。

15.一种可读存储介质,其特征在于,当所述可读存储介质中的指令由电子设备的处理器执行时,使得所述处理器能够执行如权利要求1至9中任一项所述的电路验证方法。

技术总结

本发明实施例提供一种电路验证方法、装置、电子设备及可读存储介质,该方法包括:获取设计文件,所述设计文件包括被测设计和断言语句;所述断言语句用于验证所述被测设计是否满足测试条件;将所述断言语句转化为断言电路,所述断言电路为寄存器转换级电路;基于所述被测设计和所述断言电路,生成目标网表;根据所述目标网表将所述被测设计和所述断言电路配置到集成电路芯片中;运行所述集成电路芯片,并监测所述被测设计的断言结果;在所述被测设计的断言覆盖率满足预设条件的情况下,确定所述被测设计通过验证。本发明实施例可以利用断言电路来揭示被测设计内部状态和潜在问题,解决了FPGA仿真缺乏设计细节的低级可见性的问题。

技术研发人员:石侃,翁伟杰,张子卿,蔡礼嘉,包云岗

受保护的技术使用者:北京开源芯片研究院

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!