一种裁剪单管仿真所需版图的方法与流程

本发明属于半导体设计和生产,具体涉及一种裁剪单管仿真所需版图的方法。

背景技术:

1、产品芯片由多种器件组成,器件的电学特性在一定程度上决定了芯片最终是否能够正常工作。在现有的半导体行业中,通常采用仿真模型模拟获取器件的仿真数据,以取代成本昂贵的硅片实验,通过仿真结果指导器件的实际生产,以降低器件开发成本、缩短开发周期以及提高成品率。

2、随着半导体设计工艺的不断发展,产品芯片上的器件集成度显著提高,对产品芯片完整版图的仿真运算量十分巨大,需要耗费过长的时间。如何在不影响仿真结果的前提下缩小仿真所需版图的尺寸以提高仿真速度,已成为半导体设计领域亟待解决的问题之一。

3、在仿真分析中,通常需要根据版图中一些标签层的label位置确定仿真激励施加端口,但由于对版图进行drc(design rule check,设计规则检查)时,人工版图调整可能导致某些标签层产生错误,进而导致通过这些标签层确定的激励端口存在错位的可能。

4、此外,在对完整版图进行一定的逻辑处理以得到仿真所需版图的过程中,可能存在某些特殊情况不适用采用的处理逻辑,导致获得的版图错误而不能用于后续仿真,如何对获得的版图进行查验,确保后续用于仿真的版图的正确性,也是半导体设计中缩短调试修正周期所面临的问题之一。

技术实现思路

1、鉴于以上所述现有技术的不足,本发明的目的在于:提供一种裁剪单管仿真所需版图的方法,对初始版图进行裁剪以缩小仿真所用版图尺寸,提高仿真速度。

2、为实现上述的全部或部分目的,本发明提供以下技术方案:

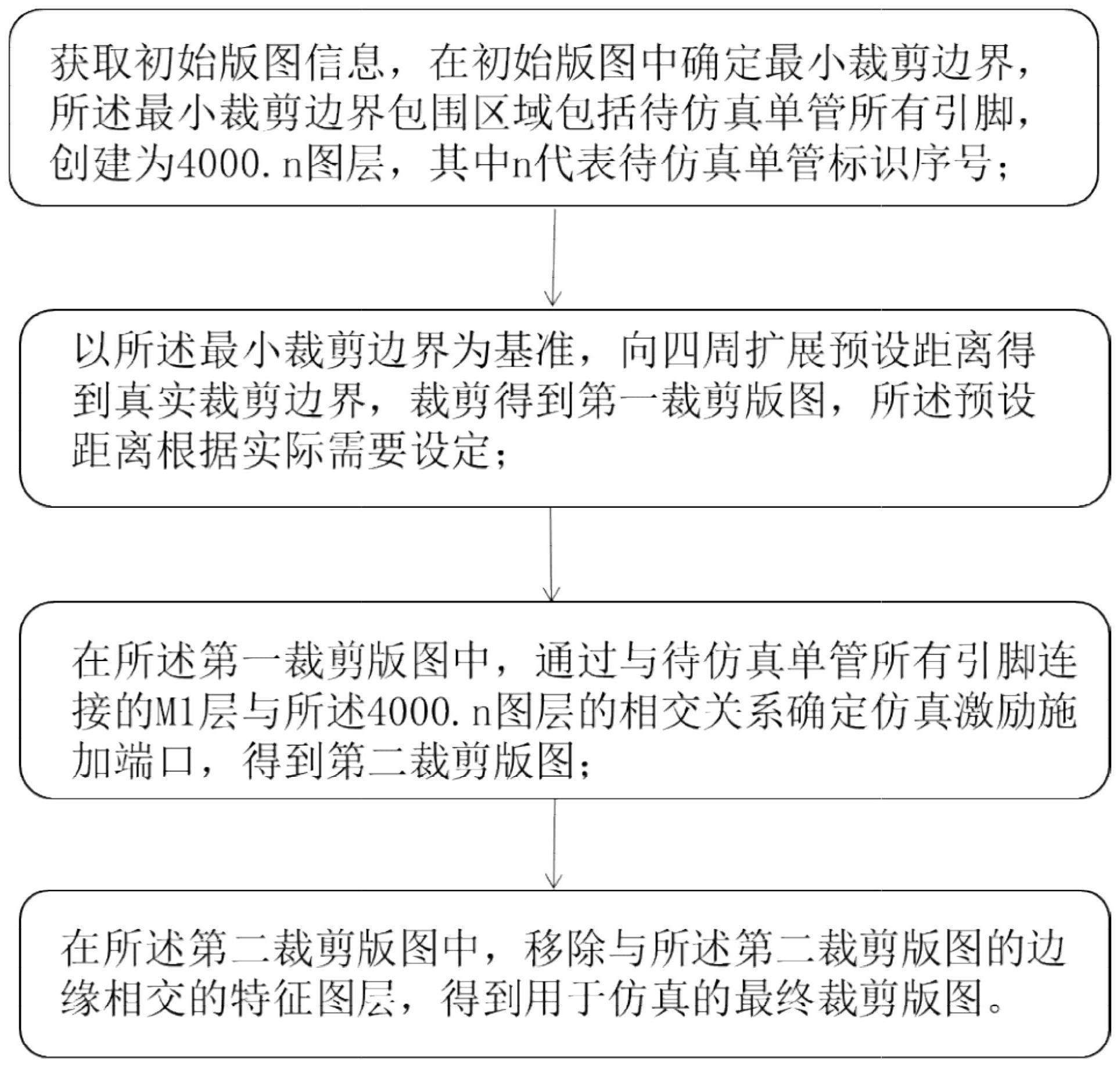

3、本发明提供一种裁剪单管仿真所需版图的方法,包括以下步骤:

4、获取初始版图信息,在初始版图中确定最小裁剪边界,所述最小裁剪边界包围区域包括待仿真单管所有引脚,创建为4000.n图层,其中n代表待仿真单管标识序号;

5、以所述最小裁剪边界为基准,向四周扩展预设距离得到真实裁剪边界,裁剪得到第一裁剪版图,所述预设距离根据实际需要设定;

6、在所述第一裁剪版图中,通过与待仿真单管所有引脚连接的m1层与所述4000.n图层的相交关系确定仿真激励施加端口,得到第二裁剪版图;

7、在所述第二裁剪版图中,移除与所述第二裁剪版图的边缘相交的特征图层,得到用于仿真的最终裁剪版图。

8、该技术方案的有益效果在于,对初始版图进行裁剪以缩小仿真所用版图尺寸,提高仿真速度;将上述步骤采用自动化方法实现,以针对初始版图中的每个待仿真单管都执行上述裁剪逻辑,提高处理效率和准确性。

9、所述确定最小裁剪边界的步骤包括:提取待仿真单管所有引脚的坐标信息;识别待仿真单管所有引脚坐标信息中的最小坐标(xmin,ymin)和最大坐标(xmax,ymax),以所述(xmin,ymin)、(xmax,ymax)作为相对顶点构成的矩形边界为所述最小裁剪边界。

10、所述初始版图包括m1_txt1层,所述m1_txt1层用于标注待仿真单管的引脚,所述m1_txt1层标签的命名包括待仿真单管的命名信息及其引脚命名信息。

11、所述提取待仿真单管所有引脚的坐标信息包括:提取初始版图中m1_txt1层标签的命名信息、与其对应的坐标信息,并存储于文档;遍历所有待仿真单管,在所述文档中查找待仿真单管及其引脚的命名信息,对应的坐标信息即为待仿真单管引脚的坐标信息;在所述坐标信息中,识别所述最小坐标(xmin,ymin)和最大坐标(xmax,ymax)。

12、所述初始版图包括m1_txt2层,所述m1_txt2层用于标注待仿真单管的引脚所连接的焊盘;

13、所述确定仿真激励施加端口的步骤包括:

14、在初始版图中,提取与m1_txt2层相交的m1层,在与栅极、漏极、源极、体极引脚相交的所述m1层上,分别创建m1_g层、m1_d层、m1_s层、m1_b层,得到metalmark.gds;

15、将所述metalmark.gds按照待仿真单管真实裁剪边界所对应的坐标进行裁剪,并将裁剪所得图形导入待仿真单管的第一裁剪版图中,分别在所述m1_g层、m1_d层、m1_s层和m1_b层与所述4000.n图层相交的多边形上确定仿真激励施加端口,得到第二裁剪版图;其中所述m1_g层、m1_d层、m1_s层和m1_b层与所述4000.n图层相交的多边形上确定仿真激励施加端口,例如所述m1_g层、m1_d层、m1_s层和m1_b层与所述4000.n图层相交的多边形上的任一顶点处添加代表栅极、漏极、源极和体极引脚的名称标签,即为所述仿真激励施加端口。

16、所述m1_txt1层的添加方法为在提取目标器件的源/漏/栅/体四端口对应的矩形m1时,会在对应矩形的中心位置添加所述m1_txt1层的label;

17、所述m1_txt2层的添加方法为在lvs验证前,在目标器件的源/漏/栅/体所连接的pad上方中心位置添加;其中上述操作的作用是用于lvs识别版图端口。

18、所述裁剪单管仿真所需版图的方法还包括:提取包含电性测试过程记录的列表,所述列表包括在测试过程中发生源极引脚和漏极引脚交换的器件信息;在所述列表中搜索待仿真单管,若所述列表中存在待仿真单管,则在所述第二裁剪版图中,将代表源极引脚和漏极引脚的名称标签进行交换;若所述列表中不存在待仿真单管,则不作处理。由于真实测试时产生源极引脚和漏极引脚交换,因此对仿真所需版图进行对应处理,以保证仿真数据准确性。

19、本发明中所述的“特征图层”是指:仿真文件根据所述特征图层识别待仿真器件类型。所述特征图层包括有源区图层(记为aa)、多晶硅图层(记为po)、有源区边界处多晶硅的标记层或有源区的有效区域图层。所述有源区的有效区域图层为aa的等效层,根据aa层按一定逻辑产生。若裁剪边界正好位于该特征图层处而导致裁剪版图中的特征图层形状被破坏,则可能导致待仿真单管类型识别错误,因此通过移除与裁剪边界相交的特征图层以避免类型识别出错。

20、在仿真文件通过有源区的有效区域图层识别待仿真单管类型的技术方案中,所述裁剪单管仿真所需版图的方法还包括在逻辑电路区域添加有源区的有效区域图层。

21、在仿真文件通过有源区的有效区域图层识别待仿真单管类型的技术方案中,还可以包括,在所述第二裁剪版图中,移除静态随机存储区域的有源区的有效区域图层,使仿真对象仅限于逻辑电路区域,以减小仿真运算量,缩短仿真时间。

22、所述裁剪单管仿真所需版图的方法还包括对所述最终裁剪版图进行校验检查的步骤:提取所述最终裁剪版图对应的网表文件,查验所述网表文件是否正确,以判断对应的最终裁剪版图是否可用于后续仿真。

23、所述查验所述网表文件的步骤包括:

24、s1:将网表文件的每一行定义为数组,d、g、s、b元素为所述数组的基本组成单元,其中d代表漏极,g代表栅极,s代表源极,b代表体极;

25、s2:定义统计变量$port_mark、$device_mark、$stacks_mark、$stackd_mark、$port_bsd_mark、$device_bsd_mark、$bad_mark,并设定所述统计变量的初始值为0;

26、s3:遍历所述网表文件的每一个数组,根据d、g、s、b元素在数组中的组成,执行以下操作:

27、若端口声明所在行对应数组同时包括d、g、s、b,则令$port_mark变量数值加1;

28、若端口声明所在行对应数组中包括g,且包括d、b、s中的任意两个,则令$port_bsd_mark变量数值加1;

29、若待仿真单管声明所在行对应数组同时包括d、g、s、b,则令$device_mark变量数值加1;

30、若待仿真单管声明所在行对应数组中第1-4个元素分别为(s||d)、g、!(s||d)、b元素,则令$stacks_mark变量数值加1;

31、若待仿真单管声明所在行对应数组中第1-4个元素分别为!(s||d)、g、(s||d)、b元素,则令$stackd_mark变量数值加1;

32、若待仿真单管声明所在行对应数组中第1-4个元素分别为组合(b、g、d、b)、(s、g、d、s)、(s、g、d、d)、(s、g、b、b)、(d、g、s、s)、(d、g、s、d)、(b、g、s、b)、(d、g、b、b)的其中之一,则令$device_bsd_mark变量数值加1;

33、若网表文件的任意行中存在“bad”字符,则令$bad_mark变量数值加1;

34、s4:根据所述统计变量的数值,判断是否存在以下情况:

35、a:同时满足:$port_mark=1、$device_mark≥1、$bad_mark≠0;

36、b:同时满足:$port_mark=1、$stacks_mark≥1、stackd_mark≥1、$bad_mark≠0;

37、c:同时满足:$port_bsd_mark=1、$device_bsd_mark≥1;

38、若符合上述三种情况之一,则网表正确,对应最终裁剪版图可用于后续仿真;若不符合,则网表错误,对应最终裁剪版图不能用于后续仿真。

39、与现有技术相比,本发明至少具有以下有益效果:

40、提供一种裁剪单管仿真所需版图的方法,对初始版图进行裁剪以缩小仿真所用版图尺寸,提高仿真速度;将上述步骤采用自动化方法实现,以针对初始版图中的每个待仿真单管都执行上述裁剪逻辑,提高处理效率和准确性;

41、通过与待仿真单管所有引脚连接的m1层与最小裁剪边界所包围图形的相交关系确定仿真激励施加端口,并根据真实测试中源极引脚和漏极引脚交换情况,对裁剪版图中端口的名称标签进行相应调整,确保仿真激励施加端口的准确性;

42、查验最终裁剪版图所对应的网表文件,根据网表文件的正确性确保该最终裁剪版图可用于后续仿真,以缩短调试修正周期。

- 还没有人留言评论。精彩留言会获得点赞!