内置式可重构协处理器的计算芯片的制作方法

本发明涉及计算机芯片,具体为内置式可重构协处理器的计算芯片。

背景技术:

1、芯片,准确地说就是硅片,也叫集成电路,它是微电子技术的主要产品,计算机芯片是一种用硅材料制成的薄片,其大小仅有手指甲的一半,一个芯片是由几百个微电路连接在一起的,体积很小,在芯片上布满了产生脉冲电流的微电路。计算机芯片利用这些微电流,就能够完成控制计算机、自动化装置制和其它各种设备所需要的操作。计算机芯片内的电路很小,它使用的电流也很小,所以也称芯片为微电子器件,微型计算机中的主要芯片有微处理芯片、接口芯片和存储器芯片;

2、在大众已经习惯的计算模式中,处理器(cpu)和专用集成电路(asic)一直是计算机芯片的两大主流,其中,处理器计算模式的特点在于它们都具有各自的指令集,通过执行指令集中的相关指令来完成计算,改写软件指令就能改变系统实现的功能,而不用去改动底层的硬件环境;专用集成电路是针对某一特定应用专门设计的硬件电路;专用集成电路计算模式的特点在于用硬件来实现应用的操作,因为针对特定应用设计,所以在执行相应应用时具有很高的速度、效率和精度。

3、但是现有技术在实际使用时,伴随着应用领域特别是嵌入式环境对系统的性能、能耗、上市时间等指标需求的不断提高,通常的处理器在使用过程中必须从存储器中读取每条指令,将其译码后再执行,因而每个独立的操作具有更高的执行开销。另外,处理器的指令集是由处理器自身体系结构决定的,没有用专门指令实现的操作只能使用已有的指令组合来处理,从而增加了执行的开销;同时,通常的集成电路在使用过程中,开发周期太长,代价太高。而且硬件电路一旦制作好以后是不能够被随意改动的。这就意味着如果功能的需求发生了变化,就需要重新设计和重新加工新的专用集成电路芯片。哪怕只是芯片上的很小一部分线路需要修改,也要重新制作整个芯片。如果针对各种不同的应用都专门设计专用的电路芯片,就会带来高昂的成本;

4、由此可见,现有的主流计算模式中存在的主要问题是:处理器方式能够灵活地实现各种应用,但却在性能上有缺陷;而硬件逻辑实现性能虽然高,但灵活性却很差。

技术实现思路

1、本发明的目的在于提供内置式可重构协处理器的计算芯片,以解决上述背景技术中提出的现有的主流计算模式中存在的主要问题是:处理器方式能够灵活地实现各种应用,但却在性能上有缺陷;而硬件逻辑实现性能虽然高,但灵活性却很差的问题。

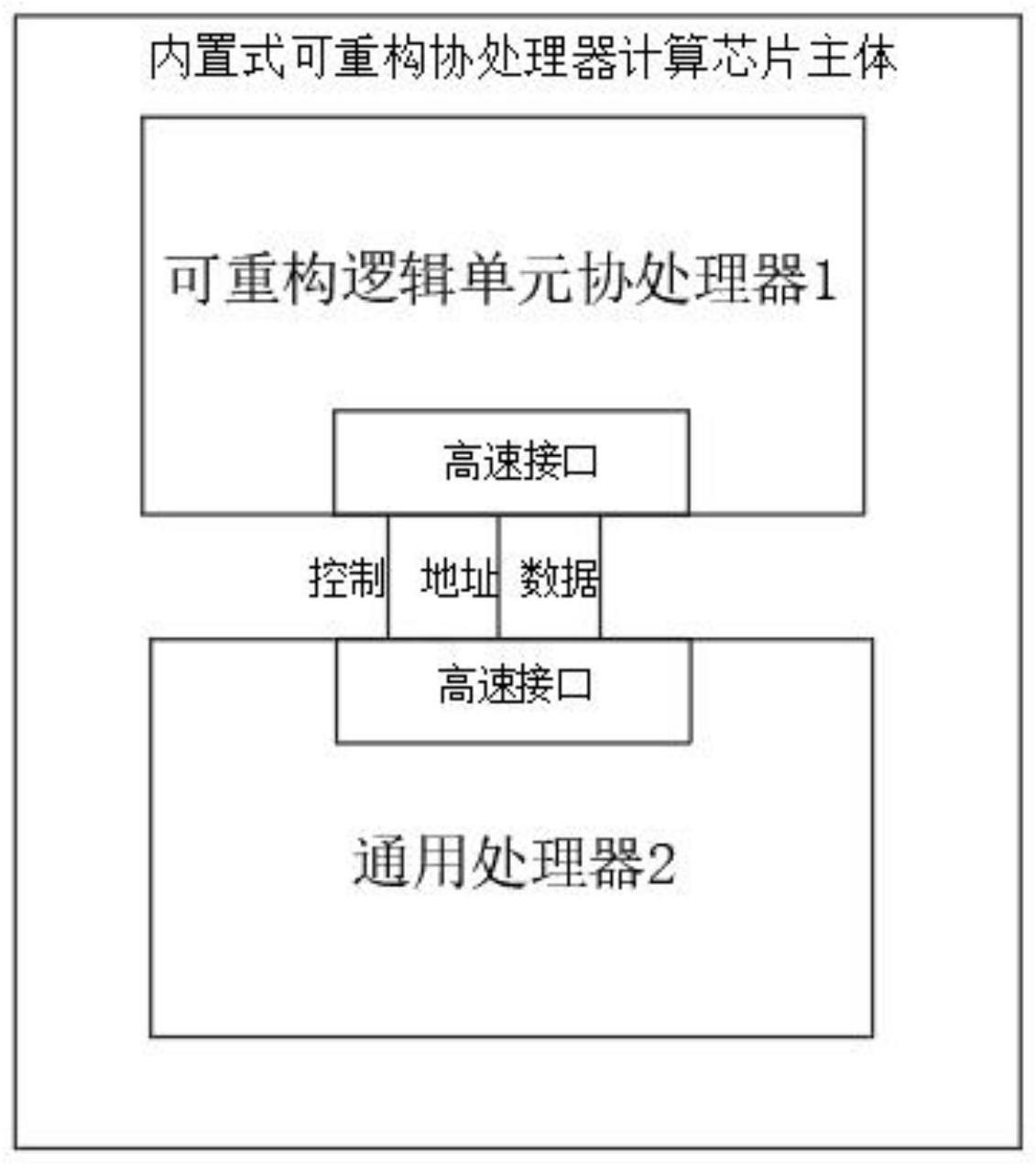

2、为实现上述目的,本发明提供如下技术方案:包括通用处理器和可重构逻辑单元协处理器;

3、所述可重构逻辑单元协处理器与通用处理器耦合集成为内置式可重构协处理器计算芯片主体,且可重构逻辑单元协处理器作为一个独立的协处理器通过高速接口与所述通用处理器进行通讯,使得可重构逻辑单元协处理器与通用处理器之间形成高速的数据传输和协同计算;

4、所述可重构逻辑单元协处理器包括可重构逻辑单元、数据存储单元、控制单元和输入输出接口,使得通过所述可重构逻辑单元协处理器负责控制整个内置式可重构协处理器计算芯片主体的初始化配置、硬件重新配置、并行计算和数据交换和重复执行的工作流程。

5、优选的,所述可重构逻辑单元协处理器由fpga芯片基础定制构件。

6、优选的,所述高速接口由pcie接口构件,所述内置式可重构协处理器计算芯片主体通过专用通信接口与其他外部设备进行通信,所述外部设备包括存储器和图形处理器,使得所述内置式可重构协处理器计算芯片主体与外部设备进行高速数据交换。

7、优选的,所述初始化配置包括通用处理器向可重构逻辑单元协处理器向发送配置信息,所述配置信息包括任务要求和硬件结构;所述硬件重新配包括根据配置信息,控制单元会根据特定的算法将可重构逻辑单元中的逻辑门阵列、查找表、算术逻辑单元等重新组织形成特定的硬件结构;所述并行计算包括内置式可重构协处理器计算芯片主体的计算任务分解为多个小任务,可重构逻辑单元协处理器通过并行计算来加速计算过程,每个小任务都会被分配到可重构逻辑单元的不同部分进行处理;所述数据交换包括计算过程中的数据和结果通过输入输出接口与通用处理器进行交换,完成整个计算任务;所述重复执行包括在需要的情况下,通用处理器可以重新发送配置信息,以更改可重构逻辑单元的硬件结构,从而适应新的计算要求。

8、优选的,所述可重构逻辑单元包括采用可编程逻辑门阵列(pla)、可编程查找表(lut)、和可编程算术逻辑单元(alu),使得所述可重构逻辑单元协处理器在逻辑门级别上实现计算任务的硬件加速。

9、优选的,所述数据存储单元包括采用集成更大容量的寄存器文件和高速缓存,使得所述可重构逻辑单元协处理器提供更高的数据处理能力。

10、优选的,所述控制单元包括采用更高效的配置算法,使得所述可重构逻辑单元协处理器允许更快速地重构硬件结构。

11、优选的,所述输入输出接口包括采用更快的总线技术或者专用的高速通信接口,使得所述可重构逻辑单元协处理器支持更高速的数据交换。

12、优选的,所述可重构逻辑单元协处理器的可重构逻辑单元、数据存储单元和控制单元负责控制整个内置式可重构协处理器计算芯片主体负责实际执行计算任务的硬件加速。

13、与现有技术相比,本发明的有益效果是:

14、1、本发明采用更灵活的可重构逻辑单元结构,能够更好地适应不同的计算任务,提供更高的性能和能效;

15、2、本发明还集成更大容量和更高速的数据存储单元,同时采用更快速的输入输出接口,能够更快地传输和处理数据;

16、3、本发明同时还具备动态优化能力,可以根据实际计算情况和负载变化,实时调整硬件结构,以获得更高的性能和能效。

技术特征:

1.内置式可重构协处理器的计算芯片,包括通用处理器(1),其特征在于:包括可重构逻辑单元协处理器(2);

2.根据权利要求1所述的内置式可重构协处理器的计算芯片,其特征在于:所述可重构逻辑单元协处理器(2)由fpga芯片基础定制构件。

3.根据权利要求2所述的内置式可重构协处理器的计算芯片,其特征在于:所述高速接口由pcie接口构件,所述内置式可重构协处理器计算芯片主体通过专用通信接口与其他外部设备进行通信,所述外部设备包括存储器和图形处理器,使得所述内置式可重构协处理器计算芯片主体与外部设备进行高速数据交换。

4.根据权利要求3所述的内置式可重构协处理器的计算芯片,其特征在于:所述初始化配置包括通用处理器(1)向可重构逻辑单元协处理器(2)向发送配置信息,所述配置信息包括任务要求和硬件结构;所述硬件重新配包括根据配置信息,控制单元会根据特定的算法将可重构逻辑单元中的逻辑门阵列、查找表、算术逻辑单元等重新组织形成特定的硬件结构;所述并行计算包括内置式可重构协处理器计算芯片主体的计算任务分解为多个小任务,可重构逻辑单元协处理器(2)通过并行计算来加速计算过程,每个小任务都会被分配到可重构逻辑单元的不同部分进行处理;所述数据交换包括计算过程中的数据和结果通过输入输出接口与通用处理器(1)进行交换,完成整个计算任务;所述重复执行包括在需要的情况下,通用处理器可以重新发送配置信息,以更改可重构逻辑单元的硬件结构,从而适应新的计算要求。

5.根据权利要求4所述的内置式可重构协处理器的计算芯片,其特征在于:所述可重构逻辑单元包括采用可编程逻辑门阵列(pla)、可编程查找表(lut)、和可编程算术逻辑单元(alu),使得所述可重构逻辑单元协处理器(2)在逻辑门级别上实现计算任务的硬件加速。

6.根据权利要求5所述的内置式可重构协处理器的计算芯片,其特征在于:所述数据存储单元包括采用集成更大容量的寄存器文件和高速缓存,使得所述可重构逻辑单元协处理器(2)提供更高的数据处理能力。

7.根据权利要求6所述的内置式可重构协处理器的计算芯片,其特征在于:所述控制单元包括采用更高效的配置算法,使得所述可重构逻辑单元协处理器(2)允许更快速地重构硬件结构。

8.根据权利要求7所述的内置式可重构协处理器的计算芯片,其特征在于:所述输入输出接口包括采用更快的总线技术或者专用的高速通信接口,使得所述可重构逻辑单元协处理器(2)支持更高速的数据交换。

9.根据权利要求8所述的内置式可重构协处理器的计算芯片,其特征在于:所述可重构逻辑单元协处理器(2)的可重构逻辑单元、数据存储单元和控制单元负责控制整个内置式可重构协处理器计算芯片主体负责实际执行计算任务的硬件加速。

技术总结

本发明公开了内置式可重构协处理器的计算芯片,包括通用处理器和可重构逻辑单元协处理器;所述可重构逻辑单元协处理器与通用处理器耦合集成为内置式可重构协处理器计算芯片主体,且可重构逻辑单元协处理器作为一个独立的协处理器通过高速接口与所述通用处理器进行通讯,使得可重构逻辑单元协处理器与通用处理器之间形成高速的数据传输和协同计算;所述可重构逻辑单元协处理器包括可重构逻辑单元、数据存储单元、控制单元和输入输出接口。本发明实现了整个内置式可重构协处理器计算芯片主体具有更灵活的硬件结构、更高速的数据处理和更好的动态优化能力,能够提供更高的计算加速性能和能效,适用于广泛的计算任务和应用场景。

技术研发人员:王冠清,陈清甫

受保护的技术使用者:无锡天璇技术有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!