一种基于大容量非易失存储的多任务智能处理器

本发明属于智能处理器领域,具体涉及一种基于大容量非易失存储的多任务智能处理器。

背景技术:

1、目前,基于新型存储介质的非易失存储器已逐步应用到处理器中,并取得了较好的效果。相较于传统的静态随机存储器(sram),新型非易失存储器具有存储密度高、静态功耗低、可实现更大的片上存储容量、掉电不丢失数据等特性,满足对实时性要求高的应用。相较于传统的flash存储器,新型非易失存储器具有更快的读写速度和更长的耐久性,可以替代flash存储器作为嵌入式存储器使用,提升处理器的读写带宽及存储的使用寿命。

2、现有处理器中的新型非易失存储器,主要用于缓解片内sram和片外flash数据访存带来的存储墙和功耗墙问题。在新型的非易失存储器中,自旋转移矩存储器(stt-ram)和电阻式存储器(reram)技术具有替代sram和flash的潜力,利用其非易失特性,极大缓解了传统主流片上存储sram导致的高静态功耗和低密度的问题。与flash相比,其具有更低的编程电压、更快的读写速度和长耐久性,且与cmos技术兼容,易于制造。然而,受工艺和自身结构限制,现有的大容量非易失存储器良率低,规模量产的非易失存储器存在存储容量偏小、耐久性不足、稳定性较差等问题,无法满足日益增加的存储需求及实际应用的需求,进而影响处理器的性能。此外,现有的智能算法在取得更好应用效果的同时,其网络规模随之攀升。在提升硬件计算能力的同时,其数据安全性和存储容量需求也限制智能处理器性能。

技术实现思路

1、本发明的目的在于:提供一种基于大容量非易失存储的多任务智能处理器,从存储容量、耐久性、稳定性等多方面提升处理器性能,使其更好的满足应用需求。

2、为实现上述目的,本发明采用如下技术方案:

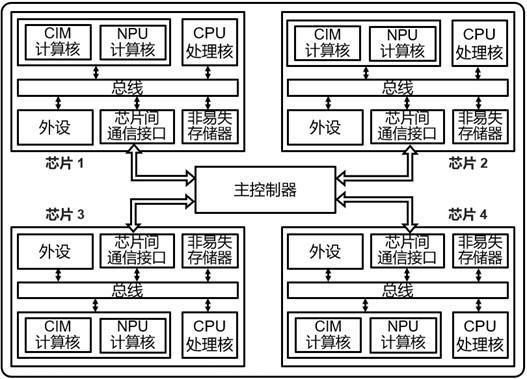

3、一种基于大容量非易失存储的多任务智能处理器,包括n个芯片电路和1个任务主控制器,芯片电路与任务主控制器互连;

4、所述任务主控制器用于将任务指令分配至各芯片电路;

5、所述芯片电路用于执行任务主控制器下发的任务指令,并将执行结果返回至任务主控制器;

6、芯片电路包括cpu处理核、外设电路模块、混合计算模块、非易失存储模块、通信模块;

7、所述cpu处理核用于接收任务主控制器下发的任务指令,根据任务指令生成控制各模块的控制指令;

8、所述外设电路模块响应控制指令接收外部输入的原始数据和权重,并存储到非易失存储模块;

9、所述混合计算模块响应控制指令从非易失存储模块中获取原始数据和权重,并执行计算操作,将计算结果存储至非易失存储模块;

10、所述通信模块用于实现cpu处理核与任务主控制器的通信。

11、进一步的,所述混合计算模块包括cim计算核和npu计算核; cim计算核采用存内计算方法,完成粗粒度计算;npu计算核采用传统cmos计算方法完成细粒度推理计算,计算方式根据计算需求选择。

12、进一步的,所述非易失存储模块包括存储器、内自建测试电路、修复电路、纠错电路、容错电路和第一存储控制器;

13、所述存储器包括非易失存储阵列和损耗均衡电路,非易失存储阵列包括第二存储控制器和存储介质;第二存储控制器用于将读写命令转化为对存储介质的具体读写操作,以使存储介质的完成读写操作;损耗均衡电路通过损耗均衡算法,动态改变非易失存储阵列中读写数据的逻辑地址和物理地址的映射关系,实现存储器的均衡访问;所述逻辑地址是指外部输入数据希望访问的地址,物理地址是指在非易失存储阵列中的实际存储地址;

14、所述内自建测试电路,用于对非易失存储阵列中所有读写数据的地址进行读写测试,以验证每一个存储地址空间的读写功能的正常与否;并将异常的存储地址空间发送至修复电路;

15、所述修复电路,通过冗余行或冗余列对读写异常的存储地址空间进行替换修复;

16、所述容错电路根据预设容错规则,实时监测外部逻辑对非易失存储器的访问状态,并将监测到的异常情况反馈至第一存储控制器,其异常情况是指对存储器的恶意访问;

17、所述第一存储控制器根据预设规则,控制均衡电路、内自建测试电路、修复电路进行相应处理,对容错电路反馈的异常情况进行处理。其预设规则包括通过jtag接口,通过第一存储控制器控制内自建测试电路,以实现出厂检测;对整个存储器进行全地址域读写检查,若有错,则使用修复电路通过冗余行或冗余列进行替换;正常使用时,第一存储控制器启动容错电路检测存储写入情况;若检测到恶意地址攻击,将其传达给第一存储器控制器,同时暂时禁止访问直到恶意地址攻击消失。

18、进一步的,所述非易失存储模块还可以设为级联结构,级联结构是由多个非易失存储模块和一个非易失存储主控制器组成;每个非易失存储模块分别与非易失存储主控制器互连。

19、进一步的,所述n≥1,当n>1时,各芯片电路之间根据需求选择串行或并行方式实现级联。

20、本发明的多任务智能处理器为嵌入式设计,通过任务主控制器对各芯片电路进行控制,减少了片外数据访存,降低系统功耗,缓解了存储墙问题。使用时,根据需求选择芯片电路数量和级联方式,通过芯片级联,实现不同规模的算力和存储需求的智能处理器,确保智能算法安全高效运行。配合内自建测试电路、修复电路以及容错电路,解决了现有基于新型非易失存储器的处理器存在的耐久性不足、稳定性差等问题,有效提升了新型非易失存储器综合性能,更好的满足应用需求。

技术特征:

1.一种基于大容量非易失存储的多任务智能处理器,包括至少1个芯片电路、1个任务主控制器,芯片电路与任务主控制器互连,其特征在于:

2.根据权利要求1所述的一种基于大容量非易失存储的多任务智能处理器,其特征在于:所述混合计算模块包括cim计算核和np u计算核;其中,cim计算核采用存内计算方法,进行粗粒度计算;npu计算核采用传统cmos计算方法,进行细粒度推理计算,计算方式根据计算指令选择。

3.根据权利要求1所述的一种基于大容量非易失存储的多任务智能处理器,其特征在于:所述非易失存储模块包括存储器、内自建测试电路、修复电路、纠错电路以及容错电路以及第一存储控制器;

4.根据权利要求1所述的一种基于大容量非易失存储的多任务智能处理器,其特征在于:所述非易失存储模块还可以设为级联结构,级联结构是由多个非易失存储模块和一个非易失存储主控制器组成;每个非易失存储模块分别与非易失存储主控制器互连。

5.根据权利要求1至4任一项所述的一种基于大容量非易失存储的多任务智能处理器,其特征在于:当芯片电路的个数≥2时,各芯片电路之间根据需求选择串行或者并行实现级联。

技术总结

本发明属于智能处理器领域,具体涉及一种基于大容量非易失存储的多任务智能处理器。该处理器包括芯片电路和任务主控制器,芯片电路与任务主控制器互连;任务主控制器用于将任务指令分配至各芯片电路;芯片电路用于执行任务主控制器下发的任务指令,并将执行结果返回至任务主控制器;芯片电路包括CPU处理核、外设电路模块、混合计算模块、非易失存储模块、通信模块;非易失存储模块存储器由内自建测试电路、修复电路、纠错电路、容错电路和第一存储控制器组成。通过任务主控制器对各芯片电路进行控制,缓解了存储墙问题,通过在第一存储控制器内增设自建测试电路、修复电路以及容错电路,实现耐久性、稳定性的提升。

技术研发人员:常亮,赵鑫,郭子龙,周菁

受保护的技术使用者:电子科技大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!