SPI的主设备读取从设备中数据的控制方法及设备与流程

本申请涉及智能客服,尤其涉及一种spi的主设备读取从设备中数据的控制方法及设备。

背景技术:

1、spi(serial peripheral interface)传输通常会使用给定字长的两个移位寄存器,一个在主设备中,一个在从设备中,这两个寄存器连接成一个虚拟的环形缓冲器。由主设备提供sclk(simplifiedclock)管脚,为从设备提供时钟信号。

2、其中,主设备在时钟信号的后沿从数据总线接受从设备发出的数据位,但如果从设备没有及时将数据传输到数据总线,会导致主设备在时钟信号的每个后沿采样到无效数据,由此增加主设备上的数据处理流程。

3、因此,亟需一种能够对主设备读取从设备中的数据的控制方便,避免主设备采样到过多的无效数据。

技术实现思路

1、有鉴于此,本申请提供一种spi的主设备读取从设备中数据的控制方法及设备,用以解决现有技术中主设备采样到过多无效数据的技术缺陷,如下:

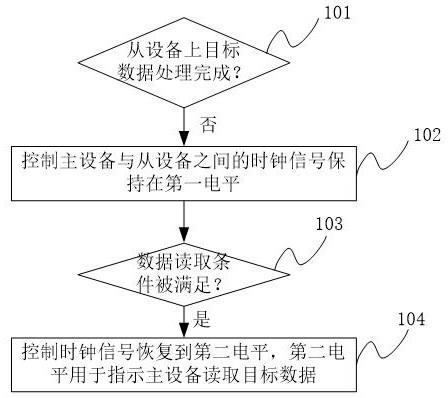

2、一种spi的主设备读取从设备中数据的控制方法,应用于所述从设备,所述方法包括:

3、监测所述从设备上目标数据是否处理完成;

4、在所述目标数据处理未完成的情况下,控制所述主设备与所述从设备之间的时钟信号保持在第一电平;

5、在数据读取条件被满足的情况下,控制所述时钟信号恢复到第二电平,所述第二电平用于指示所述主设备读取所述目标数据。

6、上述方法,优选的,所述数据读取条件,包括以下任意一项:

7、所述目标数据被全部写入所述主设备与所述从设备之间的数据读取总线上,所述第二电平用于指示所述主设备从所述数据读取总线上读取所述目标数据;

8、或,

9、所述时钟信号保持在所述第一电平的持续时长达到预设的目标时长,所述目标时长包含至少一个所述时钟信号的时钟周期。

10、上述方法,优选的,所述从设备中设置有单稳态触发器,所述单稳态触发器与mos管相连,所述mos管与所述从设备的第一管脚相连接,所述第一管脚与所述主设备中的第二管脚相连,所述第二管脚用于提供所述时钟信号;

11、其中,所述控制所述主设备与所述从设备之间的时钟信号保持在第一电平,包括:

12、发送目标电平给所述单稳态触发器,使得所述单稳态触发器进入暂态,所述暂态下的单稳态触发器能够输出高电平,以使得mos管将所述时钟信号钳位到第一电平。

13、上述方法,优选的,在所述主设备与所述从设备处于第一工作模式的情况下,所述mos管为nmos晶体管;所述第一工作模式为所述主设备在所述时钟信号进入上升沿时采集数据的模式;

14、其中,所述nmos晶体管在接收到所述单稳态触发器输出的高电平的情况下,将所述时钟信号钳位到第一电平,所述第一电平为低电平。

15、上述方法,优选的,在所述主设备与所述从设备处于第二工作模式的情况下,所述mos管为pmos晶体管;所述第二工作模式为所述主设备在所述时钟信号进入下升沿时采集数据的模式;

16、其中,所述pmos晶体管在接收到所述单稳态触发器输出的高电平的情况下,将所述时钟信号钳位到第一电平,所述第一电平为高电平。

17、上述方法,优选的,所述单稳态触发器中至少包含有多个备用电阻,且,所述从设备中配置有寄存器,所述寄存器用于存储所述目标时长;

18、其中,所述方法还包括:

19、根据所述寄存器中的所述目标时长,在所述多个备用电阻中确定目标电阻,所述目标电阻使得所述单稳态触发器在接收到所述目标电平时进入所述暂态,且,所述单稳态触发器在所述暂态保持所述目标时长后恢复到稳态,所述稳态下的单稳态触发器能够输出低电平,以使得所述mos管停止将所述时钟信号钳位在所述第一电平。

20、上述方法,优选的,所述从设备中配置有使能位;

21、其中,在监测所述从设备上目标数据是否处理完成之前,所述方法还包括:

22、判断所述使能位是否处于目标状态,如果是,执行所述:监测所述从设备上目标数据是否处理完成。

23、一种spi的从设备,包括:

24、流控器,用于监测所述从设备上目标数据是否处理完成;在所述目标数据处理未完成的情况下,控制所述主设备与所述从设备之间的时钟信号保持在第一电平;在数据读取条件被满足的情况下,控制所述时钟信号恢复到第二电平,所述第二电平用于指示所述主设备读取所述目标数据。

25、上述spi的从设备,优选的,还包括:

26、单稳态触发器;

27、mos管,所述单稳态触发器与所述mos管相连,所述mos管与所述从设备的第一管脚相连接,所述第一管脚与所述主设备中的第二管脚相连,所述第二管脚用于提供所述时钟信号;

28、其中,所述流控器,具体用于发送目标电平给所述单稳态触发器,使得所述单稳态触发器进入暂态,所述暂态下的单稳态触发器能够输出高电平,以使得mos管将所述时钟信号钳位到第一电平。

29、上述spi的从设备,优选的,所述单稳态触发器中至少包含有多个备用电阻,且,所述从设备中配置有寄存器,所述寄存器用于存储所述目标时长;

30、其中,所述流控器,还用于:根据所述寄存器中的所述目标时长,在所述多个备用电阻中确定目标电阻,所述目标电阻使得所述单稳态触发器在接收到所述目标电平时进入所述暂态,且,所述单稳态触发器在所述暂态保持所述目标时长后恢复到稳态,所述稳态下的单稳态触发器能够输出低电平,以使得所述mos管停止将所述时钟信号钳位在所述第一电平。

31、从上述技术方案可以看出,本申请公开的一种spi的主设备读取从设备中数据的控制方法及设备中,通过在从设备上监测目标数据是否被处理完成,在从设备上的目标数据没有处理完成的时候,通过将时钟信号保持在第一电平,使得主设备不去读取目标数据,在数据条件被满足的情况下,再通过将时钟信号恢复到第二电平,使得主设备去读取目标数据。可见,本申请中在监测从设备的数据未处理完成到数据读取条件被满足之前的时间段内,时钟信号保持在第一电平,这段时间内主设备不会去读取目标数据,也就避免主设备在这段时间内读取到无效数据,也就不会增加主设备上的数据处理流程,提高数据处理效率。

技术特征:

1.一种spi的主设备读取从设备中数据的控制方法,其特征在于,应用于所述从设备,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述数据读取条件,包括以下任意一项:

3.根据权利要求1或2所述的方法,其特征在于,所述从设备中设置有单稳态触发器,所述单稳态触发器与mos管相连,所述mos管与所述从设备的第一管脚相连接,所述第一管脚与所述主设备中的第二管脚相连,所述第二管脚用于提供所述时钟信号;

4.根据权利要求3所述的方法,其特征在于,在所述主设备与所述从设备处于第一工作模式的情况下,所述mos管为nmos晶体管;所述第一工作模式为所述主设备在所述时钟信号进入上升沿时采集数据的模式;

5.根据权利要求3所述的方法,其特征在于,在所述主设备与所述从设备处于第二工作模式的情况下,所述mos管为pmos晶体管;所述第二工作模式为所述主设备在所述时钟信号进入下升沿时采集数据的模式;

6.根据权利要求3所述的方法,其特征在于,所述单稳态触发器中至少包含有多个备用电阻,且,所述从设备中配置有寄存器,所述寄存器用于存储目标时长;

7.根据权利要求1所述的方法,其特征在于,所述从设备中配置有使能位;

8.一种spi的从设备,其特征在于,包括:

9.根据权利要求8所述的spi的从设备,其特征在于,还包括:

10.根据权利要求9所述的spi的从设备,其特征在于,所述单稳态触发器中至少包含有多个备用电阻,且,所述从设备中配置有寄存器,所述寄存器用于存储目标时长;

技术总结

本申请公开了一种SPI的主设备读取从设备中数据的控制方法及设备,方法应用于所述从设备,所述方法包括:监测所述从设备上目标数据是否处理完成;在所述目标数据处理未完成的情况下,控制所述主设备与所述从设备之间的时钟信号保持在第一电平;在数据读取条件被满足的情况下,控制所述时钟信号恢复到第二电平,所述第二电平用于指示所述主设备读取所述目标数据。

技术研发人员:李术亮,黄钧

受保护的技术使用者:北京紫光芯能科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!