芯片端口的布设方法、存储介质、电子设备及芯片与流程

本申请属于数字集成电路,特别是涉及芯片设计,具体为一种芯片端口的布设方法、存储介质、电子设备及芯片。

背景技术:

1、ir-drop(电源电压降,,简称压降)是指出现在集成电路设计中电源网络(vdd)和地网络(vss)上电压下降或者升高的一种现象。随着半导体工艺的不断发展,在先进工艺上,金属互连线的宽度越来越窄,因此,金属的电阻值会大幅度上升。最终导致在整个芯片上会存在一定范围的ir-drop。而在数字集成电路的设计中,每个逻辑单元(或者称之为逻辑单元)的电流都会对其他逻辑单元造成不同程度的ir-drop。若这些逻辑单元通过金属线互联后同时翻转,就会产生非常明显的ir-drop现象。在先进工艺中,ir-drop的产生会极大地影响芯片的时序、信号完整性甚至影响到芯片的运行速度。

2、在越来越复杂的数字集成电路设计中,对更多功能的需求大大增加,导致设计规模也不断激增。而不同功能的模块在集成时会存在运行频率不相同的情况。因此,最终在芯片的端口上也会存在不同频率的输入或输出端口(port)。在数字后端设计中,端口的摆放会对逻辑单元摆放(placement)的密度(density)值、拥塞(congestion)情况以及后续的时序收敛产生重要影响。

3、在对早期ir-drop的评估上,现有的技术方案主要是通过在placement的结果上,通过设置一些新的仿真参数(如翻转率、电压参数等)后,然后使用其他eda工具进行读取完成placement后的相关数据文件,来得到相对具体的ir-drop的报告,进而对设计进行修改迭代。而对于存在大量高翻转port的设计中,现有的大多数技术方案单纯依靠设计的数据流或顶层的布局规划来获取。一般在顶层布局规划完成后,其port的位置已经固定。这对于一些port摆放灵活性较高的模块来说,并不一定是最优的port摆放方案。

4、现有技术方案在对早期ir-drop评估上亦存在一些局限性,其局限性主要体现在:

5、1)早期ir-drop评估中,后端设计者对设计中不同逻辑单元具体翻转的时间窗口不够清楚,这会导致设置的仿真参数的精度偏差较大,进而影响早期ir-drop评估结果的准确性。

6、2)若采用与当前集成电路设计不同的eda工具进行早期ir-drop的评估,一方面,需要额外花费较多时间来熟悉该工具的使用。另一方面,不同eda工具在评估ir-drop时会因算法上的差异,使得评估结果的一致性变差。

技术实现思路

1、本申请提供一种芯片端口的布设方法、存储介质、电子设备及芯片,用于优化芯片端口的摆放位置,并对芯片的压降进行预警。

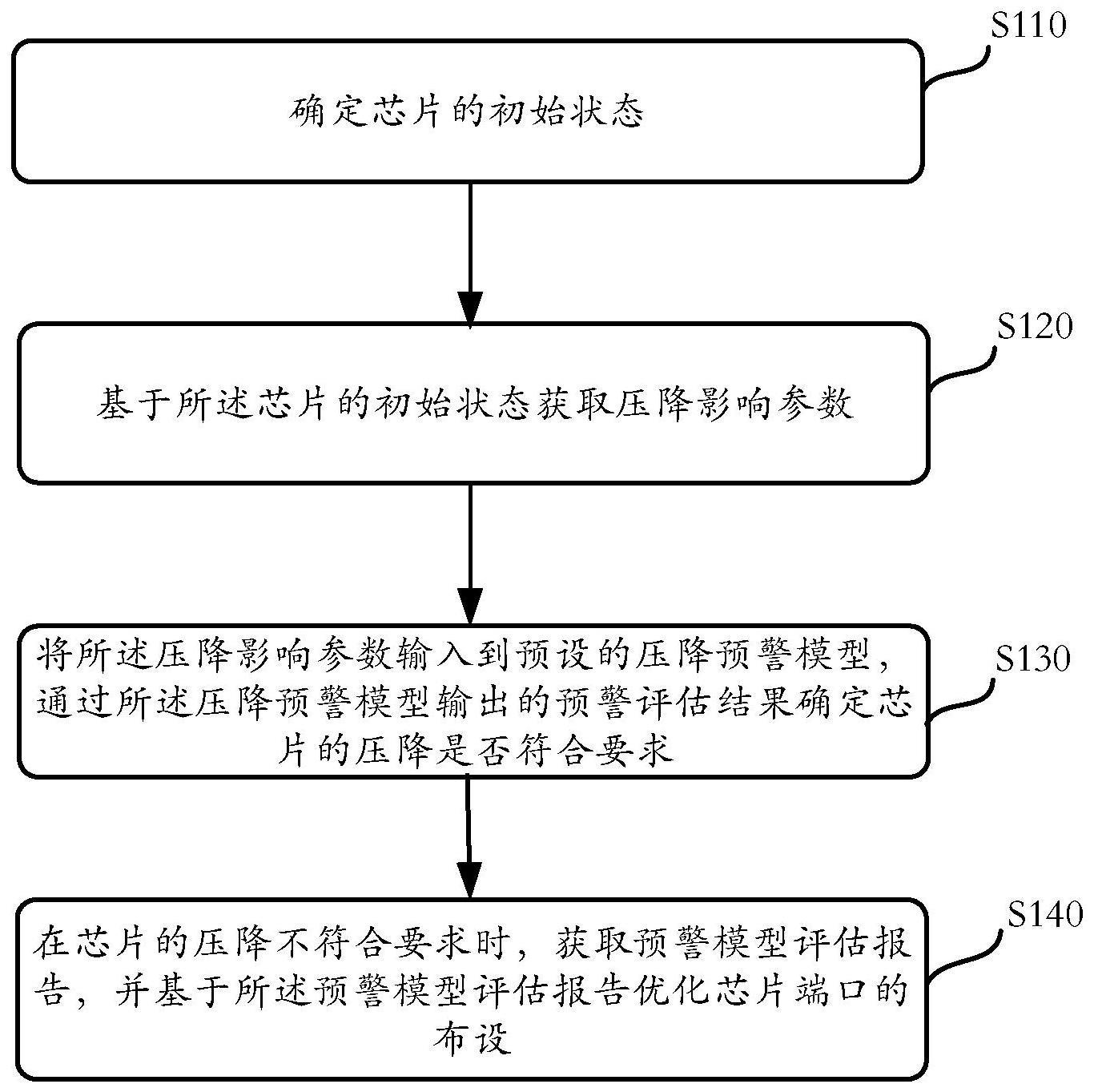

2、第一方面,本申请实施例提供一种芯片端口的布设方法,包括:确定芯片的初始状态;基于所述芯片的初始状态获取压降影响参数;将所述压降影响参数输入到预设的压降预警模型,通过所述压降预警模型输出的预警评估结果确定芯片的压降是否符合要求;在芯片的压降不符合要求时,获取预警模型评估报告,并基于所述预警模型评估报告优化芯片端口的布设。

3、在所述第一方面的一种实现方式中,所述确定芯片的初始状态包括:读取芯片设计图;基于所述芯片设计图检测预设的至少一个芯片初始状态参数是否符合设计需求;响应于所述芯片初始状态参数符合设计需求,为芯片布设初始端口和初始逻辑单元,形成芯片的初始状态。

4、在所述第一方面的一种实现方式中,所述芯片初始状态参数包括初始芯片利用率;所述基于所述芯片设计图检测预设的至少一个芯片初始状态参数是否符合设计需求包括:检测所述初始芯片利用率是否不大于芯片利用率阈值;响应于所述初始芯片利用率不大于芯片利用率阈值,确定所述初始芯片利用率符合检测需求。

5、在所述第一方面的一种实现方式中,所述芯片初始状态参数包括芯片端口摆放的边沿;所述基于所述芯片设计图检测预设的至少一个芯片初始状态参数是否符合设计需求包括:检测所述芯片端口摆放的边沿相对芯片的位置;基于所述芯片端口摆放的边沿相对所述芯片的位置确定所述芯片端口摆放的边沿是否正确;响应于所述芯片端口摆放的边沿正确,确定所述芯片端口摆放的边沿符合检测需求。

6、在所述第一方面的一种实现方式中,所述压降影响参数至少包括频率翻转因子,相邻高翻转端口之间的最大摆放密度值,电压阈值以及拥塞系数中的任一个或多种组合。

7、在所述第一方面的一种实现方式中,所述压降预警模型的一种表达方式为:

8、q*α+denmax*β+vtmax*γ+δ*λ≤ε;

9、其中:q为频率翻转因子,denmax为相邻高翻转端口之间的最大摆放密度值,vtmax为电压阈值,δ为拥塞系数,α,β,γ,λ为比例系数,ε为预警因子。

10、在所述第一方面的一种实现方式中,所述频率翻转因子的一种表达方式为:

11、q=freq*a;

12、其中:freq为逻辑门的时钟频率,a为平均开关翻转因子;

13、所述拥塞系数的一种表达方式为:

14、

15、其中,为芯片中含有端口边沿上的平均端口间距,δl为相邻高翻转端口的间距,denport_max为相邻高翻转端口之间的最大摆放密度值,ψ和ξ为比例系数。

16、在所述第一方面的一种实现方式中,基于所述预警模型评估报告优化芯片端口的布设包括:在所述芯片的压降不符合要求时,重复执行下述过程,直至所述芯片的压降符合要求,完成芯片端口的布设:若从所述预警模型评估报告确定芯片端口的间距相对较小,增大间距较小的芯片端口的间距,生成芯片的当前状态;基于所述芯片的当前状态更新所述压降影响参数;基于更新的所述压降影响参数和所述压降预警模型重新确定芯片的压降是否符合要求。

17、第二方面,本申请实施例提供一种计算机可读存储介质,其上存储有计算机程序,该计算机程序被处理器执行时实现本申请第一方面中任一项所述的芯片端口的布设方法。

18、第三方面,本申请实施例提供一种电子设备,所述电子设备包括:存储器,存储有一计算机程序;处理器,与所述存储器通信相连,调用所述计算机程序时执行本申请第一方面中任一项所述的芯片端口的布设方法。

19、第四方面,本申请实施例提供一种芯片,所述芯片应用如上所述的芯片端口的布设方法布设芯片端口。

20、本申请实施例提供的芯片端口的布设方法,通过压降影响参数构建压降预警模型,可以对芯片的压降是否符合要求进行判断预警,并可以优化芯片端口的布设。本发明简单,易于实现,又可以减少设计的迭代次数。

技术特征:

1.一种芯片端口的布设方法,其特征在于,包括:

2.根据权利要求1所述的芯片端口的布设方法,其特征在于,所述确定芯片的初始状态包括:

3.根据权利要求2所述的芯片端口的布设方法,其特征在于,所述芯片初始状态参数包括初始芯片利用率;

4.根据权利要求2或3所述的芯片端口的布设方法,其特征在于,所述芯片初始状态参数包括芯片端口摆放的边沿;

5.根据权利要求1所述的芯片端口的布设方法,其特征在于,所述压降影响参数至少包括频率翻转因子,相邻高翻转端口之间的最大摆放密度值,电压阈值以及拥塞系数中的任一个或多种组合。

6.根据权利要求5所述的芯片端口的布设方法,其特征在于,所述压降预警模型的一种表达方式为:

7.根据权利要求6所述的芯片端口的布设方法,其特征在于,所述频率翻转因子的一种表达方式为:

8.根据权利要求1所述的芯片端口的布设方法,其特征在于,基于所述预警模型评估报告优化芯片端口的布设包括:

9.一种计算机可读存储介质,其上存储有计算机程序,其特征在于,该计算机程序被处理器执行时实现权利要求1至8中任一项所述的芯片端口的布设方法。

10.一种电子设备,其特征在于,所述电子设备包括:

11.一种芯片,其特征在于,所述芯片应用如权利要求1至8中任一项所述的芯片端口的布设方法布设芯片端口。

技术总结

本申请提供一种芯片端口的布设方法、存储介质、电子设备及芯片。所述方法包括:确定芯片的初始状态;基于所述芯片的初始状态获取压降影响参数;将所述压降影响参数输入到预设的压降预警模型,通过所述压降预警模型输出的预警评估结果确定芯片的压降是否符合要求;在芯片的压降不符合要求时,获取预警模型评估报告,并基于所述预警模型评估报告优化芯片端口的布设。本申请提供的芯片端口的布设方法,通过压降影响参数构建压降预警模型,可以对芯片的压降是否符合要求进行判断,并可以优化芯片端口的布设。

技术研发人员:刘泽法,葛亮,宋颖

受保护的技术使用者:上海合芯数字科技有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!