基于FPGA的多节点缓存一致性系统验证模组及方法与流程

本发明涉及基于fpga的项目开发和芯片原型验证,尤其是指一种基于fpga的多节点缓存一致性系统验证模组及方法。

背景技术:

1、fpga(field-programmablegatearray):fpga是一种可编程逻辑器件,具有可重构的特性。它可以通过编程来实现各种数字电路功能,并且可以在运行时重新配置。fpga具有并行处理能力和高度灵活性,因此在硬件验证和原型开发中得到广泛应用。

2、传统的多节点缓存一致性验证系统往往需要大规模的仿真和调试工作。随着核数增加,验证的复杂性和资源需求也增加,在验证的灵活性、可扩展性、以及真实性评估都难以得到保。传统的基于fpga的缓存一致性系统验证使用fpga作为验证平台,以实现缓存缓存一致性系统级测试用例的设计。通过这样的验证方法,具有灵活性、高性能、可扩展性、真实性能评估和可定制性等优点,但是随着核心数的增加,也往往也面临资源受限和难以调试的问题。

技术实现思路

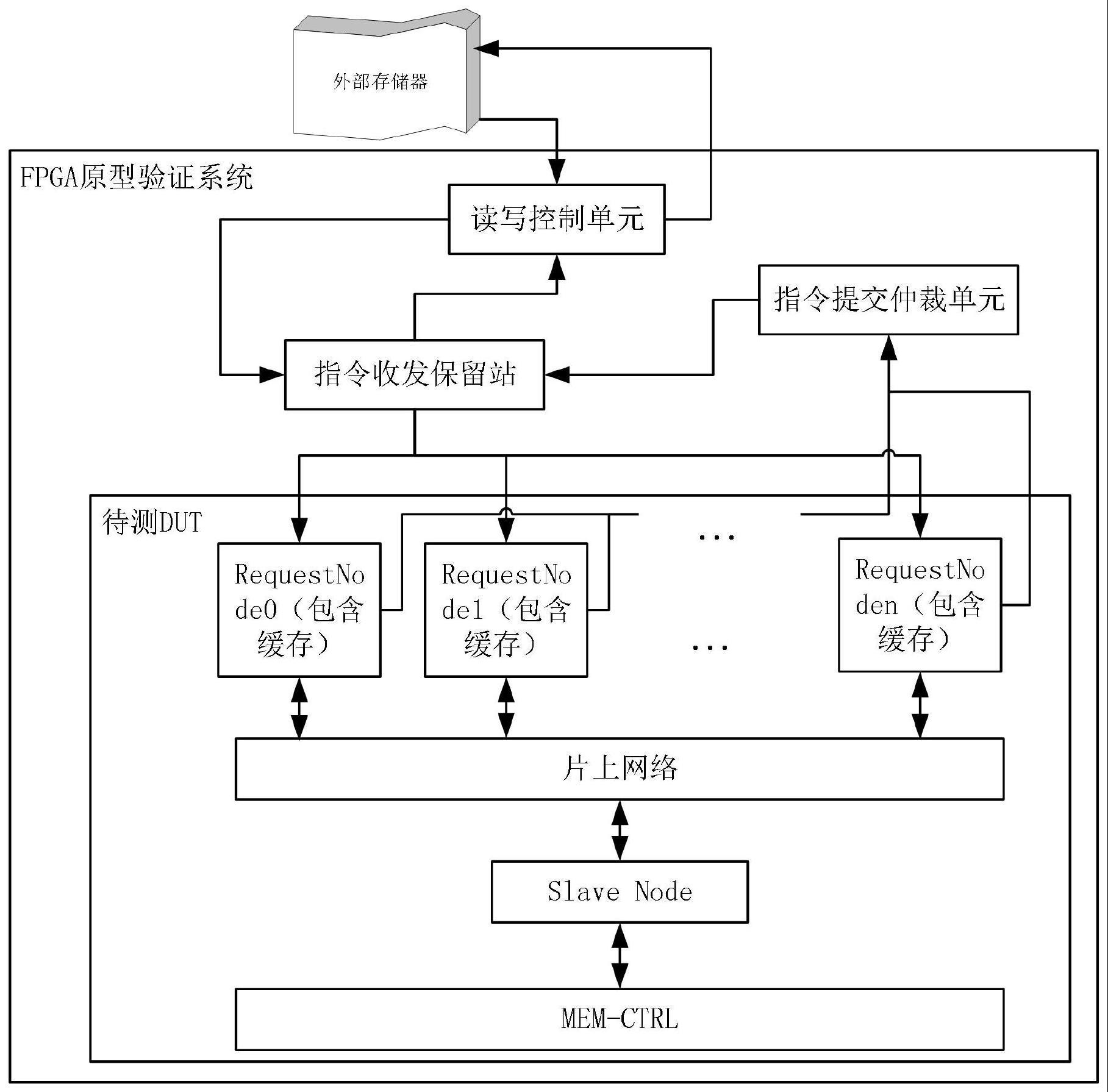

1、为解决上述技术问题,本发明的一种基于fpga的多节点缓存一致性系统验证模组,所述验证模组基于fpga的多节点缓存一致性系统设计,验证模组包括读写控制单元、指令收发保留站、指令提交仲裁单元,以及待测多请求节点的缓存一致性系统dut;

2、其中的读写控制单元一端设有外部存储器,与之组成信息互联结构,同时读写控制单元另一端与指令收发保留站相连,且指令收发保留站将释放完成了的指令信息回传读写控制单元;具体地,读写控制单元控制外部存储器的读写,将外部存储器读到指令数据发送到指令收发保留站,将指令收发保留站释放的完成了的指令信息写回到外部存储。

3、待测多请求节点的缓存一致性系统dut中设有各个请求节点requsetnode,其中的请求节点requsetnode输出端与指令提交仲裁单元之间相连,即将请求节点requsetnode发送的完成指令信息由指令提交仲裁单元中设有的仲裁控制模块接收,另一方面,请求节点requsetnode接收端与指令收发保留站之间相连,其中指令收发保留站中设有的指令存储实体,将存储的指令按序发送到请求节点requsetnode;

4、待测多请求节点的缓存一致性系统dut为待测的多节点缓存一致性系统的rtl代码,其中请求节点requsetnode可以为多个,且每个请求节点都包含缓存一致性系统中的私有缓存,此外还拥有slave node用来处理缓存一致性系统中与内存mem的一致性事务处理。

5、在本发明的一个实施例中,所诉指令收发保留站包括写指针控制模块、读地址指针控制模块、写地址指针控制模块、指令存储读写控制模块、写地址指针fifo、读地址指针fifo、指令存储实体以及state向量;

6、写地址指针控制模块依据读写控制单元的指令和读地址指针的控制信息,控制写地址指针fifo的存储的读写,读地址指针控制模块依据指令存储读写控制模块和写地址指针的控制信息,控制读地址指针fifo的存储的读写;指令存储读写控制模块依据写地址指针控制模块和读地址指针fifo的控制模块信息,控制的指令存储实体的读写以及state向量的改变,同时将指令存储实体中存储的指令按序发送到待测多请求节点的缓存一致性系统dut中的个请求节点requsetnode。

7、在本发明的一个实施例中,所述指令提交仲裁单元包括仲裁控制模块、完成指令存储读写控制模块、以及完成指令缓存fifo;

8、仲裁控制模块接收来多请求节点的缓存一致性系统待测dut中各个请求节点requsetnode发送的完成指令信息,并对产生竞争提交的完成指令信息进行排序,并存存入完成指令缓存fifo中;完成指令存储读写控制模块控制完成指令缓存fifo的读写,并根据仲裁控制模块的信息将完成指令存储存入完成指令缓存fifo中,同时将完成指令缓存fifo中的暂存完成指令信息发送到指令收发保留站。

9、在本发明的一个实施例中,所述读写控制单元控制外部存储器读写,对于来自外部存储器需要进行验证的指令信息,读写控制单元根据其状态信息,将指令依次读取出来,指令信息内容为节点信息coreid、地址address、操作码opcode、粒度grid以及数据data;对于来自指令收发保留站提交上来的完成指令信息,写入到外部存储器中,其指令信息包含:完成指令计数信息count、coreid、地址address、操作码opcode、粒度grid以及数据data。

10、在本发明的一个实施例中,所述指令收发保留站具有的指令信息接收、存储、发送以及提交释放的功能,包含指令收发保留站处理指令信息的方法,具体步骤如下:

11、步骤s1:在接收读写控制单元的第一条信息之前,写地址指针控制模块将所有的id信息存入到写地址fifo中,将写地址指针写满,id即为指令存储实体的地址或者即id与指令存储实体的地址逐建立唯一映射关系或者直接对应关系;

12、步骤s2:当写地址指针fifo写满时,即可接收来自读写控制单元的指令信息和来自指令提交仲裁单元的完成指令信息;

13、步骤s3:对接收来自读写控制单元的指令信息,读地址指针控制模块从读地址指针fifo中读取id,指令存储读写控制模块根据此id信息在指令存储实体的对应地址的指令,再配合id以及coreid发送将指令信息到对应请求节点requestnode中,更新state向量,指令信息包含内部序号id、节点点信息coreid、地址address、操作码opcode、粒度grid以及数据data,state向量中每个id都有效位valid和占用位busy;

14、对接收来自指令提交仲裁单元的完成指令信息,完成指令信息包含内部序号id、节点点信息coreid、地址address、操作码opcode、粒度grid以及数据data,指令存储读写控制模块以及内部需要id释放存储在指令存储实体中的指令,腾出存储空间,写地址指针控制将id信息存储到写地址指针中,同时将完成指令发送到读写控制单元。

15、在本发明的一个实施例中,步骤s2中的当接收来自读写控制单元的指令信息时,写地址指针控制模块读取写地址指针fifo中的id,并根据id与指令存储实体的地址关系,将来自读写控制单元的指信息存储到指令存储实体中,并更新对应的state向量,同时,读地址指针控制模块将来自写地址指针fifo中的id写入读地址指针的fifo中;

16、当接收来自指令提交仲裁单元的完成指令时,指令存储读写控制模块根据完成指令信息中id与指令存储实体的地址关系,读取之指令存储实体的指令,并更新其对应的state向量,同时写地址指针控制模块将完成指令信息中id写入到写地址指针fifo中。

17、本发明还提供基于fpga的多节点缓存一致性系统验证方法,所述的验证方法基于验证模组搭建,针对多节点缓存一致性系统形成自动化信息流,包括如下步骤:

18、步骤s11:系统初始化,指令收发保留站中写地址指针fifo初始化,即写地址指针控制模块将所有的id信息存入到写地址fifo中,将写地址指针写满,建立id与指令存储实体的地址逐映射关系;

19、步骤s12:读写控制单元从fpga原型验证系统外的外部存储器中读取已经生成的指令信息,指令信息包含节点信息coreid、地址address、操作码opcode、粒度grid以及数据data;

20、步骤s13:指令收发保留站将来自读写控制单元的指令信息进行存储和编码,编码后的指令信息包含保留站内部序号id、节点信息coreid、地址address、操作码opcode、粒度grid以及数据data,然后将编码后的指令信息发送到待测多请求节点的缓存一致性系统dut中的个请求节点requset node;

21、步骤s14:指令提交仲裁单元接收来自待测多请求节点的缓存一致性系统dut中的个请求节点requsetnode的完成指令,完成指令信息包含保留站内部序号id、节点点信息coreid、地址address、操作码opcode、粒度grid以及数据data,指令提交仲裁单元完成的指令发送到指令收发保留站,指令收发保留站释放存储在指令存储实体中的指令,然后将完成指令发送到读写控制单元;

22、步骤s15:读写控制单元将接收到的完成指令以完成状态写入外部存储器中,留待检查分析。

23、本发明的上述技术方案相比现有技术具有以下优点:本发明所述的验证模组针对待测多节点缓存一致性系统验证,模组具有灵活的扩展性;同时验证方法,指令的存储、转发、释放有着灵活适配外部不同的存储指令仿真。

- 还没有人留言评论。精彩留言会获得点赞!