一种FPGA故障检测方法及系统与流程

本申请涉及集成电路,具体而言,涉及一种fpga故障检测方法及系统。

背景技术:

1、随着集成电路工艺发展和设计技术革新,逻辑门尺寸不断减小,供电电压不断降低,工作频率不断升高,期间制造工艺也从微米级工艺向纳米级甚至几纳米级别发展;使得电子系统变得日益复杂且其电磁敏感度不断升高,对静电也越来敏感。对fpga来说也就是越高性能的fpga采用的制造工艺也越小,同时也越容易被电磁干扰和被静电(esd)损坏。相关技术中,当fpga出现故障时,采用传统的fpga检测方法不能快速检测出fpga存在故障的位置。

技术实现思路

1、为了能够快速地检测出fpga的故障情况,本申请提供一种fpga故障检测方法及系统。

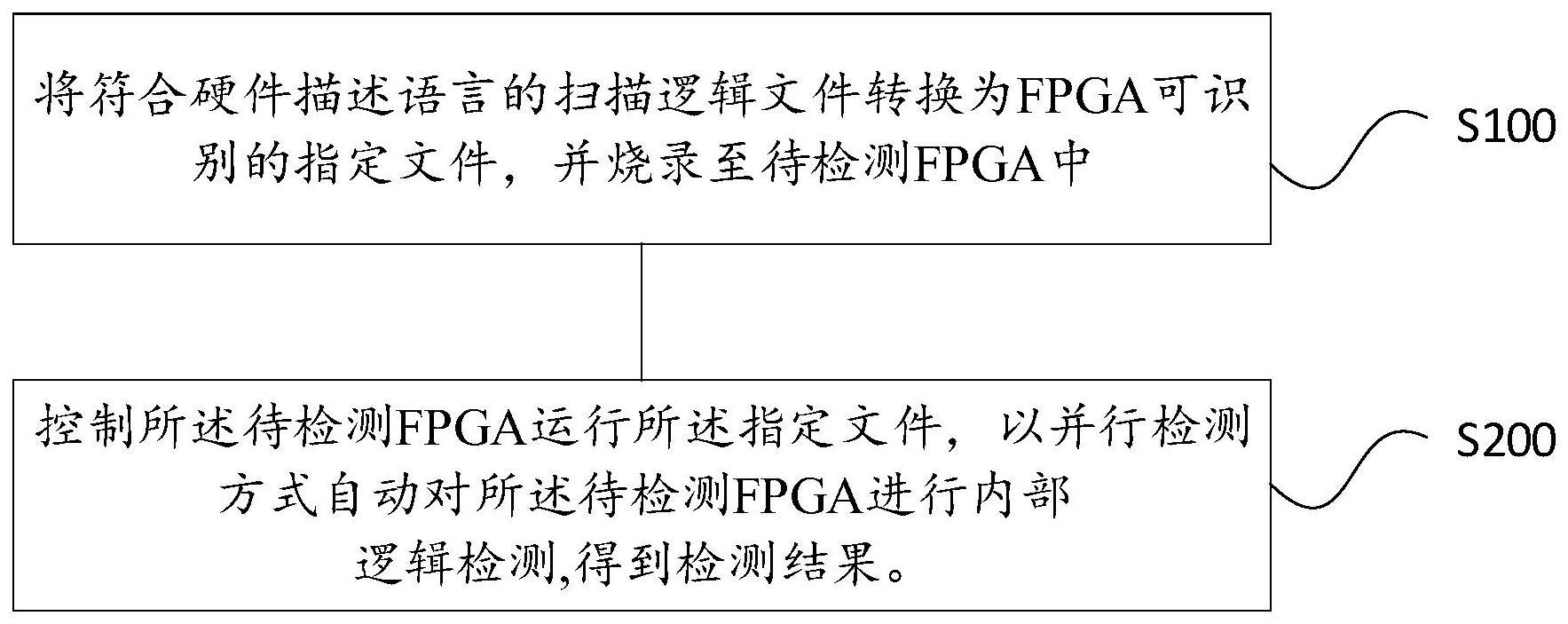

2、第一方面,本申请实施例提供一种fpga故障检测方法,包括:将符合硬件描述语言的扫描逻辑文件转换为fpga可识别的指定文件,并烧录至待检测fpga中。控制所述待检测fpga运行所述指定文件,以并行检测方式自动对所述待检测fpga进行内部逻辑检测,得到检测结果。

3、在上述实现方式中,通过先将符合硬件描述语言的扫描逻辑文件转换为fpga可以识别的文件并烧录至fpga中,然后以并行检测方式对待检测fpga自动进行内部逻辑检测。待检测fpga以并行检测方式自动进行内部逻辑检测,能快速地检测出待检测fpga的故障情况。

4、可选的,在将符合硬件描述语言的扫描逻辑文件转换为fpga可识别的指定文件之前,所述方法还包括:基于fpga标准输入文件和扫描配置信息生成所述扫描逻辑文件,其中,所述扫描配置信息用于指示所述待检测fpga中的待扫描模块。

5、在上述实现方式中,在生成逻辑扫描文件时不需要手写复杂的程序,以fpga标准文件和配置信息生成,能够节省大量的开发成本。

6、可选的,基于fpga标准输入文件和扫描配置信息生成所述扫描逻辑文件,包括:基于所述扫描配置信息,获取所述待检测fpga中的待扫描模块;从所述fpga标准输入文件中获取所述待扫描模块的内部逻辑电路;将所述待扫描模块的内部逻辑电路转换成多条测试链,其中,每条测试链包括:串联通路,所述串联通路与所述待检测fpga的虚拟io连接,所述串联通路的输入端连接至所述待检测fpga的虚拟输出端口,所述串联通路的输出端连接至所述待检测fpga的虚拟输入端口。

7、在上述实现方式中,将待扫描模块的内部逻辑电路转换成多条测试链,通过每一条测试链的输出状态,得到每一条测试链的故障情况,进而得到待检测fpga的故障情况。该方法有效解决了当检测到待检测fpga存在故障情况时,由于待检测fpga内部逻辑电路过多,无法判断具体是什么位置出现故障的问题。

8、可选的,将所述待扫描模块的内部逻辑电路信息转换成多条测试链,包括:针对所述待扫描模块中的每一条虚拟io,将所述待扫描模块中位于该条虚拟io附近的内部逻辑电路按照原有顺序串联起来,形成测试链,得到多条测试链。

9、在上述实现方式中,上述方案中以每一条虚拟io附近的内部逻辑电路按照原有顺序串联起来形成测试链,根据检测过程中每一条测试链的虚拟io状态,可以更准确地检测出待检测fpga中的故障位置。

10、可选的,所述指定文件包含待检测的多条测试链;以并行检测方式自动对所述待检测fpga进行内部逻辑检测,包括:自动修改所述多条测试链中每条测试链的输入状态;检测每条测试链的输出结果是否符合预期,得到检测结果。

11、在上述实现方式中,通过自动修改待检测fpga中每条测试链的输入状态,并自动读取测试链的输出状态,结合原测试链的输入状态,判断每条测试链的故障情况,进而得到待检测fpga的故障情况,能够检测出待检测fpga故障存在的位置。

12、可选的,所述输出结果包括输出状态,检测每条测试链的输出结果是否符合预期,包括:针对每一条测试链,检测该测试链的输出状态是否与修改后的输入状态对应;若对应,表征该测试链的输出结果符合预期。

13、在上述实现方式中,因为每条测试链的原有输入状态与原有输出状态对应,当将待检测fpga的内部逻辑电路串联形成测试链时,若改变每条测试链的输入状态,对应每条测试链的输出状态也会发生改变,基于每条测试链的输出状态与输入状态的对应关系,可以更直观地知道待检测fpga的故障情况。

14、可选的,所述方法还包括:基于所述检测结果,自动输出检测报告。在待检测fpga完成自动检测后,自动对该检测结果进行分析,并自动输出检测报告。

15、在上述实现方式中,通过分析检测结果,自动输出检测报告。自动对待检测fpga中的虚拟io状态进行分析,因为待检测fpga具有多条虚拟io,将每条虚拟io附近的内部逻辑电路串联,形成多条测试链。待检测fpga自动对多条测试链进行并行测试,每改变测试链的输入状态时,需要同时关注多个测试链的输出状态。通过自动读取每条测试链改变后的输入状态与输出状态,结合每条测试链原有的输入状态与输出状态,得到每条测试链的故障情况,自动输出包含每条测试链故障情况的检测报告。通过检测报告可以直接得到待检测fpga的故障情况。该方案有效降低操作难度,节省检测时间,同时也降低了对测试人员的知识原理要求。

16、第二方面,本申请实施例还提供一种fpga故障检测系统,包括:待检测fpga;上位机,与所述待检测fpga连接,所述上位机将符合硬件描述语言的扫描逻辑文件转换为fpga可识别的指定文件,并烧录至待检测fpga中;以及控制所述待检测fpga运行所述指定文件,以并行检测方式自动对所述待检测fpga进行内部逻辑检测,得到检测结果。

17、可选的,所述上位机还用于基于fpga标准输入文件和扫描配置信息生成所述扫描逻辑文件,其中,所述扫描配置信息用于指示所述待检测fpga中的待扫描模块。

18、可选的,所述上位机用于:基于所述扫描配置信息,获取所述待检测fpga中的待扫描模块;从所述fpga标准输入文件中获取所述待扫描模块的内部逻辑电路;将所述待扫描模块的内部逻辑电路转换成多条测试链,其中,每条测试链包括:串联通路,所述串联通路与所述待检测fpga的虚拟io连接,所述串联通路的输入端连接至所述待检测fpga的虚拟输出端口,所述串联通路的输出端连接至所述待检测fpga的虚拟输入端口。

技术特征:

1.一种fpga故障检测方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,在将符合硬件描述语言的扫描逻辑文件转换为fpga可识别的指定文件之前,所述方法还包括:

3.根据权利要求2所述的方法,其特征在于,基于fpga标准输入文件和扫描配置信息生成所述扫描逻辑文件,包括:

4.根据权利要求3所述的方法,其特征在于,将所述待扫描模块的内部逻辑电路转换成多条测试链,包括:

5.根据权利要求1所述的方法,其特征在于,所述指定文件包含待检测的多条测试链;以并行检测方式自动对所述待检测fpga进行内部逻辑检测,包括:

6.根据权利要求5所述的方法,其特征在于,所述输出结果包括输出状态,检测每条测试链的输出结果是否符合预期,包括:

7.根据权利要求1-6中任一项所述的方法,其特征在于,所述方法还包括:

8.一种fpga故障检测系统,其特征在于,包括:

9.根据权利要求8所述的fpga故障检测系统,其特征在于,所述上位机用于:

10.根据权利要求9所述的fpga故障检测系统,其特征在于,所述上位机还用于:

技术总结

本申请提供一种FPGA故障检测方法及系统,该方法包括:将符合硬件描述语言的扫描逻辑文件转换为FPGA可识别的指定文件,并烧录至待检测FPGA中。控制所述待检测FPGA运行所述指定文件,以并行检测方式自动对所述待检测FPGA进行内部逻辑检测,得到检测结果。本申请能够准确有效地检测出FPGA的故障位置,对于故障部分可以在设计部分避免使用,以及针对性修复,也降低了研发成本和试错成本。

技术研发人员:张公健,张跃,陈金霞

受保护的技术使用者:昆腾微电子股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!