一种雷达信号存储与处理系统及方法

本发明涉及数据存储技术,尤其涉及一种雷达信号存储与处理系统及方法。

背景技术:

1、随着雷达技术的发展,雷达收集到的数据量呈指数级增长,然而由于网络带宽、电磁干扰和信息安全等因素的影响,雷达信号数据通常需要先在本地实时存储后再进行数据的读取和分析。雷达信号由海量的小数据项组成,每项数据包含多个字段代表了每个信号的多维特征。由于环境和设备的原因存在多种形式的误差,需要读取出信号的原始数据后进行降噪、分选等处理。如何高效地存储读写和分析数据是一个挑战。雷达信号中最重要的字段之一是toa(信号到达时间),即雷达信号被接受的时间。雷达系统在工作时会不断接受信号,因此toa是单调递增且不重复的。相邻雷达信号的toa差值被称为pri值,是雷达识别的重要特征。

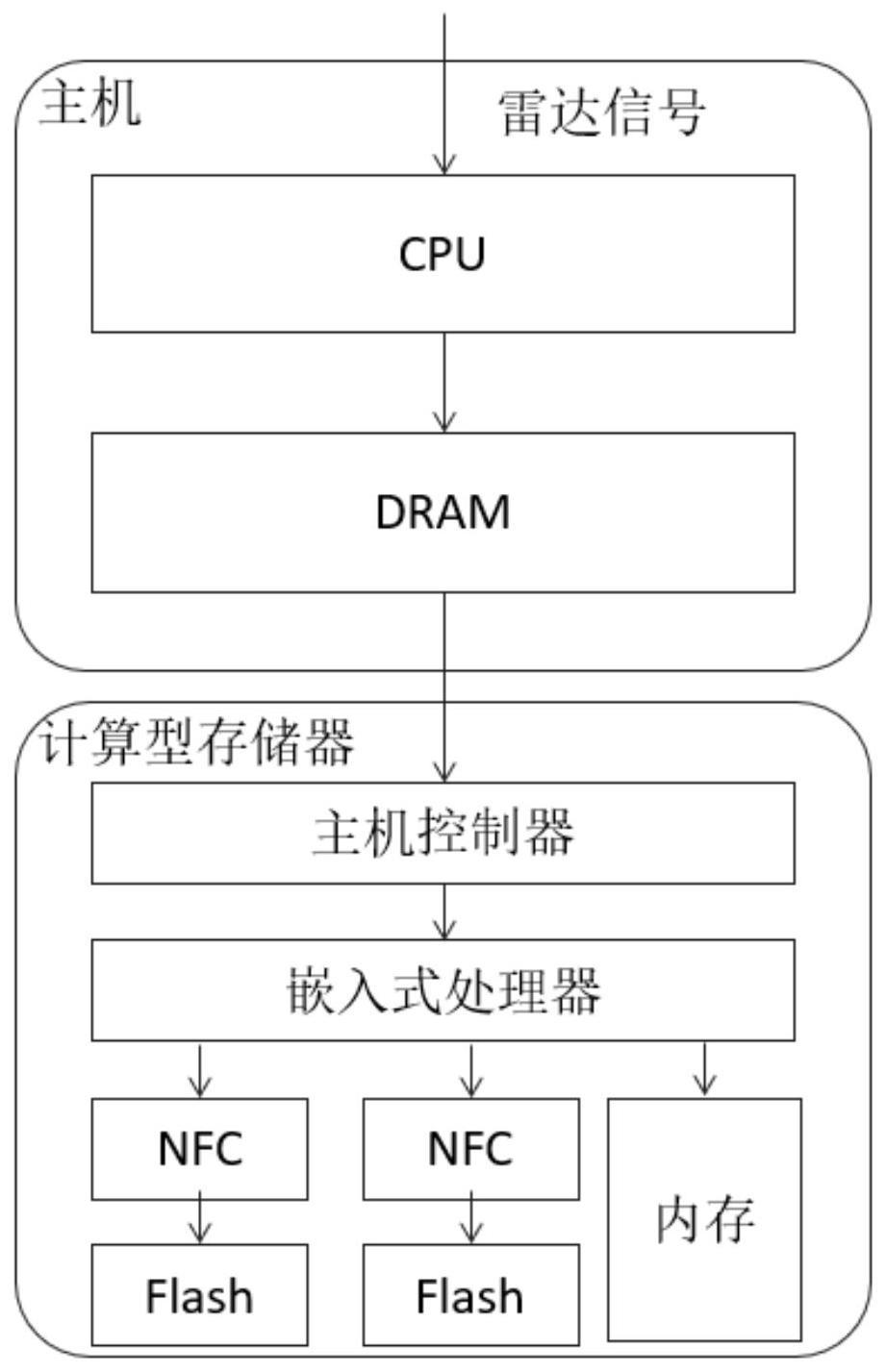

2、ssd(固态存储器)由于具有高带宽、低延迟和大容量的优点,被广泛用于雷达信号的存储。如图1所示,ssd内部由主机控制器、闪存芯片、nfc(nand闪存控制器)、嵌入式处理器和dram组成。分别用于与主机交互传输数据、持久化存储数据、控制闪存芯片、对整个ssd进行管理和缓存数据。由于ssd通常配备有多个闪存芯片和nfc,因此ssd内部可以多通道并行读写达到很高的内部带宽。

3、然而,在传统计算机架构下进行雷达信号的存储以及处理的效率会受限。图2展示了雷达信号读写以及处理的流程。在信号写入时,采集到的雷达信号需要存储到数据库中,需要进行信号到数据库表项的映射。数据库通常以文件的形式存储数据,需要进行数据库表到文件的映射。文件系统负责将文件映射为存储器的lpn(逻辑页号),然后经过块层和驱动层发送给ssd。在ssd中主机控制器将逻辑地址转换为ppn(物理页号)。在进行信号识别时,同样需要经过i/o栈进行多次数据映射才能获取数据位置并且读取所有原始数据到主机中才能进行识别获取结果,可以看出,传统计算机架构中由于这些冗余的i/o栈和大量无用数据的传输,大大限制了系统的性能。

技术实现思路

1、有鉴于此,本发明的首要目的在于提供一种雷达信号存储与处理系统,通过对雷达信号数据的数据布局方式和处理方法进行改进,采用计算型存储器代替传统存储器,通过高速pcie总线连接到主机中,从而提高信号的存储和处理性能,使其在存储器内实现快速的雷达信号处理并且降低对普通i/o的影响。

2、为了实现上述目的,本发明采用的技术方案如下:

3、一种雷达信号存储与处理系统,其关键在于,包括主机和计算型存储器,所述主机通过高速pcie总线与所述计算型存储器连接,所述主机包括cpu和dram,所述计算型存储器包括主机控制器、嵌入式处理器、内存、多个闪存和多个闪存控制器;所述主机中加载有雷达信号处理应用程序,在所述dram中存储有雷达信号处理库和驱动程序,所述主机通过cpu运行所述雷达信号处理应用程序并调用所述雷达信号处理库中的信号处理函数,然后由所述驱动程序向所述计算型存储器发送处理请求;所述嵌入式处理器中配置有请求调度器、雷达信号布局管理器和闪存转换层,所述处理请求进入所述计算型存储器后,先进入请求调度器中的请求队列等待调度执行,在获得执行机会后通过雷达信号布局管理器查询雷达信号读/写位置,并在计算型存储器内执行雷达信号处理请求中所包含的计算操作。

4、可选地,所述主机接收到雷达信号后,将雷达信号的字段拆分存储,一段连续雷达信号的相同字段单独存储到同一个闪存页中,且将表征雷达信号到达时间的字段作为索引值存储在内存的检索列表中。

5、可选地,在进行雷达信号存储时,所述主机先以bank为单位将雷达信号缓存在所述dram中的缓冲区中,当一个bank对应的缓冲区写满后,则通过直接内存访问将所述缓冲区的数据全部发送到所述计算型存储器中,然后清空所述缓冲区用于接收后续雷达信号。

6、可选地,每个bank对应一组闪存页,每个bank存储一组雷达信号,bank的大小取决于信号中字段的数量,具体为bank=feature_count*page_size,其中feature_count指雷达信号字段的数量,page_size指一个闪存页的大小,一个bank可以存储的信号数量为signal_per_bank=page_size/feature_size,其中feature_size指每个雷达字段的大小。

7、可选地,所述雷达信号布局管理器采用闪存页面静态分配方式,将一个bank中连续的逻辑页号依次分配到不同闪存中,所述闪存控制器中的闪存转换层用于实现对应闪存内的物理页分配。

8、可选地,所述内存中的数据结构包括元数据和索引列表,所述元数据存储有当前状态和系统配置信息,包括当前系统中雷达信号存储数量、存储雷达信号的起始逻辑页号值、下一个bank对应的逻辑页号值以及指向索引列表的起始内存地址,所述索引列表为一个数组,里面的每个元素是一个雷达信号到达时间值,且按顺序存放了每个bank的起始雷达信号到达时间值,索引列表的长度与bank的数量相同。

9、基于上述系统,本发明的另一目的在于提供一种雷达信号存储方法,采用前文所述的雷达信号存储与处理系统,其关键在于,包括以下步骤:

10、s11:在dram中将雷达信号的每个字段对应设置一个缓冲区,所有的缓冲区共同作为一个bank缓存数据,当主机接收到雷达信号后,将每个字段写入到其对应的缓冲区中;

11、s12:检查当前缓冲区是否已满,如果未满,则继续写入后续雷达信号,如果已满,则通过直接内存访问将所述缓冲区的数据全部发送到所述计算型存储器中,然后清空所述缓冲区用于接收后续雷达信号;

12、s13:计算型存储器通过雷达信号布局管理器查询雷达信号写位置;

13、s14:向对应的闪存转换层发起闪存页面写请求,将信号数据写入到闪存中。

14、可选地,步骤s13中,所述雷达信号布局管理器通过查询内存中的元数据来获取下一个空闲bank的起始逻辑页号值,从而确定雷达信号写位置,在完成步骤s14之后还包括:

15、s15:更新内存中的元数据。

16、此外,本发明的第三目的还在于提供一种雷达信号处理方法,采用前文所述的雷达信号存储与处理系统,其关键在于,包括以下步骤:

17、s21:计算型存储器进行一次i/o任务调度;

18、s22:判断是否有待接收的雷达信号处理请求,如果有,则进入s23,否则进入s24;

19、s23:接收主机发送的雷达信号处理请求,并检索雷达信号处理请求中雷达信号到达时间值所在的闪存页,然后将雷达信号处理请求插入请求队列中;

20、s24:判断是否有未完成的信号处理请求,如果没有,则返回步骤s21,如果有,则进入步骤s25;

21、s25:从请求队列中取出处理请求,并根据闪存通道数量和读写时延计算能够进行多少次计算;

22、s26:进行计算,并保存计算完成后的上下文信息。

23、可选地,步骤s23中采用二分法检索雷达信号处理请求中雷达信号到达时间值所在的闪存页。

24、本发明的显著效果在于:

25、(1)雷达信号写入速度快,避免了冗余、多级的雷达信号映射,通过条带状布局提高了闪存写入的并发性;

26、(2)雷达信号检索速度快,避免了冗余、多级的雷达信号映射,可以在计算型存储器的内存中定位到信号所在的闪存页面,无需额外的i/o。

27、(3)雷达信号的处理速度快,通过在计算型存储器内进行数据的近存处理,避免了冗余的信号搬运;

28、(4)系统整体功耗低,一方面使用了低功耗的嵌入式处理器进行信号的处理,无需高功耗的主机进行计算;另一方面是减少了大量的数据搬移,减少了i/o能耗开销。

- 还没有人留言评论。精彩留言会获得点赞!