一种跳转指令的预取方法及装置与流程

本发明涉及计算机,尤其涉及一种跳转指令的预取方法及装置。

背景技术:

1、cache(缓存,又称高速缓冲存储器),设置在处理器和主存之间,通常包括多个层级,用于存储指令和数据,解决处理器和主存运行速率不匹配的问题。通常情况下,当处理器需要访问内存时,先访问cache,如果cache中没有所需的指令时,接着访问存储器。对于冯诺依曼体系的处理器,只有一个cache,共同存放指令和数据,而对于哈佛体系的处理器,例如dsp处理器(digital signal processor,数字信号处理器),指令和数据分开,拥有指令cache和数据cache。

2、dsp处理器需要执行大量跳转指令,一旦遇到跳转指令,如果取指部件需要暂停等待,则非常影响处理器的执行性能。跳转指令分为两类:一类是绝对地址跳转指令,指令中携带跳转的目的地址;另一类是相对地址跳转指令,跳转的目的地址是由指令流水线根据跳转指令中的参数计算得到的。

3、对dsp处理器来说,很多时候需要执行大量的绝对地址跳转指令,如何能够使这些绝对地址跳转指令避免在第一级cache中取指失效,是提升dsp访问性能的一个重要目标。

技术实现思路

1、为了解决上述技术问题,本发明提供一种跳转指令的预取方法及装置。

2、具体的,本发明的技术方案如下:

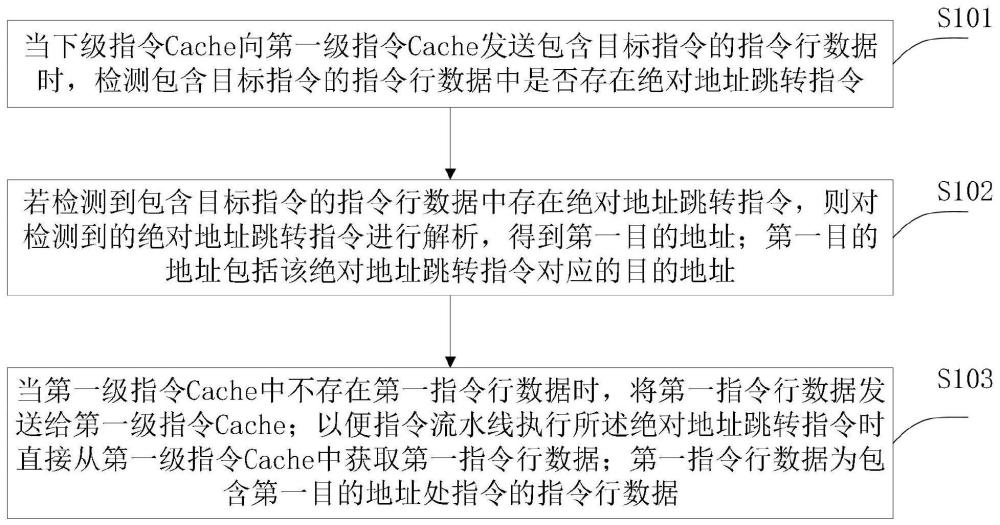

3、一方面,本发明提供一种跳转指令的预取方法,应用于具有哈佛架构的处理器,包括:

4、当下级指令cache向第一级指令cache发送包含目标指令的指令行数据时,检测包含所述目标指令的指令行数据中是否存在绝对地址跳转指令;

5、若检测到包含所述目标指令的指令行数据中存在绝对地址跳转指令,则对检测到的所述绝对地址跳转指令进行解析,得到第一目的地址;所述第一目的地址包括所述绝对地址跳转指令对应的目的地址;

6、当所述第一级指令cache中不存在第一指令行数据时,将所述第一指令行数据发送给所述第一级指令cache;以便指令流水线执行所述绝对地址跳转指令时直接从所述第一级指令cache中获取所述第一指令行数据;所述第一指令行数据为包含所述第一目的地址处指令的指令行数据。

7、在一些实施方式中,所述的当下级指令cache向第一级指令cache发送包含目标指令的目标指令行数据时,检测包含所述目标指令的指令行数据中是否存在绝对地址跳转指令之后,包括:

8、当检测到包含所述目标指令的指令行数据中存在绝对地址跳转指令时,对检测到的首个绝对地址跳转指令进行解析,得到第二目的地址;所述第二目的地址包括所述首个绝对地址跳转指令对应的目的地址;

9、当所述第一级指令cache中不存在第二指令行数据时,将所述第二指令行数据发送给所述第一级指令cache;以便所述指令流水线执行的绝对地址跳转指令为所述首个绝对地址跳转指令时,直接从所述第一级指令cache中获取所述第二指令行数据;所述第二指令行数据包括所述第二目的地址处指令的指令行数据。

10、在一些实施方式中,还包括:

11、接收所述指令流水线下发的获取所述目标指令的取指请求;

12、根据所述取指请求,在所述第一级指令cache中的各指令行中查找是否存在包含所述目标指令的指令行数据;

13、当所述第一级指令cache中不存在包含所述目标指令的指令行数据时,逐级向下一级指令cache中查找包含所述目标指令的指令行数据,直至找到包含所述目标指令的指令行数据;

14、将包含所述目标指令的指令行数据逐级向上反馈至所述第一级指令cache。

15、在一些实施方式中,还包括:

16、当所述第一级指令cache中存在所述目标指令时,将包含所述目标指令的指令行数据发送给所述指令流水线,使所述指令流水线执行所述目标指令。

17、另一方面,本发明提供一种跳转指令的预取装置,应用于具有哈佛架构的处理器,包括:

18、检测模块,用于当下级指令cache向第一级指令cache发送包含目标指令的指令行数据时,检测包含所述目标指令的指令行数据中是否存在绝对地址跳转指令;

19、解析模块,用于若检测到包含所述目标指令的指令行数据中存在绝对地址跳转指令,则对检测到的所述绝对地址跳转指令进行解析,得到第一目的地址;所述第一目的地址包括所述绝对地址跳转指令对应的目的地址;

20、发送模块,用于当所述第一级指令cache中不存在第一指令行数据时,将所述第一指令行数据发送给所述第一级指令cache;以便指令流水线执行所述绝对地址跳转指令时直接从所述第一级指令cache中获取所述第一指令行数据;所述第一指令行数据为包含所述第一目的地址处指令的指令行数据。

21、在一些实施方式中,所述解析模块,还用于当检测到包含所述目标指令的指令行中存在绝对地址跳转指令时,对检测到的首个绝对地址跳转指令进行解析,得到所述首个绝对地址跳转指令对应的目的地址;

22、所述发送模块,还用于当所述第一级指令cache中不存在第二指令行数据时,将所述第二指令行数据发送给所述第一级指令cache;以便所述指令流水线执行的绝对地址跳转指令为所述首个绝对地址跳转指令时,直接从所述第一级指令cache中获取所述第二指令行数据;所述第二指令行数据包括所述第二目的地址处指令的指令行数据。

23、在一些实施方式中,还包括:

24、接收模块,用于接收所述指令流水线下发的获取所述目标指令的取指请求;

25、第一查找模块,用于根据所述取指请求,在所述第一级指令cache中的各指令行中查找是否存在包含所述目标指令的指令行数据;

26、第二查找模块,用于当所述第一级指令cache中不存在包含所述目标指令的指令行数据时,逐级向下一级指令cache中查找包含所述目标指令的指令行数据,直至找到包含所述目标指令的指令行数据;

27、反馈模块,用于将包含所述目标指令的指令行数据逐级向上反馈至所述第一级指令cache。

28、在一些实施方式中,还包括:第二发送模块,用于当所述第一级指令cache中存在所述目标指令时,将包含所述目标指令的指令行数据发送给所述指令流水线,使所述指令流水线执行所述目标指令。

29、与现有技术相比,本发明至少具有以下一项有益效果:

30、(1)本发明在绝对地址跳转指令被执行之前,提前将后续指令流水线有可能会执行到的绝对地址跳转指令的目的地址所在的指令行数据取至第一级指令cache中,这样等到取指部件需要执行绝对地址跳转指令时,第一级指令cache可以提供相应的指令,有利于提高处理器的访问性能。

31、(2)本发明赋予指令cache一定的译码功能,当检测到绝对地址跳转指令时,就将其对应的目的地址解析出来,并向下级指令cache发出获取目的地址所在指令行数据的请求,这样等到取指部件开始执行绝对地址跳转指令时,第一级指令cache能够尽快将该绝对地址跳转指令的目的地址所在的指令行数据提供给指令流水线,避免第一级cache中出现指令失效而引起取指部件等待,能够加速指令cache访问指令的速度。

32、(3)本发明的跳转指令预取过程在第一级指令cache中进行,能够对下级指令cache发送的指令行数据进行解析,并主动向下级指令cache发出目标地址的预取请求,进一步加快取指的过程。

- 还没有人留言评论。精彩留言会获得点赞!