复用JTAG调试通道调试CPU核的处理器及应用方法与流程

本发明涉及芯片调试,具体涉及一种复用jtag调试通道调试cpu核的处理器及应用方法。

背景技术:

1、随着应用对高性能需求的增加,单核处理器芯片已经越来越无法满足应用需求,多核处理器芯片应时而生,但是无论是芯片是单核处理器还是多核处理器,其在设计、制造、封装和应用过程中都有可能存在问题,因此为了保证芯片的正确性,还必须对芯片进行调试。jtag(joint test action group,联合测试工作组)接口主要用于芯片内部测试,现在绝大多数的高级器件如dsp、cpu ip、fpga等都支持jtag协议,jtag接口已是soc芯片中不可或缺的一部分。

2、在现有技术中,单核处理器和多核处理器通常均是采用jtag接口对其内部电路逻辑进行访问以便对其进行调试。jtag是一种用于芯片内部调试的且兼容ieee1149.1的国际标准化协议,标准的jtag接口一般具有5个信号,分别是:复位信号trst、模式选择信号tms、时钟信号tck、数据输入信号tdi和数据输出信号tdo。jtag对芯片进行调试的基本原理是,在芯片中定义实现一个测试访问端口tap(test access port),jtag仿真器通过测试访问端口tap对芯片内部进行测试。

3、公布号为cn101154184a的中国专利文献公开了一种通过jtag接口对微处理器进行调试的现有技术,虽然在该现有技术中所介绍了的调试方法,其通过jtag接口调试的对象是微处理器,但是该现有技术也仅仅体现了通过jtag接口对单处理器进行调试的基本方法:通过配置jtag接口,利用外部上层软件使用标准的或者扩展的标准tap命令访问仿真调试模块,执行调试命令,从而达到调试的目的。

4、对于异构多核处理器而言,由于其包含多个cpu和/或dsp等单核处理器,每个单核处理器均设置有属于自己的调试访问端口tap,各个单处理器之间还通过外围逻辑电路连接,这些都导致多核处理器的联合调试变得复杂。现有技术中,存在一种采用串联方式对多核处理器进行调试的方法,多核处理器包含多个处理器核(也称ip核),每个处理器核均设置有属于自己的测试访问端口tap。各个处理器核的测试访问端口tap采用菊花链式的连接方式,即上一级测试访问端口tap的数据输出信号tdo接入下级测试访问端口tap的数据输入信号tdi,jtag仿真器的时钟信号tck、模式选择信号tms、复位信号trst接入所有的tap。

5、公布号为cn102103535a的中国专利文献公开了一种通过芯片级tap以及其他支撑模块实现通过单一jtag接口对多处理器进行调试的现有技术。该方法虽然巧妙的在不改变标准的tap接口和标准的仿真器端口设计的情况下,仅通过增加一个芯片的tap以及其他支撑模块实现了通过单一jtag接口对多核处理器进行调试的方法。

6、但是,无论是采用jtap串联方式还是并行方式对多核处理器进行调试,其主体思想仍是:通过配置jtag接口,利用外部上层软件使用标准的或者扩展的标准tap命令访问仿真调试模块,选择待测处理器核,执行调试命令,从而达到调试的目的。但是,在jtag接口不可用或者有其他用途的情况下,则无法实现对多核处理器进行调试。而且,在异构多核soc芯片中集成了不同体系架构的cpu核时,通常这些异构的cpu核作为主机只能访问芯片上的可寻址空间和各自的内部私有空间或资源(包括私有memory,寄存器文件、控制寄存器、pc指针等),不能访问其他核的私有空间或资源(包括私有memory,寄存器文件、控制寄存器、pc指针等),更别说控制核内指令流水线的运行、暂停和单步了。

技术实现思路

1、本发明要解决的技术问题:针对现有技术的上述问题,提供一种复用jtag调试通道调试cpu核的处理器及应用方法,本发明能够不通过配置jtag接口而是直接通过编写程序配置一系列的寄存器后复用jtag调试逻辑通过总线控制实现对cpu核的调试,同时能够支持访问自研的cpu核的私有空间或资源。

2、为了解决上述技术问题,本发明采用的技术方案为:

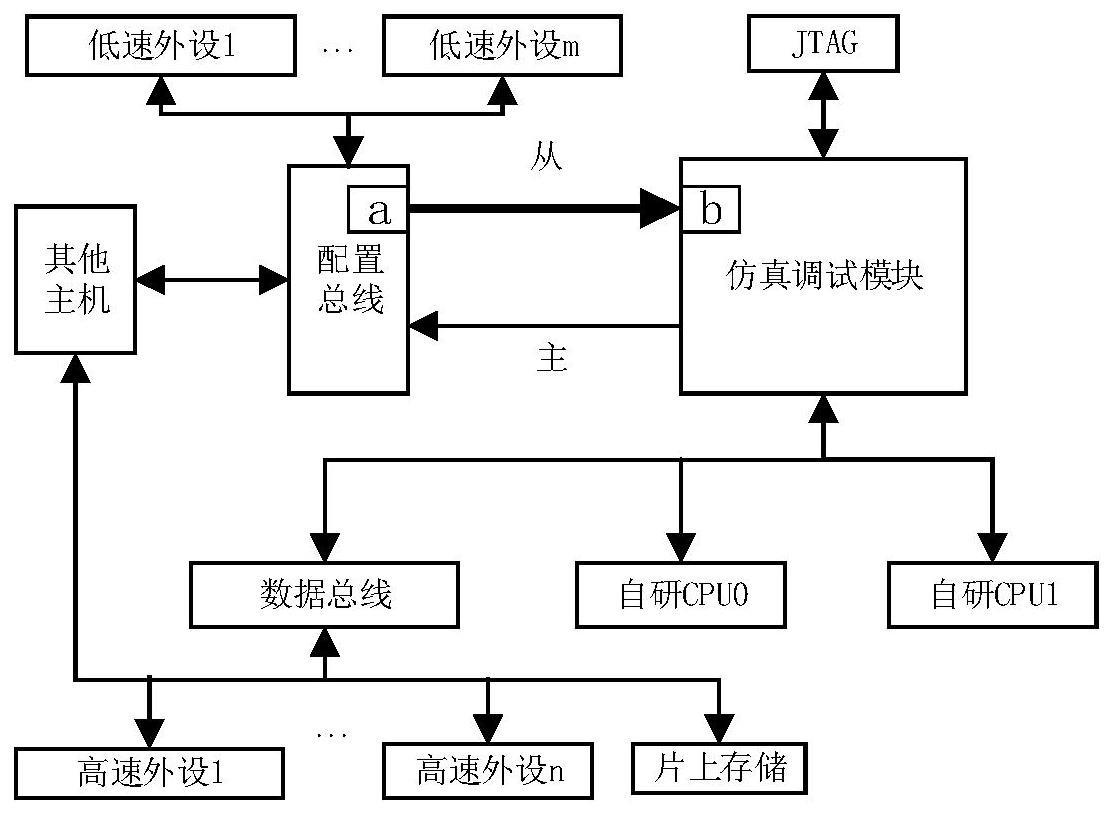

3、一种复用jtag调试通道调试cpu核的处理器,包括jtag接口、仿真调试模块、配置总线、片内主机模块以及cpu核,所述jtag接口与仿真调试模块相连,所述仿真调试模块通过配置总线与片内主机模块相连,所述仿真调试模块通过数据总线与cpu核相连,所述配置总线中包含用于访问仿真调试模块的主机接口,所述仿真调试模块中包含与主机接口相连的从机接口和对应的译码模块以用于被片内主机模块访问,且所述仿真调试模块内还包含一组寄存器和选择器以用于实现jtag接口、片内主机模块对仿真调试模块的复用控制,在不使用jtag接口的情况下通过片内主机模块利用寄存器和选择器复用仿真调试模块实现对cpu核的调试功能以及访问cpu核的私有空间或资源。

4、可选地,所述一组寄存器和选择器中的寄存器包括:

5、使能寄存器pe,用于表示片内主机模块调试的全局使能;

6、选择寄存器pj,用于表示jtag调试和片内主机模块调试的通道占用状态;

7、调试指令寄存器,用于存放调试指令;

8、调试数据寄存器,用于存放调试数据;

9、状态寄存器,用于存放调试状态。

10、可选地,所述使能寄存器pe包括第一使能寄存器pe1和第二使能寄存器pe2,所述第一使能寄存器pe1和第二使能寄存器pe2均用于表示其他主机调试的全局使能,且只有第一使能寄存器pe1等于第一设定值、第二使能寄存器pe2等于第二设定值同时成立时才允许片内主机模块利用寄存器和选择器复用仿真调试模块实现对cpu核的调试功能以及访问cpu核的私有空间或资源。

11、可选地,所述调试指令寄存器包括调试指令寄存器0和调试指令寄存器1,调试指令寄存器0用于存放调试指令的低32位,调试指令寄存器1用于存放调试指令的高16位;所述状态寄存器包括状态寄存器0和状态寄存器1,状态寄存器0用于存放调试状态的低32位,状态寄存器1用于存放调试状态的高16位。

12、可选地,所述一组寄存器和选择器中的选择器包括:第一选择器,用于选择通过片内主机模块通过配置从机接口写入还是通过jtag接口扫入调试指令;第二选择器,用于选择将收集的状态返回至jtag接口还是产生调试请求的片内主机模块;第三选择器,用于选择将收集的状态返回至jtag接口还是产生调试请求的片内主机模块;第四选择器,用于选择通过片内主机模块通过配置从机接口写入还是通过jtag接口扫入调试数据。

13、可选地,所述译码模块包括:简单译码模块,用于对仿真调试模块中tck时钟域下的指令寄存器中锁存的指令进行译码,以产生对使能寄存器pe、选择寄存器pj和仿真调试模块中系统时钟域下指令寄存器的访问控制信号;配置总线从机接口寄存器译码模块,用于对片内主机模块产生的总线请求进行译码,以产生对使能寄存器pe、选择寄存器pj、仿真调试模块中系统时钟域下的指令寄存器和数据寄存器的访问控制信号。

14、可选地,所述cpu核的数量为多个。

15、此外,本发明还提供一种计算机设备,包括相互连接的微处理器和存储器,所述微处理器为所述的复用jtag调试通道调试cpu核的处理器。

16、此外,本发明还提供一种所述的复用jtag调试通道调试cpu核的处理器的应用方法,包括:

17、s101,打开调试使能:配置第一使能寄存器pe1使能打开并向其写入第一设定值,配置第二使能寄存器pe2使能打开并向其写入第二设定值,若第一使能寄存器pe1等于第一设定值、第二使能寄存器pe2等于第二设定值同时成立则跳转步骤s102;

18、s102,在不使用jtag接口的情况下通过片内主机模块利用寄存器和选择器复用仿真调试模块实现对指定的cpu核的指定调试功能或者访问指定的cpu核的私有空间或资源,包括:不断读选择寄存器pj的状态,等待其值变为01,值变为01表示片内主机模块占用jtag调试通道,当值变为01后,根据片内主机模块针对指定的cpu核所需执行的流水线暂停的调试操作,分别向调试指令寄存器0和调试指令寄存器1写入调试命令、向调试数据寄存器写入调试数据;然后读取状态寄存器0和状态寄存器1获得调试状态和调试数据以判断指定的cpu核是否调试通过或者访问指定的cpu核的私有空间或资源是否成功;

19、s103,关闭调试使能:配置第一使能寄存器pe1使能关闭并向其写入全0,配置第二使能寄存器pe2使能关闭并向其写入全0。

20、可选地,步骤s102中指定调试功能包括控制指定的cpu核执行流水线暂停、控制指定的cpu核流水线单步以及控制指定的cpu核流水线运行中的部分或全部;

21、所述控制指定的cpu核执行流水线暂停包括:不断读选择寄存器pj的状态,等待其值变为01,值变为01表示片内主机模块占用jtag调试通道,当值变为01后,根据片内主机模块针对指定的cpu核所需执行的流水线暂停的调试操作,分别向调试指令寄存器0和调试指令寄存器1写入调试命令、向调试数据寄存器写入调试数据;然后读取状态寄存器0和状态寄存器1获得调试状态和调试数据以判断指定的cpu核是否调试通过,若根据调试状态和调试数据判定指定的cpu核执行流水线已经暂停、且程序计数器pc指针不动,则判定指定的cpu核执行流水线暂停的调试通过,否则判定指定的cpu核执行流水线暂停的调试不通过;释放jtag调试通道,向选择寄存器pj写入全0;

22、所述控制指定的cpu核流水线单步包括:不断读选择寄存器pj的状态,等待其值变为01,当值变为01后,根据片内主机模块针对指定的cpu核所需执行的流水线单步的调试操作,分别向调试指令寄存器0和调试指令寄存器1写入调试命令、向调试数据寄存器写入调试数据;然后读取状态寄存器0和状态寄存器1获得调试状态和调试数据以判断指定的cpu核是否调试通过,若根据调试状态和调试数据判定指定的cpu核执行流水线已经暂停、且程序计数器pc指针走了一拍,则判定指定的cpu核执行流水线单步的调试通过,否则判定指定的cpu核执行流水线单步的调试不通过;释放jtag调试通道,向选择寄存器pj写入全0;

23、所述控制指定的cpu核流水线运行包括:不断读选择寄存器pj的状态,等待其值变为01,当值变为01后,根据片内主机模块针对指定的cpu核所需执行的流水线运行的调试操作,分别向调试指令寄存器0和调试指令寄存器1写入调试命令、向调试数据寄存器写入调试数据;然后读取状态寄存器0和状态寄存器1获得调试状态和调试数据以判断指定的cpu核是否调试通过;释放jtag调试通道,向选择寄存器pj写入全0。

24、可选地,步骤s102中访问指定的cpu核的私有空间或资源包括读指定的cpu核的片内通用寄存器、写指定的cpu核的片内通用寄存器或、读指定的片内外设资源、写指定的片内外设资源、读片上存储、写片上存储中的部分或全部;

25、所述读指定的cpu核的片内通用寄存器包括:不断读选择寄存器pj的状态,等待其值变为01,当值变为01后,根据片内主机模块针对指定的cpu核所需执行的读指定的cpu核的片内通用寄存器的调试操作,分别向调试指令寄存器0和调试指令寄存器1写入调试命令、向调试数据寄存器写入调试数据;然后读取状态寄存器0和状态寄存器1获得调试状态和调试数据以判断访问读指定的cpu核的片内通用寄存器是否成功;释放jtag调试通道,向选择寄存器pj写入全0;

26、所述写指定的cpu核的片内通用寄存器包括:不断读选择寄存器pj的状态,等待其值变为01,当值变为01后,根据片内主机模块针对指定的cpu核所需执行的写指定的cpu核的片内通用寄存器的调试操作,分别向调试指令寄存器0和调试指令寄存器1写入调试命令、向调试数据寄存器写入调试数据;然后读取状态寄存器0和状态寄存器1获得调试状态和调试数据以判断写指定的cpu核的片内通用寄存器是否成功;释放jtag调试通道,向选择寄存器pj写入全0;

27、所述读指定的片内外设资源包括:不断读选择寄存器pj的状态,等待其值变为01,当值变为01后,根据片内主机模块针对指定的cpu核所需执行的述读指定的片内外设资源的调试操作,分别向调试指令寄存器0和调试指令寄存器1写入调试命令、向调试数据寄存器写入调试数据;然后读取状态寄存器0和状态寄存器1获得调试状态和调试数据以判断访问读指定的片内外设资源是否成功;释放jtag调试通道,向选择寄存器pj写入全0;

28、所述写指定的片内外设资源包括:不断读选择寄存器pj的状态,等待其值变为01,当值变为01后,根据片内主机模块针对指定的cpu核所需执行的写指定的片内外设资源的调试操作,分别向调试指令寄存器0和调试指令寄存器1写入调试命令、向调试数据寄存器写入调试数据;然后读取状态寄存器0和状态寄存器1获得调试状态和调试数据以判断写指定的片内外设资源是否成功;释放jtag调试通道,向选择寄存器pj写入全0;

29、所述读片上存储包括:不断读选择寄存器pj的状态,等待其值变为01,当值变为01后,根据片内主机模块针对指定的cpu核所需执行的读片上存储的调试操作,分别向调试指令寄存器0和调试指令寄存器1写入调试命令、向调试数据寄存器写入调试数据;然后读取状态寄存器0和状态寄存器1获得调试状态和调试数据以判断读片上存储是否成功;释放jtag调试通道,向选择寄存器pj写入全0;

30、所述写片上存储包括:不断读选择寄存器pj的状态,等待其值变为01,当值变为01后,根据片内主机模块针对指定的cpu核所需执行的写片上存储的调试操作,分别向调试指令寄存器0和调试指令寄存器1写入调试命令、向调试数据寄存器写入调试数据;然后读取状态寄存器0和状态寄存器1获得调试状态和调试数据以判断写片上存储是否成功;释放jtag调试通道,向选择寄存器pj写入全0。

31、和现有技术相比,本发明主要具有下述优点:

32、1、本发明包括述配置总线中包含用于访问仿真调试模块的主机接口,仿真调试模块中包含与主机接口相连的从机接口和对应的译码模块以用于被片内主机模块访问,且仿真调试模块内还包含一组寄存器和选择器以用于实现jtag接口、片内主机模块对仿真调试模块的复用控制,本发明能够在jtag接口不可用或者有其他用途的情况下,通过程序配置一系列的寄存器后复用jtag调试逻辑通过总线控制实现对自研的cpu核的调试功能。

33、2、本发明仿真调试模块内还包含一组寄存器和选择器以用于实现jtag接口、片内主机模块对仿真调试模块的复用控制,因此片内主机模块通过程序配置的寄存器后通过总线控制复用jtag调试通道访问自研的cpu核的私有空间或资源。

34、3、本发明为处理器对调试功能做了冗余设计,使用更加灵活方便。

- 还没有人留言评论。精彩留言会获得点赞!