一种快速连接MOS管脚和输入/输出引脚的布线方法与流程

本发明涉及集成电路设计,尤其涉及一种快速连接mos管脚和输入/输出引脚的布线方法。

背景技术:

1、传统的集成电路版图主要依靠手工设计,随着工艺节点的提升和设计复杂度的增加,集成电路版图规模愈发庞大,若版图仍然依赖纯手工进行设计,则会耗费大量时间、精力,降低设计效率。为了进一步提升版图设计的效率,让工程师将更多精力集中在创造性设计上,计算机辅助设计技术不可或缺。

2、在某些模拟电路版图设计场景中,i/o pin(输入/输出引脚)需要与包围在其中的mos管的各端(源极、漏极、栅极)相连接。布线时需要考虑设计规则约束,并尽可能保持走线整齐美观。

3、目前只能依靠手工操作来实现mos pin(mos管脚)和i/o pin(输入/输出引脚)的布线,当多个i/o cell和mos cell呈阵列式排布时,需要布线的mos cell和i/o cell数量较多,手工布线的方法效率低下,需要耗费大量的时间和精力。

技术实现思路

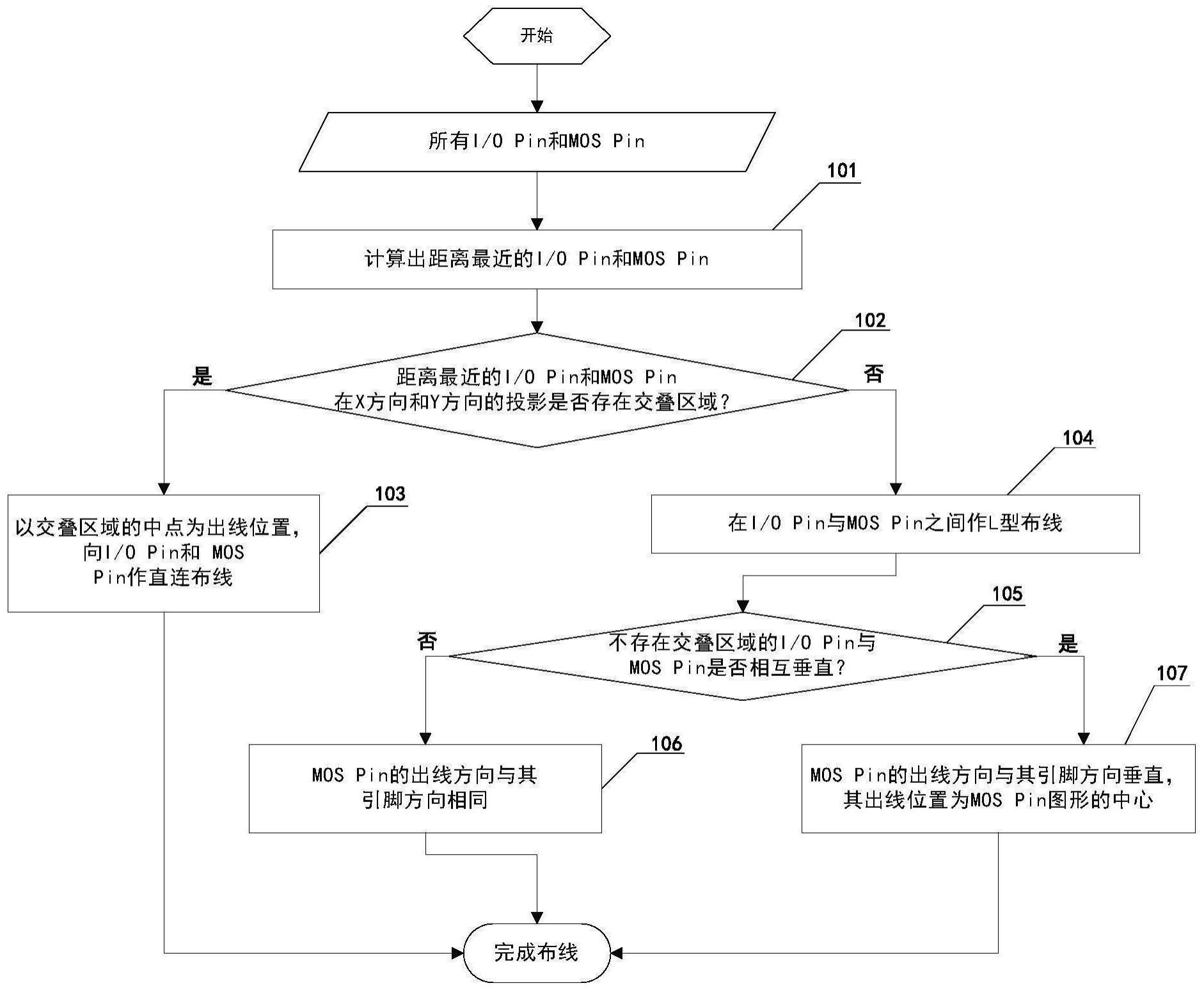

1、为了解决现有技术的缺陷,本发明的目的在于提供一种快速连接mos管脚和输入/输出引脚的布线方法,根据距离最近的一对i/o pin和mos pin在x方向和y方向的投影上是否存在交叠区域选择直连或l型的布线模式,实现借助eda工具快速完成对指定cell(单元)的布线,节约时间,提升版图设计效率。

2、为了实现上述目的,本发明提供的快速连接mos pin和阵列式i/o pin的布线方法,包括以下步骤:

3、获取输入/输出引脚和mos管脚的中心点坐标,计算出距离最近的输入/输出引脚和mos管脚;

4、判断所述距离最近的输入/输出引脚和mos管脚是否存在交叠区域;

5、若存在交叠区域,以所述交叠区域的中心为出线位置,根据预先设置的布线层和布线宽度,作直连布线连接所述距离最近的输入/输出引脚和mos管脚;

6、若不存在交叠区域,根据预先设置的布线层和布线宽度,作l型布线连接所述距离最近的输入/输出引脚和mos管脚。

7、进一步地,所述输入/输出引脚或所述mos管脚呈阵列排布。

8、进一步地,所述判断所述距离最近的输入/输出引脚和mos管脚是否存在交叠区域的步骤,还包括:将距离最近的输入/输出引脚图形和mos管脚图形分别在x方向、y方向上做投影,判断所述mos管脚和所述输入/输出引脚是否存在交叠区域。

9、进一步地,所述若不存在交叠区域,根据预先设置的布线层和布线宽度,作l型布线连接所述距离最近的输入/输出引脚和mos管脚的步骤,进一步包括:

10、选取输入/输出引脚图形上距离mos管脚最近的边界,将所述边界向内偏移二分之一的布线宽度之处作为第一出线位置;

11、根据输入/输出引脚图形的水平长度与竖直长度的大小关系确定第一出线方向;

12、以mos管脚图形上任意位置作为第二出线位置,与所述第一出线方向垂直的方向作为第二出线方向;

13、根据预先设置的布线层和布线宽度,自所述第一出线位置沿所述第一出线方向向所述mos管脚作第一布线,自所述第二出线位置沿所述第二出线方向向所述输入/输出引脚作第二布线,所述第一布线与所述第二布线相连接,形成l型布线图形。

14、进一步地,所述根据输入/输出引脚图形的水平长度与竖直长度的大小关系确定第一出线方向的步骤,包括:比较所述输入/输出引脚图形的水平长度与竖直长度,若所述水平长度大于等于所述竖直长度,确定所述第一出线方向为竖直方向,否则确定为水平方向。

15、进一步地,还包括:判断输入/输出引脚与mos管脚是否相互垂直,若相互垂直,则以mos管脚图形的中心作为所述第二出线位置。

16、进一步地,所述选取输入/输出引脚图形上距离mos管脚最近的边界的步骤,包括:分别计算输入/输出引脚图形上各个边界中点与mos管脚图形中心点的距离,选取距离最小的边界中点所在的边界。

17、更进一步地,还包括:待布线完成后,根据连接性关系,获取布线连接得到的所有物体;判断所有所述物体是否属于本次布线中待连接的引脚图形或布线过程中创建的物理图形线、逻辑路径线段,若存在任一物体不属于,则认为本次布线的结果发生了短路。

18、为实现上述目的,本发明还提供一种电子设备,包括存储器、处理器,以及存储在所述存储器中并可在所述处理器上运行的计算机程序,所述处理器,用于执行所述存储器所存放的计算机程序,以实现如上所述的快速连接mos管脚和输入/输出引脚的布线方法的步骤。

19、为实现上述目的,本发明还提供一种计算机可读存储介质,所述存储介质中存储有至少一条指令,所述指令由处理器加载并执行以实现如上所述的快速连接mos管脚和输入/输出引脚的布线方法的步骤。

20、本发明提供的快速连接mos管脚和输入/输出引脚的布线方法,与现有技术相比具有如下有益效果:

21、通过计算出距离最近的一对输入/输出引脚和mos管脚,根据两者在x方向和y方向的投影上是否存在交叠区域选择直连布线或l型布线的模式,按照直连布线或l型布线规则最终完成连线;该方法可以同时对在当前block(宏单元)区域下多个输入/输出引脚和mos管脚进行布线,且支持用户自定义布线层和宽度,在提升版图设计效率的同时也提高了易用性。

22、本发明的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本发明而了解。

技术特征:

1.一种快速连接mos管脚和输入/输出引脚的布线方法,包括以下步骤:

2.根据权利要求1所述的快速连接mos管脚和输入/输出引脚的布线方法,其特征在于,所述输入/输出引脚或所述mos管脚呈阵列排布。

3.根据权利要求1所述的快速连接mos管脚和输入/输出引脚的布线方法,其特征在于,所述判断所述距离最近的输入/输出引脚和mos管脚是否存在交叠区域的步骤,还包括:将距离最近的输入/输出引脚图形和mos管脚图形分别在x方向、y方向上做投影,判断所述mos管脚和所述输入/输出引脚是否存在交叠区域。

4.根据权利要求1所述的快速连接mos管脚和输入/输出引脚的布线方法,其特征在于,所述若不存在交叠区域,根据预先设置的布线层和布线宽度,作l型布线连接所述距离最近的输入/输出引脚和mos管脚的步骤,进一步包括:

5.根据权利要求4所述的快速连接mos管脚和输入/输出引脚的布线方法,其特征在于,所述根据输入/输出引脚图形的水平长度与竖直长度的大小关系确定第一出线方向的步骤,包括:比较所述输入/输出引脚图形的水平长度与竖直长度,若所述水平长度大于等于所述竖直长度,确定所述第一出线方向为竖直方向,否则确定为水平方向。

6.根据权利要求4所述的快速连接mos管脚和输入/输出引脚的布线方法,其特征在于,还包括:判断输入/输出引脚与mos管脚是否相互垂直,若相互垂直,则以mos管脚图形的中心作为所述第二出线位置。

7.根据权利要求4所述的快速连接mos管脚和输入/输出引脚的布线方法,其特征在于,所述选取输入/输出引脚图形上距离mos管脚最近的边界的步骤,包括:分别计算输入/输出引脚图形上各个边界中点与mos管脚图形中心点的距离,选取距离最小的边界中点所在的边界。

8.根据权利要求1所述的快速连接mos管脚和输入/输出引脚的布线方法,其特征在于,还包括:待布线完成后,根据连接性关系,获取布线连接得到的所有物体;判断所有所述物体是否属于本次布线中待连接的引脚图形或布线过程中创建的物理图形线、逻辑路径线段,若存在任一物体不属于,则认为本次布线的结果发生了短路。

9.一种电子设备,包括存储器、处理器,以及存储在所述存储器中并可在所述处理器上运行的计算机程序,其特征在于,所述处理器,用于执行所述存储器所存放的计算机程序,以实现权利要求1-8任一项所述的方法。

10.一种计算机可读存储介质,其特征在于,所述存储介质中存储有至少一条指令,所述指令由处理器加载并执行以实现权利要求1-8任一项所述的方法。

技术总结

一种快速连接MOS管脚和输入/输出引脚的布线方法,包括以下步骤:获取输入/输出引脚和MOS管脚的中心点坐标,计算出距离最近的输入/输出引脚和MOS管脚;判断所述距离最近的输入/输出引脚和MOS管脚是否存在交叠区域;若存在交叠区域,以所述交叠区域的中心为出线位置,根据预先设置的布线层和布线宽度,作直连布线连接所述距离最近的输入/输出引脚和MOS管脚;若不存在交叠区域,根据预先设置的布线层和布线宽度,作L型布线连接所述距离最近的输入/输出引脚和MOS管脚。本发明根据距离最近的一对I/O Pin和MOS Pin在X方向和Y方向的投影上是否存在交叠区域选择直连或L型布线模式,实现快速完成对指定单元的布线,提升版图设计效率。

技术研发人员:李海博,张亚东

受保护的技术使用者:北京华大九天科技股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!