一种时钟移相方法和装置与流程

本发明涉及集成电路,特别是涉及一种时钟移相方法和装置。

背景技术:

1、emmc(embedded multi media card,嵌入式多媒体卡)为mmc(multimedia cardassociation,多媒体存储卡协会)协会所订立的、主要是针对手机或平板电脑等产品的内嵌式存储器标准规格。emmc的一个明显优势是在封装中集成了一个控制器,用于提供标准接口并管理闪存,使得手机厂商就能专注于产品开发的其它部分,并缩短向市场推出产品的时间。

2、emmc是当前常用的数据通信接口,广泛应用于各种芯片之间的通信,但是由于emmc传输速度高,host controller(主机控制器)与emmc之间通信使用的数字信号在高速传输过程中容易受到工艺、pad(管脚输入输出)延迟、pcb(printed circuit board,印制电路板)布线延迟等因素影响,导致信号出现相位偏移。这种相位偏移可能导致数据采样不正确,最终导致host或emmc无法正常工作。

3、鉴于此,克服该现有技术所存在的缺陷是本技术领域亟待解决的问题。

技术实现思路

1、本发明要解决的技术问题是现有技术中host与媒体卡之间通信所使用的数字信号在高速传输过程中容易受到工艺、pad延迟、pcb布线延迟等因素影响,导致信号出现相位偏移,影响host或媒体卡的正常工作。

2、本发明采用如下技术方案:

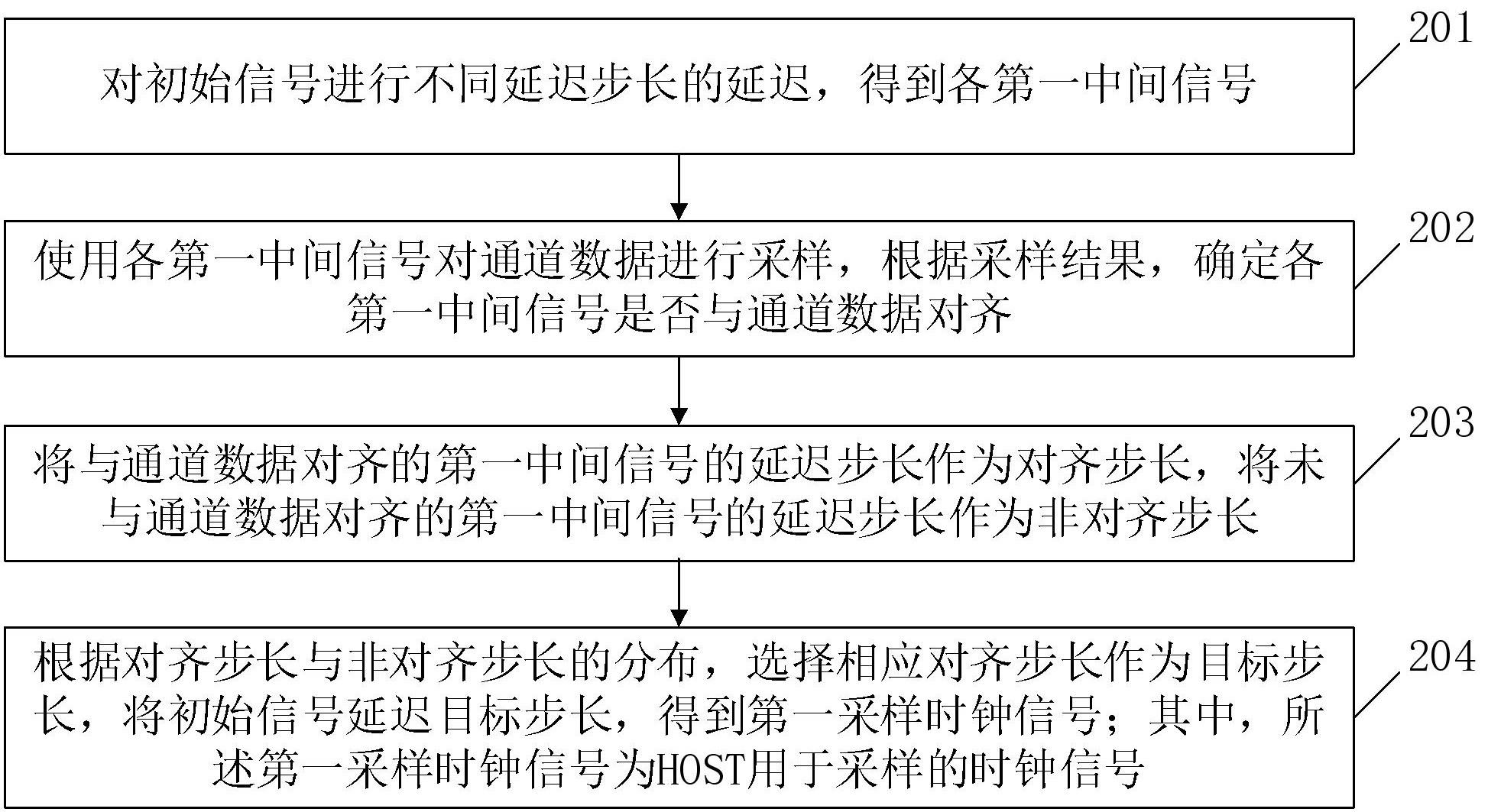

3、第一方面,本发明提供了一种时钟移相方法,包括:

4、对初始信号进行不同延迟步长的延迟,得到各第一中间信号;

5、使用各第一中间信号对通道数据进行采样,根据采样结果,确定各第一中间信号是否与通道数据对齐;

6、将与通道数据对齐的第一中间信号的延迟步长作为对齐步长,将未与通道数据对齐的第一中间信号的延迟步长作为非对齐步长;

7、根据对齐步长与非对齐步长的分布,选择相应对齐步长作为目标步长,将初始信号延迟目标步长,得到第一采样时钟信号;其中,所述第一采样时钟信号为host用于采样的时钟信号。

8、优选的,所述根据对齐步长与非对齐步长的分布,选择相应对齐步长作为目标步长,具体包括:

9、将连续多个对齐步长所在的步长区间划分为对齐区间,将连续多个非对齐步长所在的步长区间划分为非对齐区间;

10、找到完整对齐区间,选择位于该完整对齐区间中心的对齐步长作为目标步长;其中,所述完整对齐区间为位于两个非对齐区间之间的对齐区间。

11、优选的,若无法找到完整对齐区间,则查找非对齐区间前后的对齐区间,分别作为前区间和后区间;

12、若仅存在前区间或仅存在后区间,则在前区间中或后区间中选择相应的延迟步长作为目标延迟步长;

13、若存在前区间和后区间,则使用前区间的区间长度与后区间的区间长度,计算得到目标长度;

14、以非对齐区间后目标长度所在位置的延迟步长作为目标步长。

15、优选的,所述在前区间中或后区间中选择相应的延迟步长作为目标延迟步长,具体包括:

16、选择位于前区间中心的对齐步长或后区间中心的对齐步长作为目标延迟步长。

17、优选的,所述使用前区间的区间长度与后区间的区间长度,计算得到目标长度,具体包括:

18、以前区间的区间长度与后区间的区间长度的平均值作为目标长度。

19、优选的,所述方法还包括:

20、按照每间隔预设时间延迟步长增加第一预设步长的方式,对初始信号进行延迟,依次得到不同延迟的第二中间信号;

21、在初始信号的上升沿或下降沿采集相应第二中间信号的电平,生成超前进位信号;

22、以超前进位信号产生上升沿时所对应的延迟步长以及超前进位信号产生下降沿时所对应的延迟步长,形成延迟步长区间;

23、以所述延迟步长区间的长度除以预设值,得到目标延迟步长;

24、使用所述目标延迟步长对ds信号进行延迟,得到第二采样时钟信号;其中,所述第二采样时钟信号为host在相应模式下用于辅助采样的时钟信号。

25、优选的,当完整对齐区间的长度小于预设长度时,使用各第一中间信号对通道数据进行采样,根据采样结果,确定各通道数据的数据周期划分;

26、根据各通道数据的数据周期划分,按照不同的n值,在每个n值下将数据周期延迟小的n个通道数据划分为第一通道数据,将数据周期延迟大的num-n个通道数据划分为第二通道数据,得到对应n值下的第一通道数据和第二通道数据;其中,n大于1且n小于num,num为通道数量。

27、找到每个n值下,第一通道数据的数据周期维持不变且均为同一数据周期时所对应的各第一步长区间,计算各第一步长区间的长度;

28、以长度最长的第一步长区间中心的延迟步长作为第一目标延迟步长,以长度最长的第一步长区间所对应的n值作为最终的n值,以使用该最终的n值下划分所得的第一通道数据为第一目标数据,以使用该最终的n值下划分所得的第二通道数据为第二目标数据,找到该第二目标数据的数据周期维持不变且均为同一数据周期时所对应的第二步长区间;

29、对初始信号进行第一目标延迟步长得到第一目标采样信号,以第二步长区间中心的延迟步长作为第二目标延迟步长,对初始信号进行第二目标延迟步长得到第二目标采样信号,使用第一目标采样信号对第一目标数据进行采样,得到第一采样结果,使用第二目标采样信号对第二目标数据进行采样,得到第二采样结果,将第一采样结果和第二采样结果合并得到所有通道数据在相应数据周期的数据。

30、第二方面,本发明提供了一种时钟移相装置,包括控制模块和延迟模块;

31、所述延迟模块用于对初始信号进行不同延迟步长的延迟,得到各第一中间信号;

32、所述控制模块用于使用各第一中间信号对通道数据进行采样,根据采样结果,确定各第一中间信号是否与通道数据对齐;所述第一中间信号通过对初始信号进行延迟得到;将与通道数据对齐的第一中间信号的延迟步长作为对齐步长,将未与通道数据对齐的第一中间信号的延迟步长作为非对齐步长;根据对齐步长与非对齐步长的分布,选择相应对齐步长作为目标步长;

33、所述延迟模块还用于将初始信号延迟目标步长,得到第一采样时钟信号。

34、优选的,所述延迟模块包括至少一条延迟线路,每条延迟线路包括延迟组件和选择组件;

35、所述延迟组件用于将输入信号进行不同步长的延迟,得到不同延迟步长的延迟信号;

36、所述选择组件用于根据控制信号,选择性地将相应延迟的延迟信号输出,得到第一中间信号;其中,所述控制信号从所述选择组件的控制端输入。

37、优选的,所述装置还包括触发模块;

38、所述延迟组件用于按照每间隔预设时间延迟步长增加预设步长的方式,对初始信号进行延迟,依次得到不同延迟的第二中间信号;

39、所述触发模块用于在初始信号的上升沿或下降沿采集相应第二中间信号的电平,生成超前进位信号;

40、所述控制模块用于以超前进位信号产生上升沿时所对应的延迟步长以及超前进位信号产生下降沿时所对应的延迟步长,形成延迟步长区间;以所述延迟步长区间的长度除以预设值,得到目标延迟步长;

41、所述延迟模块还使用所述目标延迟步长对ds信号进行延迟,得到第二采样时钟信号;其中,所述第二采样时钟信号为host在相应模式下用于辅助采样的时钟信号。

42、本发明通过对初始信号进行不同步长的延迟,并确定相应延迟下采样确定信号与通道数据是否对齐,从而能够选定相应的延迟步长,使信号与数据对齐,从而确保后续host数据采样的正确工作。

- 还没有人留言评论。精彩留言会获得点赞!