一种可动态配置的交叉开关互连结构电路的制作方法

本发明涉及一种可动态配置的交叉开关互连结构电路,特别是面向嵌入式,对片内数据带宽、数据传递延迟要求高、数据传递路径复杂、集成的处理器核数较多的交叉开关片上互连结构。

背景技术:

1、随着多核处理器芯片的集成核数进一步增加,与之相关联的通信要求也越来越高。片上互连结构是多核系统研究的一个重要方向。当前片内互连主要可以分为总线互连、片上网络互连和交叉开关互连三种。

2、共享总线结构比较简单,当通信要求较小时,可实现较高的工作频率。但由于在单位时刻内只能有一个处理器核执行数据传输任务,当集成的处理器核数量增多时,该结构的延迟开销急剧增大,限制了带宽和吞吐率的提高。

3、片上网络互连是基于报文交换的网络拓扑结构,网络中每个节点与一个路由器相连接。路由器通过局部互连线与其他临近的路由器相连接。节点之间的通讯需要经过多个跳步实现,由于能够将全局互连线转化为局部互连线,因此能够有效的解决全局互连线所带来的功耗和传输线效应,但数据在片上网络传递时,传递延迟很大。因此,片上网络互连主要用于芯片中集成上百处理器核的情况。

4、交叉开关互连为各个处理器核之间提供最大可能的连接,相当于总线上的每个处理器核都拥有一组独立的总线结构。交叉开关互连是一种特殊的拓扑,拓扑结构中任意两个节点之间的连接不需要经过其他节点,任意两个节点之间的距离都是1。一个n*m的交叉开关互连具有n个输入端口和m个输出端口,每条输入线和所有的输出线都有一个交叉点,交叉点上有一个开关:用于选择闭合交叉点还是断开交叉点。为了保证输出的正确性,规定每个输出只能连接到一个输入,而一个输入可以连接到多个输出。交叉开关互连在硬件实现上简化为点到点连接,内部带宽很高,具备良好的可扩展性,能够提供大容量的数据交换。但目前的交叉开关互连设计,也存在明显的不足:

5、(1)它直接将发送方与特定的接受方连接起来,一旦建立连接,在数据传递整个过程中,连接关系保持不变,缺乏灵活性;

6、(2)它的作用仅是在一个输入与一个输出之间建立一条通道,让数据向下传递,不能够实现多个输入与一个输出、一个输入与多个输出、或者多个输入与多个输出之间建立灵活的传递通道;

7、本发明主要针对这两点不足进行改进。

技术实现思路

1、本发明解决的技术问题是:克服现有技术的不足,提出了一种可动态配置的交叉开关互连结构电路,适用于多核处理器芯片的交叉开关互连,能够使得交叉开关互连结构更加灵活、高效地实现数据传递。

2、本发明解决上述技术问题是通过如下技术方案予以实现的:

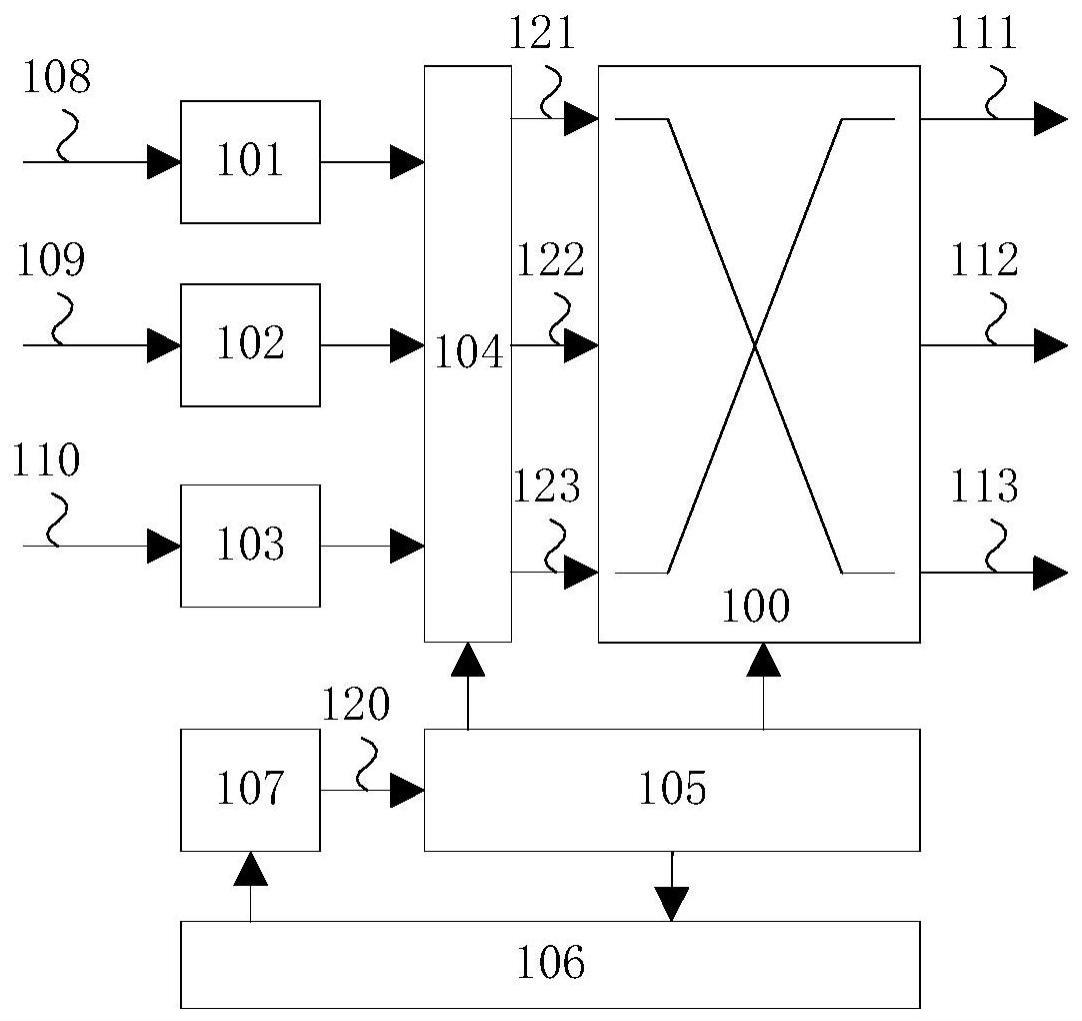

3、一种可动态配置的交叉开关互连结构电路,包括:第一输入缓存单元101、第二输入缓存单元102、第三输入缓存单元103、交叉开关矩阵100、输入控制单元104、配置缓存单元105、配置更新控制单元106和索引指针107;

4、第一输入缓存单元101、第二输入缓存单元102和第三输入缓存单元103采用fifo单元实现,分别将三路输入数据进行缓存;

5、输入控制单元104对配置缓存单元105输入的配置数据进行解析,在解析结果的指导下,读入三个输入缓存单元的数据并输出给交叉开关矩阵100;

6、配置缓存单元105在索引指针107的作用下,输出此索引指针对应位置寄存器的配置数据给交叉开关矩阵100、输入控制单元104、以及配置更新控制单元106;

7、配置更新控制单元106对配置缓存单元105输出的配置数据进行解析,解析结果对索引指针107进行更新;

8、索引指针107寄存的是下一时钟周期将从配置缓存单元中读出配置数据的地址信息;

9、交叉开关矩阵100在配置缓存单元105输出的配置数据控制下,对输入的数据进行多路选择,控制路径选通并输出。

10、进一步的,第一输入缓存单元101、第二输入缓存单元102和第三输入缓存单元103采用fifo单元实现;输入控制单元104、交叉开关矩阵100为组合逻辑单元,其中,交叉开关矩阵100采用多路选择器实现;配置缓存单元105是一个寄存器组,索引指针107为寄存器;配置更新控制单元106为时序逻辑单元。

11、进一步的,所述索引指针对应位置寄存器的配置数据包括交叉开关矩阵的开关控制信息、输入数据的选择信息、输出数据的整理信息、索引指针改变规则信息。

12、进一步的,所述配置更新控制单元106对配置缓存单元105输出的配置数据进行解析,解析结果对索引指针107进行更新,具体为:

13、(1)在解析过程中,首先判断配置数据是否有效,如果有效则进入步骤(2),否则解析过程暂停,等待配置数据有效;

14、(2)判断是否索引指针需要清零,如果要清零,则索引指针输出零,之后进入步骤(3);如果不需要清零,则索引指针数据直接输出;

15、(3)依据配置数据,判断是否要执行循环配置,如果执行循环配置,需要记录循环配置的次数,并与配置数据中指定的循环次数相比较,相等则输出此配置信息的下一地址给索引指针;不相等则输出此配置数据包含的配置起始索引地址给索引指针;如果不执行循环配置,则直接输出此配置信息的下一地址给索引指针。

16、进一步的,配置缓存单元105、索引指针107、配置更新控制单元106之间形成控制闭环,实现自动控制。

17、进一步的,所述配置缓存单元105包括配置缓存寄存器组205和配置寄存器200;

18、配置缓存寄存器组205包括多个配置缓存寄存器,配置缓存寄存器组205接收索引指针的输出作为地址信息输入,选择出配置缓存寄存器组中对应地址的数据,并写出到的配置寄存器200中;

19、配置寄存器200中的数据信息,作为配置数据输出。

20、进一步的,在配置寄存器200和配置缓存寄存器组205中,具有相同的配置数据格式,包括配置有效位210、配置复位有效位211、循环配置字段250、输出1选择配置字段220、输出2选择配置字段230、输出3选择配置字段240;

21、输出1选择配置字段、输出2选择配置字段、输出3选择配置字段定义的是交叉开关矩阵三路输出数据线传递规则;

22、配置有效位210,只有在此位为‘1’时,表示此寄存器中的配置数据有效;

23、配置复位有效位211,当此位为‘1’时,表示此寄存器中的配置数据是最后一条有效的配置数据,后面配置缓存寄存器中的数据无效;当此位为‘0’时,表示此寄存器中的配置数据不是最后一条有效的配置数据,后面配置缓存寄存器中的数据有效。

24、进一步的,输出1选择配置字段220控制交叉开关矩阵输出的第一路数据及其传递路径,包括输出1选择配置有效位221、输出1数据强制无效位222、输出1强时序有效位223以及输出1多路选择位224;

25、输出1选择配置有效位221,只有在此位为‘1’时,表示此输出1选择配置字段中的配置数据有效;

26、输出1数据强制无效位222,当此位为‘1’时,表示需要将交叉开关矩阵输出的第一路数据强制设置为全‘0’。

27、输出1强时序有效位223,当此位为‘1’时,表示只有在输出1完成一次数据传递后,配置更新控制单元才能够更新配置索引指针,读取接下来的配置缓存寄存器;

28、输出1多路选择位224,是一个位宽为2的二进制数据,定义了交叉开关矩阵的路径选择。

29、进一步的,输出2选择配置字段230控制交叉开关矩阵输出的第二路数据及传递路径,包括输出2选择配置有效位231、输出2数据强制无效位232、输出2强时序有效位233、输出2多路选择位234;

30、输出2选择配置有效位231,只有在此位为‘1’时,表示此输出2选择配置字段中的配置数据有效;输出2数据强制无效位232,当此位为‘1’时,表示需要将交叉开关矩阵输出的第二路数据强制设置为全‘0’;输出2强时序有效位233,当此位为‘1’时,表示只有在输出2完成一次数据传递后,配置更新控制单元才能够更新配置索引指针,读取接下来的配置缓存寄存器;输出2多路选择位234,是一个位宽为2的二进制数据,定义了交叉开关矩阵的路径选择;

31、输出3选择配置字段240控制交叉开关矩阵输出的第三路数据及传递路径,包括输出3选择配置有效位241、输出3数据强制无效位242、输出3强时序有效位243和输出3多路选择位244;

32、输出3选择配置有效位,只有在此位为‘1’时,表示此输出3选择配置字段中的配置数据有效;输出3数据强制无效位,当此位为‘1’时,表示需要将交叉开关矩阵输出的第三路数据强制设置为全‘0’;输出3强时序有效位,当此位为‘1’时,表示只有在输出3完成一次数据传递后,配置更新控制单元才能够更新配置索引指针,读取接下来的配置缓存寄存器;输出3多路选择位,是一个位宽为2的二进制数据,定义了交叉开关矩阵的路径选择。

33、进一步的,循环配置字段250包括循环配置有效位251、循环次数指定位252和循环起始地址253;

34、循环配置有效位251,只有在此位为‘1’时,表示此寄存器中的配置数据是需要执行循环配置的,此寄存器对应的地址是每次循环配置的结束地址;当配置寄存器中此位为‘1’时,需要配置更新控制单元106判断执行的循环次数,一旦达到循环次数指定位252指定的循环次数,则更新索引指针,使其指向后面的配置缓存寄存器;如果达到循环次数指定位252指定的循环次数,则更新配置索引指针,指向循环起始地址253指定的循环起始地址。

35、进一步的,本发明还提出一种多核处理器芯片,该芯片中集成多个处理器核,多个处理器核之间利用所述的可动态配置的交叉开关互连结构电路实现连接,所述的可动态配置的交叉开关互连结构电路的输入和输出分别与处理器核连接,实现处理器核间数据传递。

36、进一步的,本发明还提出一种片上系统芯片,在片上系统芯片中集成cpu、dsp和多个不同的ip核,利用所述的可动态配置的交叉开关互连结构电路连接多个ip核,此时所述的可动态配置的交叉开关互连结构电路的输入和输出分别与ip核连接,实现核间数据传递。

37、本发明与现有技术相比的优点在于:

38、(1)本发明的交叉开关互连结构,设计有配置缓存单元、配置索引指针、配置更新控制单元,配置更新控制单元能够对配置缓存单元的输入数据进行解析,解析后的结果赋给索引指针,通过索引指针,改变配置缓存单元的输出,从而改变交叉开关的输入与输出之间的传递路径。在配置缓存单元、配置索引指针、配置更新控制单元之间能够形成控制的闭环,达到自动控制的目的,不再需要外部干预;此外,由于配置索引指针能够单周期连续改变,因此,能够实现传递路径的动态改变,达到数据传输灵活、高效的目的。

39、(2)本发明的交叉开关互连结构,为了降低配置缓存单元的容量,在配置数据格式中,定义了循环配置字段,能够在一定范围内循环利用配置缓存中的数据,配置缓存单元的容量地减少,能够直接降低互连结构面积和功耗。

40、(3)本发明的交叉开关互连结构,针对每个输出的选择配置字段中,设计了强时序有效位,当此位为‘1’时,只有在此输出选择配置字段的多路选择位指定的输入数据有效、被传递输出后,才会更新配置缓存单元,否则处于等待指定输入数据的状态,通过此设计,能够对输入的数据按照一定的先后顺序输出,调整数据前后关系,简化后期对数据的处理工作。

41、(4)本发明的交叉开关互连结构,针对每个输出的选择配置字段中,设计了强制无效位,当此位为‘1’时,在此输出选择配置字段的多路选择位指定的输入数据会被丢掉,输出变为全‘0’,通过此设计,能够对输出的数据按照一定的规则进行整理,剔出一些数据,简化后期对数据的处理工作。

- 还没有人留言评论。精彩留言会获得点赞!