忽略时钟误差的数据交互方法、系统、终端及存储介质与流程

本发明属于通信,具体涉及一种忽略时钟误差的数据交互方法、系统、终端及存储介质。

背景技术:

1、在服务器机器中,不同芯片或板卡协同工作才能保证机器整体的正常运行,各部分间的数据交互必不可少。对于简单的电平信号,可以使用gpio直连的方式传递高低电平信号;但对于复杂的数据交互,通常使用总线方式进行数据传输。其中对于数据量大,实时性要求高的数据,会采用qpim、pcie、sas/sata、usb等高速串行总线进行;而对于数据量较小的交互场景,通常采用uart,i2c,spi等串行总线进行通信。

2、spi总线需要单独的时钟信号,硬件走线多;i2c总线为半双工方式,同一时刻数据传输是单向的。uart异步串口仅需两条走线,且能够实现双向数据传输,但数据交互的双方必须按照某一固定的波特率进行数据收发;这就要求双方必须有精度较高的工作时钟来保证波特率的误差在规定范围内,即必须搭配单独的晶振使用。

技术实现思路

1、针对现有技术的上述不足,本发明提供一种忽略时钟误差的数据交互方法、系统、终端及存储介质,以解决上述技术问题。

2、第一方面,本发明提供一种忽略时钟误差的数据交互方法,包括:

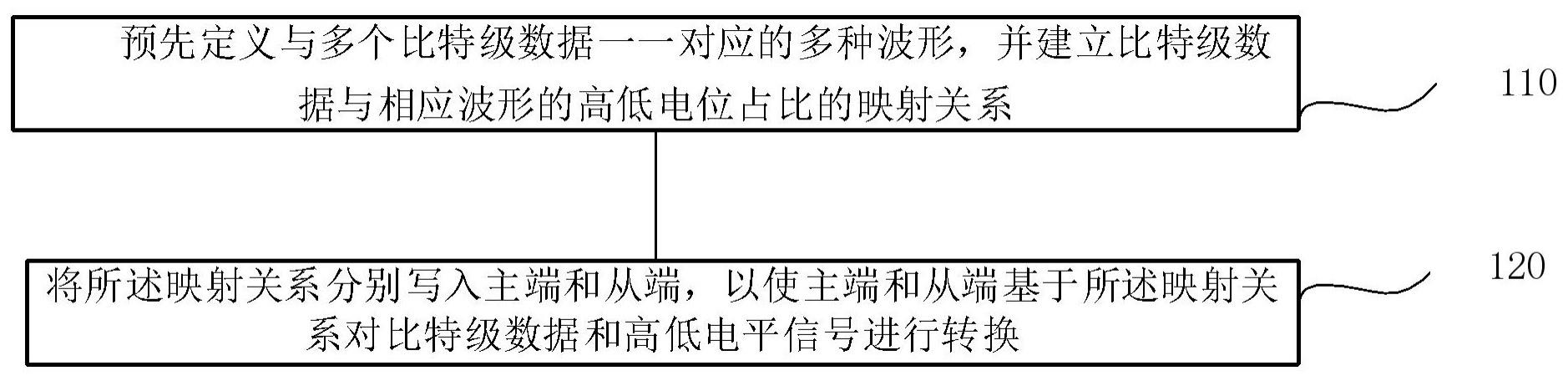

3、预先定义与多个比特级数据一一对应的多种波形,并建立比特级数据与相应波形的高低电位占比的映射关系;

4、将所述映射关系分别写入主端和从端,以使主端和从端基于所述映射关系对比特级数据和高低电平信号进行转换。

5、在一个可选的实施方式中,预先定义与多个比特级数据一一对应的多种波形,并建立比特级数据与相应波形的高低电位占比的映射关系,包括:

6、设置起始标志位对应的第一高低电位占比;

7、设置数据0对应的第二高低电位占比;

8、设置数据1对应的第三高低电位占比。

9、在一个可选的实施方式中,将所述映射关系分别写入主端和从端,包括:

10、设置数据解析规则,所述数据解析规则包括一帧数据的比特位数量和比特位的排列顺序;

11、设置波形约束条件,所述波形约束条件包括高低电平信号的单个周期由一段连续高电平和一段连续低电平组成,高电平在低电平之前;

12、将所述数据解析规则、波形约束条件,和比特级数据与高低电位占比的映射关系,固化为交互协议;

13、将所述交互协议写入主端芯片的寄存器和从端芯片的寄存器。

14、在一个可选的实施方式中,主端和从端基于所述映射关系对比特级数据和高低电平信号进行转换,包括:

15、主端基于所述映射关系将第一数据映射为第一高低电平信号,并将第一高低电平信号通过第一链路发送至从端,所述从端基于所述映射关系将接收的第一高低电平信号转换为第一数据;

16、从端基于所述映射关系将第二数据映射为第二高低电平信号,并将第二高低电平信号通过第二链路发送至从端,所述从端基于所述映射关系将接收的第二高低电平信号转换为第二数据。

17、在一个可选的实施方式中,基于所述映射关系将比特级数据转换为高低电平信号的方法,包括:

18、发送端基于数据解析规则解析待发送数据数据帧的比特位数值及排列顺序,依次基于所述映射关系将顺序排列的比特位数值转换为顺序排列的高低电位占比值,所述发送端为主端或从端;

19、发送端将顺序排列的高低电位占比值缓存为任务队列,并在任务队列最前端插入起始标志位对应的第一高低电位占比,得到执行队列;

20、发送端按照所述执行队列中的高低电位占比值依次调节高低电平信号在相应时间周期内的实际高低电位占比,所述高低电位占比为高电位和低单位在单个时间周期内的计数比;

21、接收端利用芯片内部晶振为接收的高低电平信号进行计数,获取高低电平信号每个周期的高低电平计数次数,所述接收到包括主端或从端;

22、接收端依次计算每个周期内的高低电平计数次数比例,得到高低电位占比;

23、接收端基于所述映射关系将依次排列的高低电位占比转换为比特级数据,并基于数据解析规则将所述比特级数据转换为数据帧。

24、在一个可选的实施方式中,利用芯片内部晶振为接收的高低电平信号进行计数的方法包括:

25、每收到依次内部晶振的计数信号,记录一次电位高低状态,得到高低电平计数次数。

26、在一个可选的实施方式中,接收端依次计算每个周期内的高低电平计数次数比例,得到高低电位占比,包括:

27、接收端基于波形约束条件将高低电平信号分割为多个单个周期;

28、依次计算多个单个周期内的高低电平计数次数比例。

29、第二方面,本发明提供一种忽略时钟误差的数据交互系统,包括:

30、规则定义模块,用于预先定义与多个比特级数据一一对应的多种波形,并建立比特级数据与相应波形的高低电位占比的映射关系;

31、信号转换模块,用于将所述映射关系分别写入主端和从端,以使主端和从端基于所述映射关系对比特级数据和高低电平信号进行转换。

32、在一个可选的实施方式中,规则定义模块包括:

33、第一设置单元,用于设置起始标志位对应的第一高低电位占比;

34、第二设置单元,用于设置数据0对应的第二高低电位占比;

35、第三设置单元,用于设置数据1对应的第三高低电位占比。

36、在一个可选的实施方式中,将所述映射关系分别写入主端和从端,包括:

37、设置数据解析规则,所述数据解析规则包括一帧数据的比特位数量和比特位的排列顺序;

38、设置波形约束条件,所述波形约束条件包括高低电平信号的单个周期由一段连续高电平和一段连续低电平组成,高电平在低电平之前;

39、将所述数据解析规则、波形约束条件,和比特级数据与高低电位占比的映射关系,固化为交互协议;

40、将所述交互协议写入主端芯片的寄存器和从端芯片的寄存器。

41、在一个可选的实施方式中,主端和从端基于所述映射关系对比特级数据和高低电平信号进行转换,包括:

42、主端基于所述映射关系将第一数据映射为第一高低电平信号,并将第一高低电平信号通过第一链路发送至从端,所述从端基于所述映射关系将接收的第一高低电平信号转换为第一数据;

43、从端基于所述映射关系将第二数据映射为第二高低电平信号,并将第二高低电平信号通过第二链路发送至从端,所述从端基于所述映射关系将接收的第二高低电平信号转换为第二数据。

44、在一个可选的实施方式中,基于所述映射关系将比特级数据转换为高低电平信号的方法,包括:

45、发送端基于数据解析规则解析待发送数据数据帧的比特位数值及排列顺序,依次基于所述映射关系将顺序排列的比特位数值转换为顺序排列的高低电位占比值,所述发送端为主端或从端;

46、发送端将顺序排列的高低电位占比值缓存为任务队列,并在任务队列最前端插入起始标志位对应的第一高低电位占比,得到执行队列;

47、发送端按照所述执行队列中的高低电位占比值依次调节高低电平信号在相应时间周期内的实际高低电位占比,所述高低电位占比为高电位和低单位在单个时间周期内的计数比;

48、接收端利用芯片内部晶振为接收的高低电平信号进行计数,获取高低电平信号每个周期的高低电平计数次数,所述接收到包括主端或从端;

49、接收端依次计算每个周期内的高低电平计数次数比例,得到高低电位占比;

50、接收端基于所述映射关系将依次排列的高低电位占比转换为比特级数据,并基于数据解析规则将所述比特级数据转换为数据帧。

51、在一个可选的实施方式中,利用芯片内部晶振为接收的高低电平信号进行计数的方法包括:

52、每收到依次内部晶振的计数信号,记录一次电位高低状态,得到高低电平计数次数。

53、在一个可选的实施方式中,接收端依次计算每个周期内的高低电平计数次数比例,得到高低电位占比,包括:

54、接收端基于波形约束条件将高低电平信号分割为多个单个周期;

55、依次计算多个单个周期内的高低电平计数次数比例。

56、第三方面,提供一种终端,包括:

57、处理器、存储器,其中,

58、该存储器用于存储计算机程序,

59、该处理器用于从存储器中调用并运行该计算机程序,使得终端执行上述的终端的方法。

60、第四方面,提供了一种计算机存储介质,所述计算机可读存储介质中存储有指令,当其在计算机上运行时,使得计算机执行上述各方面所述的方法。

61、本发明的有益效果在于,本发明提供的忽略时钟误差的数据交互方法、系统、终端及存储介质,通过定义数据与高低电位占比的映射关系,忽略了内部晶振时钟误差对传输数据的影响,因此使用两条信号线可实现数据交互双方的全双工通信,保证数据交互的实时性;总线内无需单独时钟信号,减少了硬件走线的复杂性;无需片外独立晶振,降低了硬件成本。

62、本发明通过设置数据解析规则、波形约束规则降低了数据处理与电平信号转换的复杂度,提升了数据传输效率。

63、本发明提供的数据转换方法,通过将数据分割为数据帧,进一步对数据帧进行分割得到依次排列的比特级数据,然后将这些比特级数据转换为依次排列的高低电位占比值,每个高低电位占比值均对应一个周期,基于预设的信号周期时间,在周期内将实际高低电位占比调整为相应高低电位占比,以队列的方式逐一转换,提升了数据转换的效率和准确度。

64、此外,本发明设计原理可靠,结构简单,具有非常广泛的应用前景。

- 还没有人留言评论。精彩留言会获得点赞!