用于组合优化问题的随机数产生器

本公开涉及概率计算电路领域,具体用于组合优化问题的随机数产生器。

背景技术:

1、组合优化问题是一类在离散状态下求极值点最优化问题,在信息计算、经济管理、工业工程、交通运输、通讯网络等诸多领域有广泛的应用。由于组合优化问题属于多项式复杂程度的非确定性问题,精确算法在问题规模线性扩大时,计算量将指数增长。

2、现有技术中一般使用伪随机数实现对组合优化问题的求解,然而伪随机数由于具有周期性、相干性以及生成的大量数字分布不均匀等缺陷,导致传统数字计算机对组合优化问题的求解精度受到严重影响,使得精准问题求解难以实现。此外,传统计算机产生随机数速度慢,能耗大,且由于冯诺依曼瓶颈,大规模数据在存储器和处理器之间的移动也会消耗大量的时间和能量。

技术实现思路

1、本公开提供了一种用于组合优化问题的随机数产生器,用以解决上述技术问题。

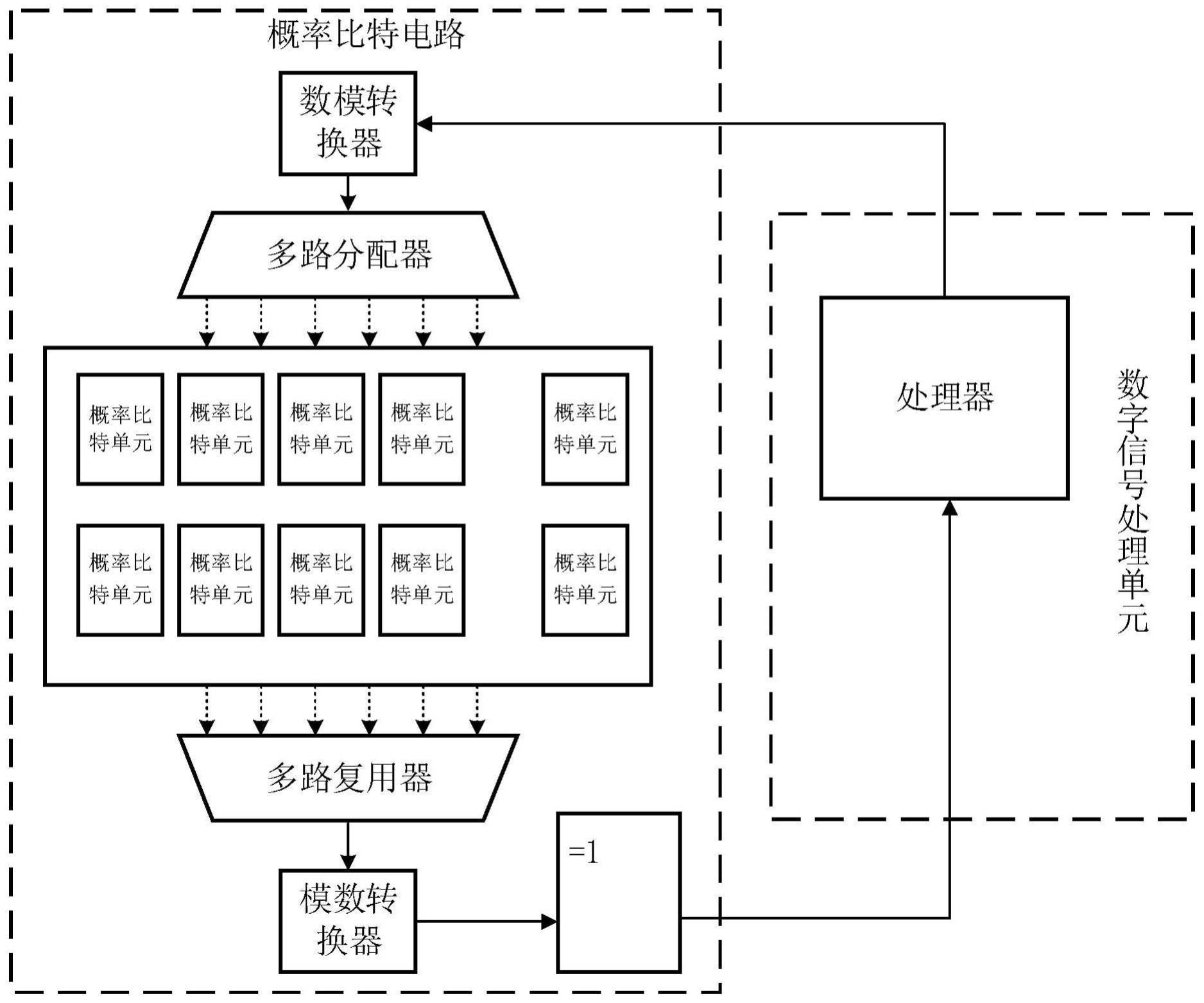

2、本公开的一个方面提供了一种用于组合优化问题的随机数产生器,包括:概率比特电路,用于进行并行概率运算,概率比特电路包括概率比特阵列,用于根据输入信号进行迭代操作;数字信号处理电路,与概率比特电路串联形成回路,用于根据概率比特电路的输出信号确定迭代操作需要的输入信号,以及用于根据输出信号生成对应随机数。

3、根据本公开的实施例,概率运算至少包括概率为0-0.5的概率翻转运算和/或概率为1的概率翻转运算。

4、根据本公开的实施例,概率比特阵列包括:多个概率比特单元,每个概率比特单元均包括第一晶体管、第二晶体管、自旋轨道矩磁隧道结和两态存储器,第一晶体管、第二晶体管、自旋轨道矩磁隧道结和两态存储器之间通过多条电路连线连接;多个概率比特单元的相同信号端之间通过同一电路连线连接。

5、根据本公开的实施例,多条电路连线包括:第一电路连线、第二电路连线、第三电路连线、第四电路连线、第五电路连线、第六电路连线、第七电路连线;第一电路连线,与第一晶体管的栅极连接,用于控制第一晶体管的栅极电压输入;第二电路连线,与第一晶体管的源极连接,用于控制第一晶体管的源极电压输入;第三电路连线,与自旋轨道矩磁隧道结的输出端连接,用于输出列单元信号或作为概率翻转时写入信号的接地端;第四电路连线,与第二晶体管的源极连接,用于控制第二晶体管的源极电压输入;第五电路连线,与第二晶体管的栅极连接,用于控制第二晶体管的栅极电压输入;第六电路连线,与两态存储器的输出连接,用于从两态存储器中读出两态存储器的电压信息;第七电路连线,与两态存储器的浮栅连接,用于控制两态存储器的电阻大小。

6、根据本公开的实施例,自旋轨道矩磁隧道结包括顶电极、钉扎层、氧化层、自由层和重金属层;自由层的磁化状态包括向上状态和向下状态,在重金属层施加电流的情况下产生自旋轨道耦合效应,通过自旋轨道耦合效应转化成的自旋流传导到自由层中,使自由层的磁化方向发生随机翻转;随机翻转的方向由自由层的初始磁化状态和在重金属层施加的电流的大小中的至少之一决定。

7、根据本公开的实施例,在施加给重金属层的电压脉冲的幅值小于阈值的情况下,自由层的状态统计规律同时依赖于电压脉冲前自由层的状态以及电压脉冲的幅值和宽度;

8、根据本公开的实施例,数字信号处理模块包括:门电路,与概率比特电路的输出相连,用于将数字信号进行逻辑异或运算。

9、根据本公开的实施例,概率比特电路包括:模数转换单元,模数转换单元的输入与概率比特阵列的输出连接,模数转换单元的输出与数字信号处理单元连接,用于将概率比特电路的输出转化为数字信号。数模转换单元,数模转换单元的输入与数字信号处理单元的输出连接,数模转换单元的输出与概率比特阵列连接,用于将处理器的数字信号转换为模拟信号,以及用于对概率比特阵列进行读写操作。

10、根据本公开的实施例,模数转换单元包括:多路复用器,与概率比特电路阵列的输出相连,用于读取概率比特电路的多个信号;模数转换器,与多路复用器的输出相连,用于将多路复用器输出的多个信号转换为数字信号。

11、根据本公开的实施例,数模转换单元包括:数模转换器,与处理器的输出相连,用于将处理器获取的翻转概率值转换为模拟信号;多路分配器,与数模转换器和概率比特电路阵列相连,用于将根据数模转换器的模拟信号对概率比特电路进行读写操作。

12、根据本公开的实施例,本公开中的随机数产生器使用了包含自旋轨道矩磁隧道结的概率比特单元,由于自旋轨道矩磁隧道结中的自由层的信息具有非易失性,可以作为信息的存储单元,由此实现存算一体的概率计算,避免了传统计算机产生大规模随机数所造成的存储器和处理器之间数据移动会消耗大量时间和能量的问题。

13、根据本公开的实施例,本公开使用存算一体的概率比特电路实现迭代模拟退火法求解组合优化问题,可以跳出组合优化问题中局部最小值点,且避免了传统随机数产生器利用枚举解决组合优化问题时所需要的产生的随机数序列过于巨大的问题。此外,本公开的技术方案中,概率比特单元使用的是两底端(只用两个晶体管)结构,工业化难度更低。

技术特征:

1.一种用于组合优化问题的随机数产生器,其特征在于,包括:

2.根据权利要求1所述的随机数产生器,其特征在于,所述概率运算至少包括概率为0-0.5的概率翻转运算和/或概率为1的概率翻转运算。

3.根据权利要求1所述的随机数产生器,其特征在于,所述概率比特阵列包括:

4.根据权利要求3所述的随机数产生器,其特征在于,所述多条电路连线包括:第一电路连线、第二电路连线、第三电路连线、第四电路连线、第五电路连线、第六电路连线、第七电路连线;

5.根据权利要求4所述的随机数产生器,其特征在于,所述自旋轨道矩磁隧道结包括顶电极、钉扎层、氧化层、自由层和重金属层;

6.根据权利要求5所述的随机数产生器,其特征在于,在施加给所述重金属层的电压脉冲的幅值小于阈值的情况下,所述自由层的状态统计规律同时依赖于所述电压脉冲前所述自由层的状态以及所述电压脉冲的幅值和宽度。

7.根据权利要求1所述的随机数产生器,其特征在于,所述数字信号处理模块包括:

8.根据权利要求1所述的随机数产生器,其特征在于,所述概率比特电路包括:

9.根据权利要求8所述的随机数产生器,其特征在于,所述模数转换单元包括:

10.根据权利要求8所述的随机数产生器,其特征在于,所述数模转换单元包括:

技术总结

本公开提供了一种用于组合优化问题的随机数产生器,可以应用于概率计算技术领域。该用于组合优化问题的随机数产生器包括:概率比特电路,用于进行并行概率运算,所述概率比特电路包括概率比特阵列,用于根据输入信号进行迭代操作;数字信号处理电路,与所述概率比特电路串联形成回路,用于根据所述概率比特电路的输出信号确定所述迭代操作需要的所述输入信号,以及用于根据所述输出信号生成对应随机数。本公开提供的随机数产生器可以提高随机数产生效率,减少存储器和处理器之间数据移动消耗的大量时间和能量。

技术研发人员:王开友,雷坤,兰修凯

受保护的技术使用者:中国科学院半导体研究所

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!