端口时序约束方法、装置、电子设备及存储介质与流程

本公开涉及芯片设计,尤其涉及一种端口时序约束方法、端口时序约束装置、电子设备及计算机可读存储介质。

背景技术:

1、静态时序分析和收敛作为芯片设计中的重要部分,然而伴随着芯片设计规模的不断提升,芯片中的子模块数量越来越多,使得子模块端口的时序收敛难度加大,进而给后端设计人员带来了前所未有的挑战和困难。在此背景下,前端设计人员提供的约束文件,特别是对于端口的时序约束,变得尤为重要。

2、但是,前端设计人员目前提供的约束文件中,对于端口的时序约束,通常是根据一般的经验值,直接将端口的时序约束值确定为0.6t至0.7t,t为时钟周期。但是这种根据一般经验值确定的端口时序约束值通常会存在约束过严或约束过松的问题,以至于造成时序收敛风险。

技术实现思路

1、本公开的目的是提供一种端口时序约束方法、端口时序约束装置、电子设备及计算机可读存储介质,旨在提高端口时序约束值的准确性,以克服约束过严和约束过松的问题。

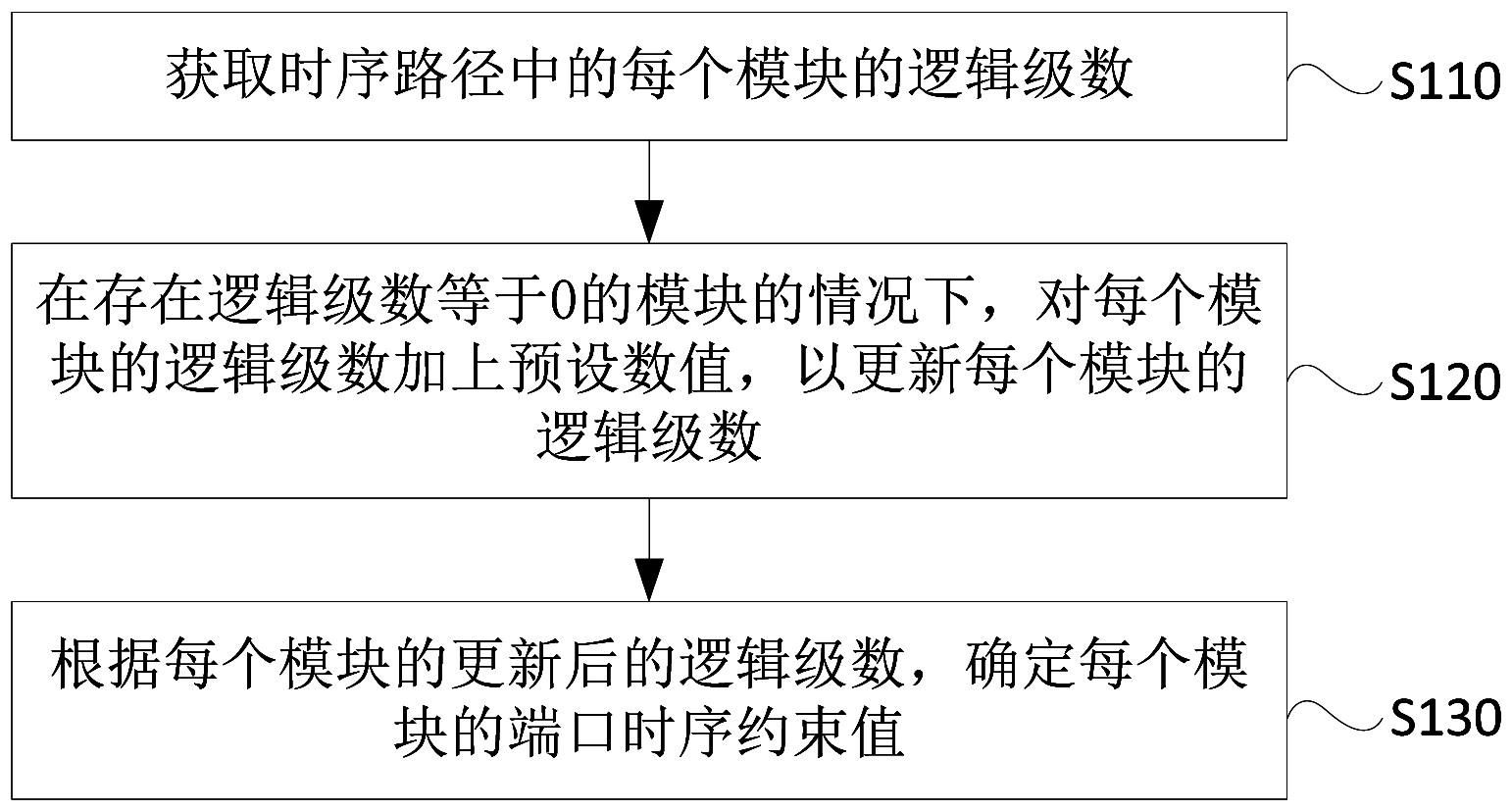

2、根据本公开的一个方面,提供一种端口时序约束方法,该方法包括:

3、获取时序路径中的每个模块的逻辑级数;

4、在存在逻辑级数等于0的模块的情况下,对每个模块的逻辑级数加上预设数值,以更新每个模块的逻辑级数;

5、根据每个模块的更新后的逻辑级数,确定每个模块的端口时序约束值。

6、本公开一种可行的实现方式中,获取时序路径中的每个模块的逻辑级数,包括:

7、针对时序路径中的每个模块,从pt工具中的前端设计文件中获取当前模块对应的逻辑单元名称;

8、根据获取的逻辑单元名称,判断逻辑单元名称对应的逻辑单元是否是功能性的逻辑单元;

9、根据功能性的逻辑单元的数量,确定当前模块的逻辑级数。

10、本公开一种可行的实现方式中,该方法还包括:将前端设计文件输入pt工具,并通过pt工具中的预设函数,从前端设计文件中读取出一个或多个模块分隔标志;

11、针对时序路径中的每个模块,从pt工具中的前端设计文件中获取当前模块对应的逻辑单元名称,包括:

12、对pt工具中的所述前端设计文件进行遍历;

13、在遍历到一个逻辑单元名称时,对当前模块的逻辑单元名称的统计数量加1;

14、在遍历到模块分隔标志时,结束对当前模块的逻辑单元名称的统计,并开始对下一个模块的逻辑单元名称进行统计。

15、本公开一种可行的实现方式中,针对时序路径中的每个模块,从pt工具中的前端设计文件中获取当前模块对应的逻辑单元名称,还包括:

16、在遍历到起始标志时,开始对时序路径的第一个模块的逻辑单元名称进行统计;

17、在遍历到结束标志时,结束逻辑单元名称统计。

18、本公开一种可行的实现方式中,根据每个模块的更新后的逻辑级数,确定每个模块的端口时序约束值,包括:

19、针对时序路径中的每个模块,根据第一逻辑级数总数和第二逻辑级数总数的比值及时钟周期,确定当前模块的端口时序约束值;

20、其中,第一逻辑级数总数是指:时序路径中除当前模块以外的其他模块的更新后的逻辑级数的总和;第二逻辑级数总数是指:时序逻辑中全部模块的更新后的逻辑级数的总和。

21、本公开一种可行的实现方式中,根据第一逻辑级数总数和第二逻辑级数总数的比值及时钟周期,确定当前模块的端口时序约束值,包括:

22、将第一逻辑级数总数和第二逻辑级数总数的比值乘以时钟周期,得到第一约束值分量;

23、将时钟周期乘以预设比例,得到第二约束值分量;

24、将第一约束值分量和第二约束值分量的总和,确定为当前模块的端口时序约束值。

25、本公开一种可行的实现方式中,预设数值为大于等于6且小于等于12的数值。

26、本公开一种可行的实现方式中,每个模块的逻辑级数所加上的预设数值是相同的。

27、本公开一种可行的实现方式中,在存在逻辑级数等于0的模块的情况下,对每个模块的逻辑级数加上预设数值,以更新每个模块的逻辑级数,包括:

28、在存在逻辑级数等于0的模块的情况下,如果逻辑级数不等于0的每个模块的逻辑级数均小于预设阈值,则对每个模块的逻辑级数加上第一预设数值,否则对每个模块的逻辑级数加上第二预设数值;其中,第一预设数值小于第二预设数值。

29、本公开一种可行的实现方式中,该方法还包括:

30、在不存在逻辑级数等于0的模块的情况下,根据每个模块的逻辑级数,确定每个模块的端口时序约束值。

31、本公开一种可行的实现方式中,在不存在逻辑级数等于0的模块的情况下,根据每个模块的逻辑级数,确定每个模块的端口时序约束值,包括:

32、针对时序路径中的每个模块,根据第三逻辑级数总数和第四逻辑级数总数的比值及时钟周期,确定当前模块的端口时序约束值;

33、其中,第三逻辑级数总数是指:时序路径中除当前模块以外的其他模块的逻辑级数的总和;第四逻辑级数总数是指:时序逻辑中全部模块的逻辑级数的总和。

34、本公开一种可行的实现方式中,根据第三逻辑级数总数和第四逻辑级数总数的比值及时钟周期,确定当前模块的端口时序约束值,包括:

35、将第三逻辑级数总数和第四逻辑级数总数的比值乘以时钟周期,得到第三约束值分量;

36、将时钟周期乘以预设比例,得到第四约束值分量;

37、将第三约束值分量和第四约束值分量的总和,确定为当前模块的端口时序约束值。

38、根据本公开的另一方面,还提供一种端口时序约束装置,该装置包括:

39、逻辑级数获取单元,用于获取时序路径中的每个模块的逻辑级数;

40、逻辑级数更新单元,用于在存在逻辑级数等于0的模块的情况下,对每个模块的逻辑级数加上预设数值,以更新每个模块的逻辑级数;

41、约束值确定单元,用于根据每个模块的更新后的逻辑级数,确定每个模块的端口时序约束值。

42、根据本公开的另一方面,还提供一种电子设备,该电子设备包括存储器和处理器;

43、存储器用于存储应用程序;

44、处理器用于运行存储器存储的应用程序,以实现第一方面或第一方面的可行实现方式所述的端口时序约束方法。

45、根据本公开的另一方面,还提供一种计算机可读存储介质,该计算机可读存储介质中存储有应用程序,应用程序被处理器执行时用于实现第一方面或第一方面的可行实现方式所述的端口时序约束方法。

技术特征:

1.一种端口时序约束方法,所述方法包括:

2.根据权利要求1所述的方法,所述获取时序路径中的每个模块的逻辑级数,包括:

3.根据权利要求2所述的方法,所述方法还包括:将所述前端设计文件输入所述pt工具,并通过所述pt工具中的预设函数,从所述前端设计文件中读取出一个或多个模块分隔标志;

4.根据权利要求3所述的方法,所述针对时序路径中的每个模块,从pt工具中的前端设计文件中获取当前模块对应的逻辑单元名称,还包括:

5.根据权利要求1所述的方法,所述根据每个模块的更新后的逻辑级数,确定每个模块的端口时序约束值,包括:

6.根据权利要求5所述的方法,所述根据第一逻辑级数总数和第二逻辑级数总数的比值及时钟周期,确定当前模块的端口时序约束值,包括:

7.根据权利要求1所述的方法,所述预设数值为大于等于6且小于等于12的数值。

8.根据权利要求7所述的方法,每个模块的逻辑级数所加上的预设数值是相同的。

9.根据权利要求1所述的方法,所述在存在逻辑级数等于0的模块的情况下,对每个模块的逻辑级数加上预设数值,以更新每个模块的逻辑级数,包括:

10.根据权利要求1所述的方法,所述方法还包括:

11.根据权利要求10所述的方法,所述在不存在逻辑级数等于0的模块的情况下,根据每个模块的逻辑级数,确定每个模块的端口时序约束值,包括:

12.根据权利要求11所述的方法,所述根据第三逻辑级数总数和第四逻辑级数总数的比值及时钟周期,确定当前模块的端口时序约束值,包括:

13.一种端口时序约束装置,所述装置包括:

14.一种电子设备,所述电子设备包括存储器和处理器;

15.一种计算机可读存储介质,所述计算机可读存储介质中存储有应用程序,所述应用程序被处理器执行时用于实现如权利要求1至12任一项所述的端口时序约束方法。

技术总结

本公开涉及芯片设计技术领域,提供一种端口时序约束方法、装置、电子设备及存储介质。其中,端口时序约束方法包括:获取时序路径中的每个模块的逻辑级数;在存在逻辑级数等于0的模块的情况下,对每个模块的逻辑级数加上预设数值,以更新每个模块的逻辑级数;根据每个模块的更新后的逻辑级数,确定每个模块的端口时序约束值。本公开中,按照上述方式为每个端口确定的端口时序约束值,相较于现有技术中直接根据一般经验值将端口时序约束值确定为0.6T至0.7T,T为时钟周期,本公开确定的端口时序约束值具有更高的准确性,能克服约束过严和约束过松的问题。

技术研发人员:刘战涛

受保护的技术使用者:北京象帝先计算技术有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!