一种均衡训练方法、装置及系统与流程

本技术涉及芯片,尤其涉及一种均衡训练方法、装置及系统。

背景技术:

1、高速串行计算机扩展总线标准(peripheral component interconnect express,pcie)是一种计算机扩展总线标准,pcie总线常用于计算机系统、服务器、存储器、手机等需要高速传输数据的处理器中,来连接外围设备。所述pcie规定,通信系统(例如,主芯片与从芯片之间的链路协商)上电后先进行链路协商,成功协商后,才建立高速链路进行业务数据的收发。其中,从pcie3.0开始,在进行链路协商时,提供了用以补偿因链路损耗引起信号质量问题的均衡训练机制。

2、所述均衡训练机制包括均衡训练阶段一至均衡训练阶段四(phase0~phase3),共4个阶段。当前,均衡训练的每一阶段都规定了固定的均衡超时时间,例如,phase2和phase3阶段规定的均衡超时时间的最大时限通常为32ms。其中,所述通信系统如果在规定的均衡超时时间内均衡训练未完成,便会触发超时,并宣布链路均衡失败。

3、而随着通信速率的飞速提升,在更高速的链路中进行通信传输时,所述通信系统需要更为复杂的均衡电路结构以及数量庞大的均衡参数。也就意味着,该种情况下,在均衡训练阶段中,确定均衡参数需要花费更长的时间,甚至远远超出所述pcie协议目前规定的最大时限32ms的均衡超时时间。因此,在更高速的链路中进行通信传输时,链路协商成功率较低。

4、综上,目前进行均衡训练的方式不够灵活,无法适用更高速的链路协商。

技术实现思路

1、本技术提供一种均衡训练方法,用以更灵活的进行均衡训练,提升高速链路协商的成功率。进一步的,本技术还提供了执行该方法的装置及系统,以及在执行该方法中用到的一种芯片。

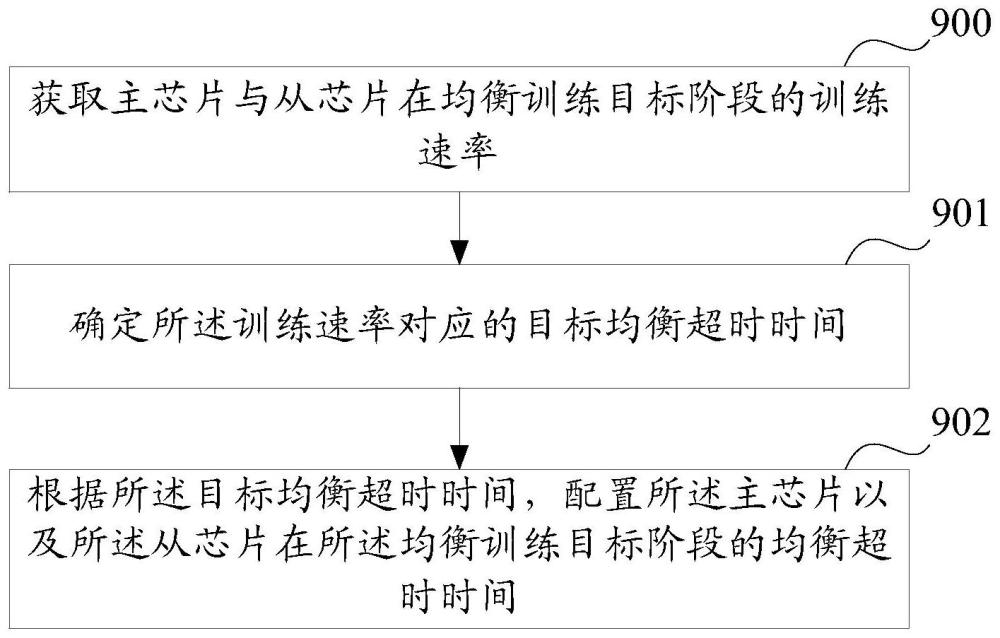

2、第一方面,本技术实施例提供一种均衡训练方法,该方法包括下述步骤:

3、获取主芯片与从芯片在均衡训练的目标阶段的训练速率,所述目标阶段是指第三阶段或第四阶段;确定所述目标阶段的训练速率所在的目标速率阈值区间,根据n+1个速率阈值区间与n+1个均衡超时时间的对应关系,确定所述目标速率阈值区间对应的目标均衡超时时间,并将所述目标均衡超时时间配置为所述目标阶段的均衡超时时间,n个速率阈值是预先确定的,且n是大于或等于0的整数,其中,所述速率阈值区间越大,则对应的所述均衡超时时间越大;则所述主芯片与所述从芯片在所述目标阶段的均衡超时时间内进行所述目标阶段的均衡训练。

4、基于该方案,本发明实施例能够针对每次均衡训练阶段,灵活的配置用于均衡训练的均衡超时时间,从而使配置的均衡超时时间更符合当前用于协商的训练速率。已知的,在均衡的各个阶段,如果芯片的均衡操作不能在均衡超时时间内完成,则该芯片将会退出均衡,进而导致该芯片和对端芯片之间的链路协商失败。而本技术中,均衡训练阶段中配置的均衡超时时间是根据所述均衡训练阶段的训练速率确定的。因此,所述均衡训练阶段配置的均衡超时时间较为充足,能够更好的保证所述均衡训练阶段的操作顺利完成,不会由于时间不充裕而退出。因此,本技术提供的方法能够在一定程度上提升链路协商成功率。

5、需要说明的是,在该芯片为主芯片时,所述对端芯片为从芯片。在该芯片为从芯片时,所述对端芯片为主芯片。

6、可选的,该主芯片和该从芯片之间通过pcie总线或ccix总线连通。可知,本实施例提供的均衡训练方法应用在使用pcie总线或ccix总线的处理器系统内。

7、可选的,在应用pcie总线的处理器系统中,该主芯片为根组件(rc,root complex)或交换芯片,该从芯片是独立于该主芯片的端点设备(endpoint)。应当知道的是,交换芯片在一些情况下可以为主芯片,在另一些情况下可以为从芯片。

8、结合第一方面,在一种可能的实现方式中,在所述目标速率阈值区间为所述n+1个速率阈值区间中速率最小的阈值区间时,所述目标均衡超时时间为前向兼容的均衡超时时间。

9、基于该方案,本发明实施例在确定所述目标阶段的训练速率所在的目标速率阈值区间为最小的阈值区间时,将所述目标均衡超时时间设置为前向兼容的均衡超时时间,无需再根据n+1个速率阈值区间与n+1个均衡超时时间的对应关系查找所述目标阶段的训练速率对应的均衡超时时间时间,更好的节省了系统开销。

10、例如,所述pcie3.0~pcie5.0的前向兼容的均衡超时时间为32ms。

11、结合第一方面,在一种可能的实现方式中,所述n+1个速率阈值区间与所述n+1个均衡超时时间的对应关系预先存储在所述主芯片的寄存器内或所述从芯片的寄存器内。

12、基于该方案,将所述n+1个速率阈值区间与所述n+1个均衡超时时间的对应关系预先存储到所述主芯片的寄存器内,或者所述从芯片的寄存器内,从而在用到所述n+1个速率阈值区间与所述n+1个均衡超时时间的对应关系时,可以直接到对应芯片的寄存器中读取,节约时间。

13、结合第一方面,在一种可能的实现方式中,所述获取主芯片与从芯片在均衡训练的目标阶段的训练速率之前,确定不采用快速均衡训练模式;所述快速均衡训练模式是指根据上一轮均衡训练目标阶段的发送参数和接收参数,分别配置所述主芯片和所述从芯片在本轮均衡训练目标阶段的初始参数的模式。

14、基于该方案,本发明实施例中还提供了一种快速均衡训练模式,即如果在进行本轮均衡训练目标阶段之前,选择了快速均衡训练模式,则将前一轮均衡训练阶段的发送参数和接收参数分别配置为所述主芯片和所述从芯片在本轮均衡训练目标节点的初始参数。丰富了进行均衡训练的方法,同时,因采用快速均衡训练模式,能够有效降低获取均衡参数的复杂度以及有效缩短获取均衡参数的时间,从而,更好的保证所述均衡训练阶段的操作顺利完成,不会由于时间不充裕而退出,一定程度上提升链路协商成功率。

15、结合第一方面,在一种可能的实现方式中,在完成本轮均衡训练目标阶段的均衡训练后,将所述主芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述主芯片的寄存器内,并将所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述从芯片的寄存器内;

16、或者,将所述主芯片以及所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述主芯片的寄存器内;或者,将所述主芯片以及所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述从芯片的寄存器内。

17、基于该方案,在完成本轮均衡训练目标阶段的均衡训练后,存储所述主芯片在所述本轮均衡训练目标阶段的均衡参数,以及存储所述从芯片在所述本轮均衡训练目标阶段的均衡参数。从而在进行下一轮均衡训练目标阶段时,可以直接获取主芯片与从芯片事先存储的发送参数和接收参数,用于确定初始参数,节约时间。

18、结合第一方面,在一种可能的实现方式中,所述确定不采用快速均衡训练模式之前,获取所述主芯片与所述从芯片用于进行所述均衡训练目标阶段的协商序列;根据所述协商序列指定的比特位值与均衡训练模式的对应关系,确定所述协商序列中指定的比特位值对应非快速均衡训练模式。

19、基于该方案,本发明实施例提供了一种如何确定是否采用均衡训练模式的方法,即根据用于进行所述均衡训练目标阶段的协商序列中指定比特位值来确定,丰富了均衡训练方式。

20、第二方面,本技术实施例还提供一种均衡训练方法,该方法包括下述步骤:

21、判断是否采用快速均衡模式,在确定采用快速均衡模式时,获取主芯片与从芯片在前一轮均衡训练目标阶段的发送参数和接收参数,并将所述发送参数和所述接收参数分别配置为所述主芯片和所述从芯片在本轮均衡训练目标阶段的初始参数,均衡训练目标阶段是指均衡训练的第三阶段或第四阶段,获取均衡训练目标阶段前向兼容的均衡超时时间,并将所述前向兼容的均衡超时时间配置为本轮均衡训练目标阶段的均衡超时时间;在所述本轮均衡训练目标阶段的均衡超时时间内,利用所述主芯片和所述从芯片在所述本轮均衡训练目标阶段的初始参数进行均衡训练。

22、基于该方案,本发明实施例在进行本次均衡训练目标阶段中,获取主芯片与从芯片在前一轮均衡训练目标阶段的发送参数和接收参数,并将所述发送参数和所述接收参数分别配置为所述主芯片和所述从芯片在本轮均衡训练目标阶段的初始参数。丰富了进行均衡训练的方法,有助于更快获取本次均衡训练阶段的均衡参数,适用性更强,效率更高。同时,因采用快速均衡训练模式,能够有效降低获取均衡参数的复杂度以及有效缩短获取均衡参数的时间,从而,更好的保证所述均衡训练阶段的操作顺利完成,不会由于时间不充裕而退出,一定程度上提升链路协商成功率。

23、需要说明的是,在该芯片为主芯片时,所述对端芯片为从芯片。在该芯片为从芯片时,所述对端芯片为主芯片。

24、可选的,该主芯片和该从芯片之间通过pcie总线或ccix总线连通。可知,本实施例提供的均衡训练方法应用在使用pcie总线或ccix总线的处理器系统内。

25、可选的,在应用pcie总线的处理器系统中,该主芯片为根组件(rc,root complex)或交换芯片,该从芯片是独立于该主芯片的端点设备(endpoint)。应当知道的是,交换芯片在一些情况下可以为主芯片,在另一些情况下可以为从芯片。

26、结合第二方面,在一种可能的实现方式中,所述快速均衡训练模式是指根据上一轮均衡训练目标阶段的发送参数和接收参数,分别配置所述主芯片和所述从芯片在本轮均衡训练目标阶段的初始参数的模式。基于该方案,本发明实施例中还提供了一种快速均衡训练模式,即在确认采用快速均衡训练模式后,根据上一轮均衡训练目标阶段的发送参数和接收参数,分别配置所述主芯片和所述从芯片在本轮均衡训练目标阶段的初始参数。丰富了进行均衡训练的方法,有助于更快获取本次均衡训练阶段的均衡参数。

27、结合第二方面,在一种可能的实现方式中,在完成本轮均衡训练目标阶段的均衡训练后,将所述主芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述主芯片的寄存器内,并将所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述从芯片的寄存器内;

28、或者,将所述主芯片以及所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述主芯片的寄存器内;或者,将所述主芯片以及所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述从芯片的寄存器内。

29、基于该方案,在完成本轮均衡训练目标阶段的均衡训练后,存储所述主芯片在所述本轮均衡训练目标阶段的均衡参数,以及存储所述从芯片在所述本轮均衡训练目标阶段的均衡参数。从而在进行下一轮均衡训练目标阶段时,可以直接获取主芯片与从芯片事先存储的发送参数和接收参数,用于确定初始参数,节约时间。

30、结合第二方面,在一种可能的实现方式中,所述确定采用快速均衡训练模式之前,获取所述主芯片与所述从芯片用于进行所述均衡训练目标阶段的协商序列;根据所述协商序列指定的比特位值与均衡训练模式的对应关系,确定所述协商序列中指定的比特位值对应非快速均衡训练模式。

31、基于该方案,本发明实施例提供了一种如何确定是否采用均衡训练模式的方法,即根据用于进行所述均衡训练目标阶段的协商序列中指定比特位值来确定,丰富了均衡训练方式。

32、第三方面,本技术提供一种均衡训练装置,该装置用于执行前述第一方面或第一方面任一实现方式所述的方法。该装置包括收发器和管理器。

33、收发器用于获取主芯片与从芯片在均衡训练的目标阶段的训练速率,所述目标阶段是指第三阶段或第四阶段。对应的,管理器用于确定所述目标阶段的训练速率所在的目标速率阈值区间,根据n+1个速率阈值区间与n+1个均衡超时时间的对应关系,确定所述目标速率阈值区间对应的目标均衡超时时间,并将所述目标均衡超时时间配置为所述目标阶段的均衡超时时间,n个速率阈值是预先确定的,且n是大于或等于0的整数,其中,所述速率阈值区间越大,则对应的所述均衡超时时间越大;则所述主芯片与所述从芯片在所述目标阶段的均衡超时时间内进行所述目标阶段的均衡训练。

34、采用本实施例提供的装置,能够实现第一方面或第一方面任一种可能的实现方式所述的均衡训练方法。可知,采用本实施例提供的装置,能够使得该主芯片在均衡的第三阶段的均衡超时时间是充足的,相应的,该主芯片在该第三阶段的均衡操作不会因为时间不够而退出;以及,使得该从芯片在均衡的第四阶段的均衡超时时间也是充足的,相应的,该从芯片在该第四阶段的均衡操作也不会因为时间不够而退出。因此,采用本实施例提供的装置,能够在一定程度上降低因为均衡超时时间不够而导致芯片退出均衡操作,有效提升链路协商成功率。

35、结合第三方面,在一种可能的实现方式下,在所述目标速率阈值区间为所述n+1个速率阈值区间中速率最小的阈值区间时,所述目标均衡超时时间为前向兼容的均衡超时时间。

36、该方案的有益效果可以参见第一方面的相关实现方式对应的有益效果,此处不再赘述。

37、如前文所述,所述pcie3.0~pcie5.0的前向兼容的均衡超时时间为32ms。

38、结合第三方面,在一种可能的实现方式下,所述n+1个速率阈值区间与所述n+1个均衡超时时间的对应关系预先存储在所述主芯片的寄存器内或所述从芯片的寄存器内。

39、结合第三方面,在一种可能的实现方式下,所述获取主芯片与从芯片在均衡训练的目标阶段的训练速率之前,所述管理器还用于确定不采用快速均衡训练模式;所述快速均衡训练模式是指根据上一轮均衡训练目标阶段的发送参数和接收参数,分别配置所述主芯片和所述从芯片在本轮均衡训练目标阶段的初始参数的模式。

40、该方案的有益效果可以参见第一方面的相关实现方式对应的有益效果,此处不再赘述。

41、结合第三方面,在一种可能的实现方式下,在完成本轮均衡训练目标阶段的均衡训练后,所述管理器还用于将所述主芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述主芯片的寄存器内,并将所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述从芯片的寄存器内;或者,将所述主芯片以及所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述主芯片的寄存器内;或者,将所述主芯片以及所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述从芯片的寄存器内。

42、结合第三方面,在一种可能的实现方式下,所述收发器还用于获取所述主芯片与所述从芯片用于进行所述均衡训练目标阶段的协商序列;根据所述协商序列指定的比特位值与均衡训练模式的对应关系,确定所述协商序列中指定的比特位值对应非快速均衡训练模式。

43、该方案的有益效果可以参见第一方面的相关实现方式对应的有益效果,此处不再赘述。

44、第四方面,本技术提供一种均衡训练装置,该装置用于执行前述第二方面或第二方面任一实现方式所述的方法。该装置包括收发器和管理器。

45、管理器,用于判断是否采用快速均衡模式;

46、收发器,用于在确定采用快速均衡模式时,获取主芯片与从芯片在前一轮均衡训练目标阶段的发送参数和接收参数;

47、管理器还用于将所述发送参数和所述接收参数分别配置为所述主芯片和所述从芯片在本轮均衡训练目标阶段的初始参数,均衡训练目标阶段是指均衡训练的第三阶段或第四阶段;

48、收发器还用于获取均衡训练目标阶段前向兼容的均衡超时时间;

49、管理器还用于将所述前向兼容的均衡超时时间配置为本轮均衡训练目标阶段的均衡超时时间;

50、以及,所述管理器还用于在所述本轮均衡训练目标阶段的均衡超时时间内,利用所述主芯片和所述从芯片在所述本轮均衡训练目标阶段的初始参数进行均衡训练。

51、采用本实施例提供的装置,能够实现第二方面或第二方面任一种可能的实现方式所述的均衡训练方法。可知,采用本实施例提供的装置,能够更快的为所述主芯片和所述从芯片配置本轮均衡训练目标阶段的初始参数,丰富了进行均衡训练的方法,有助于更快获取本次均衡训练阶段的均衡参数,适用性更强,效率更高。此外,有效降低了在进行均衡训练目标阶段过程中因时间不够而退出的概率,提升链路协商成功率。

52、结合第四方面,在一种可能的实现方式下,在完成本轮均衡训练目标阶段的均衡训练后,所述管理器还用于将所述主芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述主芯片的寄存器内,并将所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述从芯片的寄存器内;或者,将所述主芯片以及所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述主芯片的寄存器内;或者,将所述主芯片以及所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述从芯片的寄存器内。

53、该方案的有益效果可以参见第二方面的相关实现方式对应的有益效果,此处不再赘述。

54、结合第四方面,在一种可能的实现方式下,确定采用快速均衡训练模式之前,所述收发器还用于获取所述主芯片与所述从芯片用于进行所述均衡训练目标阶段的协商序列;所述管理器还用于根据所述协商序列指定的比特位值与均衡训练模式的对应关系,确定所述协商序列中指定的比特位值对应非快速均衡训练模式。

55、该方案的有益效果可以参见第二方面的相关实现方式对应的有益效果,此处不再赘述。

56、第五方面,本技术提供另一种均衡训练装置,该装置也用于执行前述第一方面或第一方面任一实现方式所述的均衡训练方法。该装置包括获取单元、确定单元和配置单元。

57、所述获取单元,用于获取主芯片与从芯片在均衡训练的目标阶段的训练速率,所述目标阶段是指第三阶段或第四阶段;

58、所述确定单元,用于确定所述目标阶段的训练速率所在的目标速率阈值区间,根据n+1个速率阈值区间与n+1个均衡超时时间的对应关系,确定所述目标速率阈值区间对应的目标均衡超时时间;

59、所述配置单元,用于将所述目标均衡超时时间配置为所述目标阶段的均衡超时时间;

60、其中,n个速率阈值是预先确定的,且n是大于或等于0的整数,所述速率阈值区间越大,则对应的所述均衡超时时间越大;

61、则所述主芯片与所述从芯片在所述目标阶段的均衡超时时间内进行所述目标阶段的均衡训练。

62、本实施例提供的装置用于执行第一方面或第一方面任一种可能的实现方式所述的方法。采用本实施例提供的装置,能够使得该主芯片在均衡的第三阶段的均衡超时时间是充足的,相应的,该主芯片在该第三阶段的均衡操作不会因为时间不够而退出;以及,使得该从芯片在均衡的第四阶段的均衡超时时间也是充足的,相应的,该从芯片在该第四阶段的均衡操作也不会因为时间不够而退出。因此,采用本实施例提供的装置,能够在一定程度上降低因为均衡超时时间不够而导致芯片退出均衡操作,有效提升链路协商成功率。

63、结合第五方面,在一种可能的实现方式下,所述确定单元具体用于在所述目标速率阈值区间为所述n+1个速率阈值区间中速率最小的阈值区间时,所述目标均衡超时时间为前向兼容的均衡超时时间。

64、结合第五方面,在一种可能的实现方式下,所述n+1个速率阈值区间与所述n+1个均衡超时时间的对应关系预先存储在所述主芯片的寄存器内或所述从芯片的寄存器内。

65、结合第五方面,在一种可能的实现方式下,所述获取主芯片与从芯片在均衡训练的目标阶段的训练速率之前,所述确定单元还用于确定不采用快速均衡训练模式;所述快速均衡训练模式是指根据上一轮均衡训练目标阶段的发送参数和接收参数,分别配置所述主芯片和所述从芯片在本轮均衡训练目标阶段的初始参数的模式。

66、结合第五方面,在一种可能的实现方式下,所述获取单元还用于在完成本轮均衡训练目标阶段的均衡训练后,将所述主芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述主芯片的寄存器内,并将所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述从芯片的寄存器内;或者,将所述主芯片以及所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述主芯片的寄存器内;或者,将所述主芯片以及所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述从芯片的寄存器内。

67、结合第五方面,在一种可能的实现方式下,所述获取单元还用于获取所述主芯片与所述从芯片用于进行所述均衡训练目标阶段的协商序列;所述确定单元还用于根据所述协商序列指定的比特位值与均衡训练模式的对应关系,确定所述协商序列中指定的比特位值对应非快速均衡训练模式。

68、第六方面,本技术提供另一种均衡训练装置,该装置也用于执行前述第二方面或第二方面任一实现方式所述的均衡训练方法。该装置包括获取单元、确定单元和配置单元。

69、所述确定单元,用于判断是否采用快速均衡模式;

70、所述获取单元,用于在确定采用快速均衡模式时,获取主芯片与从芯片在前一轮均衡训练目标阶段的发送参数和接收参数;

71、所述配置单元,用于将所述发送参数和所述接收参数分别配置为所述主芯片和所述从芯片在本轮均衡训练目标阶段的初始参数,均衡训练目标阶段是指均衡训练的第三阶段或第四阶段;

72、所述获取单元还用于获取均衡训练目标阶段前向兼容的均衡超时时间;

73、所述配置单元还用于将所述前向兼容的均衡超时时间配置为本轮均衡训练目标阶段的均衡超时时间;则在所述本轮均衡训练目标阶段的均衡超时时间内,利用所述主芯片和所述从芯片在所述本轮均衡训练目标阶段的初始参数进行均衡训练。

74、本实施例提供的装置用于执行第二方面或第二方面任一种可能的实现方式所述的方法。采用本实施例提供的装置,能够更快的为所述主芯片和所述从芯片配置本轮均衡训练目标阶段的初始参数,丰富了进行均衡训练的方法,有助于更快获取本次均衡训练阶段的均衡参数,适用性更强,效率更高。此外,有效降低了在进行均衡训练目标阶段过程中因时间不够而退出的概率,提升链路协商成功率。

75、结合第六方面,在一种可能的实现方式下,所述获取单元还用于在完成本轮均衡训练目标阶段的均衡训练后,将所述主芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述主芯片的寄存器内,并将所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述从芯片的寄存器内;或者,将所述主芯片以及所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述主芯片的寄存器内;或者,将所述主芯片以及所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述从芯片的寄存器内。

76、结合第六方面,在一种可能的实现方式下,确定采用快速均衡训练模式之前,所述获取单元还用于获取所述主芯片与所述从芯片用于进行所述均衡训练目标阶段的协商序列;所述确定单元还用于根据所述协商序列指定的比特位值与均衡训练模式的对应关系,确定所述协商序列中指定的比特位值对应非快速均衡训练模式。

77、第七方面,本技术提供了再一种均衡训练装置,该装置也用于执行前述第一方面或第一方面任一实现方式所述的均衡训练方法。该装置包括中央处理器(cpu,centralprocessor unit)和存储器,cpu用于执行存储在存储器内的代码以本实施例所述的装置的功能。

78、存储器用于存储n+1个速率阈值区间与n+1个均衡超时时间的对应关系。对应的,cpu用于获取主芯片与从芯片在均衡训练的目标阶段的训练速率,所述目标阶段是指第三阶段或第四阶段。

79、cpu还用于确定所述目标阶段的训练速率所在的目标速率阈值区间,根据n+1个速率阈值区间与n+1个均衡超时时间的对应关系,确定所述目标速率阈值区间对应的目标均衡超时时间,并将所述目标均衡超时时间配置为所述目标阶段的均衡超时时间,n个速率阈值是预先确定的,且n是大于或等于0的整数,其中,所述速率阈值区间越大,则对应的所述均衡超时时间越大;则所述主芯片与所述从芯片在所述目标阶段的均衡超时时间内进行所述目标阶段的均衡训练。

80、与前述各个实现方式所述的装置类似,采用本实施例所述的装置,能够在一定程度上降低由于均衡超时时间不够而导致系统退出均衡操作,进而导致链路协商失败的风险。

81、第八方面,本技术提供了再一种均衡训练装置,该装置也用于执行前述第二方面或第二方面任一实现方式所述的均衡训练方法。该装置包括中央处理器(cpu,centralprocessor unit)和存储器,cpu用于执行存储在存储器内的代码以本实施例所述的装置的功能。

82、存储器用于存储前一轮均衡训练目标阶段的均衡参数。对应的,cpu用于判断是否采用快速均衡模式,在确定采用快速均衡模式时,获取主芯片与从芯片在前一轮均衡训练目标阶段的发送参数和接收参数,并将所述发送参数和所述接收参数分别配置为所述主芯片和所述从芯片在本轮均衡训练目标阶段的初始参数,均衡训练目标阶段是指均衡训练的第三阶段或第四阶段。

83、cpu还用于获取均衡训练目标阶段前向兼容的均衡超时时间,并将所述前向兼容的均衡超时时间配置为本轮均衡训练目标阶段的均衡超时时间;在所述本轮均衡训练目标阶段的均衡超时时间内,利用所述主芯片和所述从芯片在所述本轮均衡训练目标阶段的初始参数进行均衡训练。

84、与前述各个实现方式所述的装置类似,采用本实施例所述的装置,能够在一定程度上降低由于均衡超时时间不够而导致系统退出均衡操作,进而导致链路协商失败的风险。

85、第九方面,本技术提供了一种芯片,该芯片可以为前述第一方面或其任一种实现方式、或第三方面或其任一种实现方式、或第五方面或其任一种实现方式提及的主芯片或从芯片。该芯片包括寄存器、收发器和管理器。

86、寄存器,用于存储n+1个速率阈值区间与n+1个均衡超时时间的对应关系;

87、收发器,用于获取主芯片与从芯片在均衡训练的目标阶段的训练速率,所述目标阶段是指第三阶段或第四阶段;

88、管理器,用于确定所述目标阶段的训练速率所在的目标速率阈值区间,根据n+1个速率阈值区间与n+1个均衡超时时间的对应关系,确定所述目标速率阈值区间对应的目标均衡超时时间,并将所述目标均衡超时时间配置为所述目标阶段的均衡超时时间,n个速率阈值是预先确定的,且n是大于或等于0的整数,其中,所述速率阈值区间越大,则对应的所述均衡超时时间越大;

89、则所述主芯片与所述从芯片在所述目标阶段的均衡超时时间内进行所述目标阶段的均衡训练。

90、应用本实施例所述的芯片,能够实现第一方面或第一方面的任一种可能的实现方式所述的方法,进而实现降低因均衡超时时间不够而导致系统退出均衡操作,进而导致链路协商失败的风险。

91、结合第九方面,在第一种可能的实现方式下,所述寄存器还用于存储前向兼容的均衡超时时间。

92、结合第九方面,在第一种可能的实现方式下,所述寄存器还用于存储本轮均衡训练目标阶段的均衡参数。

93、进一步的,本技术实施例中,所述芯片具有打开和关闭部分均衡电路,在需要快速均衡过程的情况下关闭部分均衡电路的功能,比如关闭dfe或者部分ctle,实现缩短均衡时间。其中,本技术实施例所述芯片自带管理软件,或者是符合标准的状态机。

94、第十方面,本技术提供了一种芯片,该芯片可以为前述第二方面或其任一种实现方式、或第四方面或其任一种实现方式、或第六方面或其任一种实现方式提及的主芯片或从芯片。该芯片包括寄存器、收发器和管理器。

95、寄存器,用于存储所述芯片本轮均衡训练目标阶段的均衡参数;

96、管理器,用于判断是否采用快速均衡模式;

97、收发器,用于在确定采用快速均衡模式时,获取主芯片与从芯片在前一轮均衡训练目标阶段的发送参数和接收参数;

98、管理器还用于将所述发送参数和所述接收参数分别配置为所述主芯片和所述从芯片在本轮均衡训练目标阶段的初始参数,均衡训练目标阶段是指均衡训练的第三阶段或第四阶段;

99、收发器还用于获取均衡训练目标阶段前向兼容的均衡超时时间;

100、管理器还用于将所述前向兼容的均衡超时时间配置为本轮均衡训练目标阶段的均衡超时时间;以及在所述本轮均衡训练目标阶段的均衡超时时间内,利用所述主芯片和所述从芯片在所述本轮均衡训练目标阶段的初始参数进行均衡训练。

101、应用本实施例所述的芯片,能够实现第二方面或第二方面的任一种可能的实现方式所述的方法,进而实现降低因均衡超时时间不够而导致系统退出均衡操作,进而导致链路协商失败的风险。

102、结合第十方面,在第一种可能的实现方式下,所述寄存器还用于存储本轮均衡训练目标阶段的均衡参数。

103、结合第十方面,在第一种可能的实现方式下,所述寄存器还用于存储n+1个速率阈值区间与n+1个均衡超时时间的对应关系。

104、进一步的,本技术实施例中,所述芯片具有打开和关闭部分均衡电路,在需要快速均衡过程的情况下关闭部分均衡电路的功能,比如关闭dfe或者部分ctle,实现缩短均衡时间。其中,本技术实施例所述芯片自带管理软件,或者是符合标准的状态机。

105、第十一方面,本技术还提供一种通信系统,该通信系统包括系统软件、主芯片和从芯片。所述主芯片和所述从芯片之间通过总线或ccix总线连通。

106、所述系统软件用于获取主芯片与从芯片在均衡训练的目标阶段的训练速率,所述目标阶段是指第三阶段或第四阶段;确定所述目标阶段的训练速率所在的目标速率阈值区间,根据n+1个速率阈值区间与n+1个均衡超时时间的对应关系,确定所述目标速率阈值区间对应的目标均衡超时时间,并将所述目标均衡超时时间配置为所述目标阶段的均衡超时时间,n个速率阈值是预先确定的,且n是大于或等于0的整数,其中,所述速率阈值区间越大,则对应的所述均衡超时时间越大;则所述主芯片与所述从芯片在所述目标阶段的均衡超时时间内进行所述目标阶段的均衡训练。

107、采用本实施例提供的装置,能够实现第一方面或第一方面任一种可能的实现方式所述的均衡训练方法。可知,采用本实施例提供的装置,能够使得该主芯片在均衡的第三阶段的均衡超时时间是充足的,相应的,该主芯片在该第三阶段的均衡操作不会因为时间不够而退出;以及,使得该从芯片在均衡的第四阶段的均衡超时时间也是充足的,相应的,该从芯片在该第四阶段的均衡操作也不会因为时间不够而退出。因此,采用本实施例提供的装置,能够在一定程度上降低因为均衡超时时间不够而导致芯片退出均衡操作,有效提升链路协商成功率。

108、结合第十一方面,在一种可能的实现方式下,所述系统软件还用于在所述目标速率阈值区间为所述n+1个速率阈值区间中速率最小的阈值区间时,所述目标均衡超时时间为前向兼容的均衡超时时间。

109、结合第十一方面,在一种可能的实现方式下,所述n+1个速率阈值区间与所述n+1个均衡超时时间的对应关系预先存储在所述主芯片的寄存器内或所述从芯片的寄存器内。

110、结合第十一方面,在一种可能的实现方式下,所述获取主芯片与从芯片在均衡训练的目标阶段的训练速率之前,所述系统软件还用于确定不采用快速均衡训练模式;所述快速均衡训练模式是指根据上一轮均衡训练目标阶段的发送参数和接收参数,分别配置所述主芯片和所述从芯片在本轮均衡训练目标阶段的初始参数的模式。

111、结合第十一方面,在一种可能的实现方式下,在完成本轮均衡训练目标阶段的均衡训练后,所述系统软件还用于将所述主芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述主芯片的寄存器内,并将所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述从芯片的寄存器内;或者,将所述主芯片以及所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述主芯片的寄存器内;或者,将所述主芯片以及所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述从芯片的寄存器内。

112、结合第十一方面,在一种可能的实现方式下,所述系统软件还用于获取所述主芯片与所述从芯片用于进行所述均衡训练目标阶段的协商序列;根据所述协商序列指定的比特位值与均衡训练模式的对应关系,确定所述协商序列中指定的比特位值对应非快速均衡训练模式。

113、需要说明的是,第十一方面或其各个可能实现方式的有益效果可以参见前述各个关联实施例的有益效果,由于高度类似,因此不再赘述。

114、第十二方面,本技术还提供一种通信系统,该通信系统包括系统软件、主芯片和从芯片。所述主芯片和所述从芯片之间通过总线或ccix总线连通。

115、所述系统软件用于判断是否采用快速均衡模式,在确定采用快速均衡模式时,获取主芯片与从芯片在前一轮均衡训练目标阶段的发送参数和接收参数,并将所述发送参数和所述接收参数分别配置为所述主芯片和所述从芯片在本轮均衡训练目标阶段的初始参数,均衡训练目标阶段是指均衡训练的第三阶段或第四阶段,获取均衡训练目标阶段前向兼容的均衡超时时间,并将所述前向兼容的均衡超时时间配置为本轮均衡训练目标阶段的均衡超时时间;在所述本轮均衡训练目标阶段的均衡超时时间内,利用所述主芯片和所述从芯片在所述本轮均衡训练目标阶段的初始参数进行均衡训练。

116、采用本实施例提供的装置,能够实现第二方面或第二方面任一种可能的实现方式所述的均衡训练方法。可知,采用本实施例提供的装置,能够更快的为所述主芯片和所述从芯片配置本轮均衡训练目标阶段的初始参数,丰富了进行均衡训练的方法,有助于更快获取本次均衡训练阶段的均衡参数,适用性更强,效率更高。此外,有效降低了在进行均衡训练目标阶段过程中因时间不够而退出的概率,提升链路协商成功率。

117、结合第十二方面,在一种可能的实现方式下,在完成本轮均衡训练目标阶段的均衡训练后,所述系统软件还用于将所述主芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述主芯片的寄存器内,并将所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述从芯片的寄存器内;或者,将所述主芯片以及所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述主芯片的寄存器内;或者,将所述主芯片以及所述从芯片在所述本轮均衡训练目标阶段的均衡参数存储在所述从芯片的寄存器内。

118、结合第十二方面,在一种可能的实现方式下,确定采用快速均衡训练模式之前,所述系统软件还用于获取所述主芯片与所述从芯片用于进行所述均衡训练目标阶段的协商序列;以及根据所述协商序列指定的比特位值与均衡训练模式的对应关系,确定所述协商序列中指定的比特位值对应非快速均衡训练模式。

119、需要说明的是,第十二方面或其各个可能实现方式的有益效果可以参见前述各个关联实施例的有益效果,由于高度类似,因此不再赘述。

120、第十三方面,本技术实施例提供了一种计算机程序产品,计算机程序产品包括:计算机程序代码,当计算机程序代码被均衡训练装置的单元模块或收发器、管理器运行时,使得该装置执行上述第一方面或第二方面中的任意一面;或第一方面至第二方面中的任意可能的实现方式中的任一方法。

121、第十四方面,本技术实施例提供了一种计算机可读存储介质,计算机可读存储介质存储有程序,程序使得均衡超时时间训练装置(例如,主芯片;再例如,从芯片)执行上述第一方面或第二方面中的任意一面;或第一方面至第二方面中的任意可能的实现方式中的任一方法。

- 还没有人留言评论。精彩留言会获得点赞!