基于ONFIPHY接口规范的内存访问方法和装置与流程

本技术涉及存储器,尤其涉及一种基于onfi phy接口规范的内存访问方法和装置。

背景技术:

1、nand flash存储器由于容量大、改写速度快等优点在业界得到了广泛应用,onfi(open nand flash interface,开放式nand快闪存储器接口)规范也成为当前主流的nandflash接口标准。

2、在现有电子系统的设计过程中,通常会将onfi内存接口分成内存控制逻辑(onficontroller)和物理层接口(onfi phy)两个部分。但由于onfi controller和onfi phy两部分的设计者往往并不相同,因此为了能够实现两者之间的互联以进行内存访问,每次均需要针对性设计对应的硬件电路和内存访问方法,不但降低了芯片的研发效率,提高了设计成本,也导致内存访问的效率大大降低。

技术实现思路

1、本技术提供一种基于onfi phy接口规范的内存访问方法和装置,以用于解决现有技术中芯片研发效率低、设计成本高及内存访问效率低的问题。

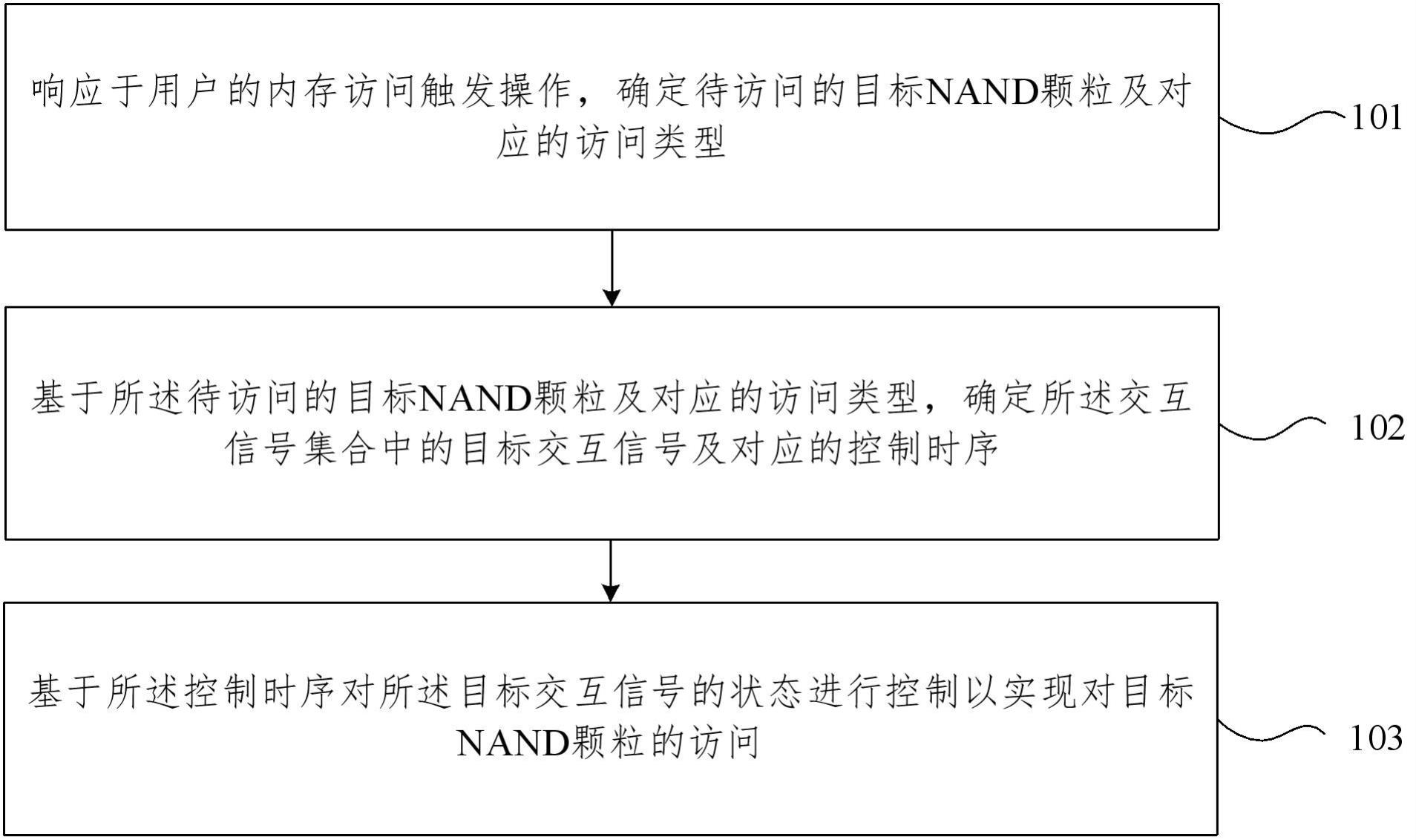

2、本技术提供一种基于onfi phy接口规范的内存访问方法,所述onfi phy接口规范定义了内存控制器与物理层之间的通用接口及对应的交互信号集合,所述方法包括:

3、响应于用户的内存访问触发操作,确定待访问的目标nand颗粒及对应的访问类型;

4、基于所述待访问的目标nand颗粒及对应的访问类型,确定所述交互信号集合中的目标交互信号及对应的控制时序;

5、基于所述控制时序对所述目标交互信号的状态进行控制以实现对目标nand颗粒的访问。

6、根据本技术提供的一种基于onfi phy接口规范的内存访问方法,所述交互信号集合中包括命令和地址信号子集、数据总线信号子集和自定义信号子集;

7、所述命令和地址信号子集中的交互信号用于对接nand颗粒的芯片使能接口、读使能接口、地址锁存使能接口、命令锁存使能接口、写使能接口、写保护接口和状态接口;

8、所述数据总线信号子集中的交互信号用于对接nand颗粒的数据接口;

9、所述自定义信号子集中的交互信号用于物理层的内部控制及与内存控制器的非内存访问目的的交互。

10、根据本技术提供的一种基于onfi phy接口规范的内存访问方法,所述命令和地址信号子集中的交互信号包括:

11、片选控制信号onfi_ce_n,用于关联nand颗粒的芯片使能接口;

12、读使能控制信号onfi_re_p0、onfi_re_p1、onfi_re_toggle_p0和onfi_re_toggle_p1,用于关联nand颗粒的读使能接口;

13、地址锁存控制信号onfi_ale_p0和onfi_ale_p1,用于关联nand颗粒的地址锁存使能接口;

14、命令锁存控制信号onfi_cle_p0和onfi_cle_p1,用于关联nand颗粒的命令锁存使能接口;

15、写使能控制信号onfi_we_n_p0和onfi_we_n_p1,用于关联nand颗粒的写使能接口;

16、写保护控制信号onfi_wp_n_p0和onfi_wp_n_p1,用于关联nand颗粒的写保护接口;

17、状态指示信号onfi_rb_n,用于关联nand颗粒的状态接口。

18、根据本技术提供的一种基于onfi phy接口规范的内存访问方法,所述数据总线信号子集中的交互信号包括:

19、写入数据指示信号onfi_wrdata_p0和onfi_wrdata_p1,用于指示向nand颗粒中写入的数据;

20、写入数据使能信号onfi_wrdata_en_p0和onfi_wrdata_en_p0,用于与写入数据指示信号组合实现向nand颗粒写入数据;

21、读取数据指示信号onfi_rddata_p0和onfi_rddata_p1,用于指示从nand颗粒中读取的数据;

22、读取数据有效标识信号onfi_rddata_valid_p0和onfi_rddata_valid_p1,用于指示从nand颗粒中读取的有效数据;

23、读取数据使能信号onfi_rddata_en_p0和onfi_rddata_en_p1,用于与读取数据指示信号、读取数据有效标识信号组合实现从nand颗粒读取数据;

24、dqs状态指示信号onfi_wrdqs_toggle_p0和onfi_wrdqs_toggle_p1,用于指示dqs信号状态;

25、dqs发送使能信号onfi_wrdqs_en_p0和onfi_wrdqs_en_p1,用于与dqs状态指示信号组合产生dqs信号的发送时序。

26、根据本技术提供的一种基于onfi phy接口规范的内存访问方法,所述自定义信号子集中的交互信号包括:

27、请求信号onfi_ctrlupd_req,用于内存控制器向物理层发送请求以完成校准工作;

28、应答信号onfi_ctrlupd_ack,用于指示物理层的当前状态;

29、初始化状态信号onfi_init_complete,用于指示物理层是否初始化完成。

30、根据本技术提供的一种基于onfi phy接口规范的内存访问方法,onfi_re_toggle_p0、onfi_re_toggle_p1、onfi_wrdqs_toggle_p0和onfi_wrdqs_toggle_p1的数据位宽均为2,当取值为2’b00时,表示低电平,当取值为2’b01时表示高电平,当取值为2’b10时表示翻转,且翻转频率为内存控制器时钟频率的2倍。

31、根据本技术提供的一种基于onfi phy接口规范的内存访问方法,所述访问类型包括读数据和写数据。

32、本技术还提供一种基于onfi phy接口规范的内存访问装置,所述onfi phy接口规范定义了内存控制器与物理层之间的通用接口及对应的交互信号集合,所述装置包括:

33、第一确定模块,用于响应于用户的内存访问触发操作,确定待访问的目标nand颗粒及对应的访问类型;

34、第二确定模块,用于基于所述待访问的目标nand颗粒及对应的访问类型,确定所述交互信号集合中的目标交互信号及对应的控制时序;

35、访问控制模块,用于基于所述控制时序对所述目标交互信号的状态进行控制以实现对目标nand颗粒的访问。

36、本技术还提供一种非暂态计算机可读存储介质,其上存储有计算机程序,该计算机程序被处理器执行时实现如上述任一种所述基于onfi phy接口规范的内存访问方法的步骤。

37、本技术还提供一种计算机程序产品,包括计算机程序,所述计算机程序被处理器执行时实现如上述任一种所述基于onfi phy接口规范的内存访问方法的步骤。

38、本技术提供的基于onfi phy接口规范的内存访问方法和装置,所述onfi phy接口规范定义了内存控制器与物理层之间的通用接口及对应的交互信号集合,所述方法包括:响应于用户的内存访问触发操作,确定待访问的目标nand颗粒及对应的访问类型;基于所述待访问的目标nand颗粒及对应的访问类型,确定所述交互信号集合中的目标交互信号及对应的控制时序;基于所述控制时序对所述目标交互信号的状态进行控制以实现对目标nand颗粒的访问,能够基于所述onfi phy接口规范实现内存的高效访问,同时,能够避免onfi controller和onfi phy两部分的设计者不同导致每次均需要针对性设计对应的硬件电路和内存访问方法,进而提高芯片的研发效率,降低设计成本。

- 还没有人留言评论。精彩留言会获得点赞!