芯片验证方法及装置、芯片验证系统和可读存储介质与流程

本技术涉及集成电路,具体而言,涉及一种芯片验证方法及装置、芯片验证系统和可读存储介质。

背景技术:

1、随着大规模集成电路(integrated circuit,ic)技术的发展,芯片的逻辑规模和电路复杂程度越来越高,为了保证芯片质量,需要将芯片作为待测器件(design undertest,dut)进行准确快速的仿真验证。在对芯片进行仿真验证时,通常需要利用激励产生装置针对芯片产生测试信号,并将产生的测试信号输入到芯片中,以验证芯片响应测试信号的输出结果是否符合预期效果。

2、目前,就待验证芯片而言,通常需要多组测试信号才能实现较为全面的芯片验证效果,这便需要配置多个激励产生装置各自独立地随机产生一组测试信号。值得注意的是,芯片验证作业所需的多组测试信号往往在信号内容上存在数据关联关系,不同激励产生装置各自产生的测试信号的至少一种字段类型的实际字段内容需要满足特定关联约束关系(例如,激励产生装置a产生的测试信号a的字段“s”取值为1时,激励产生装置b的测试信号b的字段“s”也必须取值为1),但又因针对待验证芯片配置的多个激励产生装置各自独立运行,导致多个激励产生装置实质无法有效地向待验证芯片提供满足关联约束关系的多组测试信号,影响芯片验证质量。

技术实现思路

1、有鉴于此,本技术的目的在于提供一种芯片验证方法及装置、芯片验证系统和可读存储介质,能够通过同一管理设备统一地对存在数据关联关系的多种测试信号进行激励字段内容约束,使多种测试信号各自对应的激励产生设备所生成的作用于待验证芯片的激励信号实质满足关联约束关系,以降低激励出错概率,并有效提升芯片验证效率和芯片验证质量。

2、为了实现上述目的,本技术实施例采用的技术方案如下:

3、第一方面,本技术提供一种芯片验证方法,应用于芯片验证系统所包括的关联激励输出控制设备,其中所述芯片验证系统还包括多个激励产生设备,所述方法包括:

4、获取针对待验证芯片的存在数据关联关系的多种目标测试信号之间的激励字段约束关系;

5、基于所述激励字段约束关系构建目标激励控制信号,其中所述目标激励控制信号包括所述多种目标测试信号各自的满足所述激励字段约束关系的目标激励字段内容;

6、建立所述关联激励输出控制设备与所述多种目标测试信号各自对应的目标激励产生设备之间的通信连接,并将所述目标激励控制信号发送给各个目标激励产生设备,以使每个目标激励产生设备基于自身对应的目标激励字段内容生成目标激励信号,并将生成的所述目标激励信号发送给所述待验证芯片进行芯片功能验证和/或芯片性能验证。

7、在可选的实施方式中,所述激励字段约束关系包括至少一种激励字段类型在所述多种目标测试信号处的字段内容分布约束关系,所述获取针对待验证芯片的存在数据关联关系的多种目标测试信号之间的激励字段约束关系的步骤,包括:

8、获取所述待验证芯片的测试信号要求信息,其中所述测试信号要求信息包括测试所述待验证芯片所需的所有测试信号各自对应的信号特征信息;

9、对所有测试信号各自对应的信号特征信息进行信息比对,得到存在数据关联关系的多种目标测试信号均具备的至少一种激励字段类型,以及每种激励字段类型在所述多种目标测试信号处的字段内容分布约束关系。

10、在可选的实施方式中,所述基于所述激励字段约束关系构建目标激励控制信号的步骤,包括:

11、针对每种激励字段类型,按照与该激励字段类型对应的字段内容分布约束关系,随机生成各个目标测试信号的与该激励字段类型匹配的目标激励字段内容;

12、将所有激励字段类型以及每种激励字段类型在各个目标测试信号处对应的目标激励字段内容集成到同一控制信号中,得到所述目标激励控制信号。

13、第二方面,本技术提供一种芯片验证方法,应用于芯片验证系统所包括的多个激励产生设备中的每个激励产生设备,其中所述芯片验证系统还包括激励输出控制设备;所述方法包括:

14、获取来自所述激励输出控制设备的目标激励控制信号,其中所述目标激励控制信号包括针对待验证芯片的存在数据关联关系的多种目标测试信号各自的满足激励字段约束关系的目标激励字段内容;

15、从所述目标激励控制信号中提取与自身负责产生的期望测试信号适配的目标激励字段内容;

16、基于提取出的所述目标激励字段内容产生所述期望测试信号所指向的目标激励信号;

17、检测当前设备状态是否处于芯片验证触发状态,并在检测到当前设备状态处于芯片验证触发状态时,将产生的目标激励信号发送给所述待验证芯片进行芯片功能验证和/或芯片性能验证。

18、在可选的实施方式中,所述基于提取出的所述目标激励字段内容产生所述期望测试信号所指向的目标激励信号的步骤,包括:

19、按照预先配置的针对所述待验证芯片的期望测试信号的信号特征信息,随机生成匹配的初始激励信号;

20、按照提取出的所述目标激励字段内容,对所述初始激励信号中的字段类型适配的目标字段内容进行内容替换,得到所述目标激励信号。

21、第三方面,本技术提供一种芯片验证方法,应用于芯片验证系统,所述芯片验证系统包括关联激励输出控制设备及多个激励产生设备,所述方法包括:

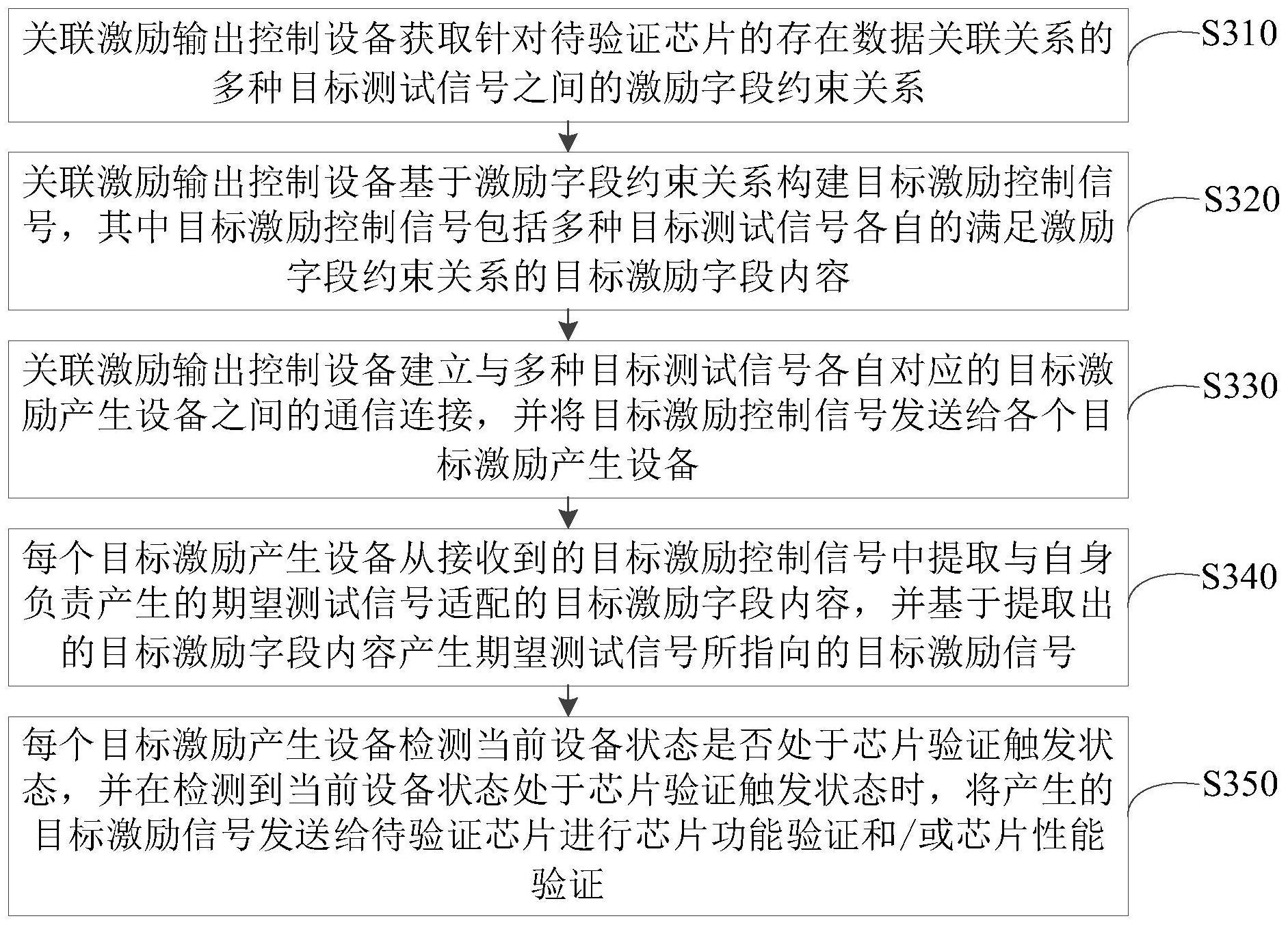

22、所述关联激励输出控制设备获取针对待验证芯片的存在数据关联关系的多种目标测试信号之间的激励字段约束关系;

23、所述关联激励输出控制设备基于所述激励字段约束关系构建目标激励控制信号,其中所述目标激励控制信号包括所述多种目标测试信号各自的满足所述激励字段约束关系的目标激励字段内容;

24、所述关联激励输出控制设备建立与所述多种目标测试信号各自对应的目标激励产生设备之间的通信连接,并将所述目标激励控制信号发送给各个目标激励产生设备;

25、每个所述目标激励产生设备从接收到的所述目标激励控制信号中提取与自身负责产生的期望测试信号适配的目标激励字段内容,并基于提取出的所述目标激励字段内容产生所述期望测试信号所指向的目标激励信号;

26、每个所述目标激励产生设备检测当前设备状态是否处于芯片验证触发状态,并在检测到当前设备状态处于芯片验证触发状态时,将产生的目标激励信号发送给所述待验证芯片进行芯片功能验证和/或芯片性能验证。

27、第四方面,本技术提供一种芯片验证装置,应用于芯片验证系统所包括的关联激励输出控制设备,其中所述芯片验证系统还包括多个激励产生设备,所述装置包括:

28、关联约束获取模块,用于获取针对待验证芯片的存在数据关联关系的多种目标测试信号之间的激励字段约束关系;

29、关联激励确定模块,用于基于所述激励字段约束关系构建目标激励控制信号,其中所述目标激励控制信号包括所述多种目标测试信号各自的满足所述激励字段约束关系的目标激励字段内容;

30、激励产生控制模块,用于建立所述关联激励输出控制设备与所述多种目标测试信号各自对应的目标激励产生设备之间的通信连接,并将所述目标激励控制信号发送给各个目标激励产生设备,以使每个目标激励产生设备基于自身对应的目标激励字段内容生成目标激励信号,并将生成的所述目标激励信号发送给所述待验证芯片进行芯片功能验证和/或芯片性能验证。

31、第五方面,本技术提供一种芯片验证装置,应用于芯片验证系统所包括的多个激励产生设备中的每个激励产生设备,其中所述芯片验证系统还包括激励输出控制设备;所述装置包括:

32、激励控制获取模块,用于获取来自所述激励输出控制设备的目标激励控制信号,其中所述目标激励控制信号包括针对待验证芯片的存在数据关联关系的多种目标测试信号各自的满足激励字段约束关系的目标激励字段内容;

33、关联激励提取模块,用于从所述目标激励控制信号中提取与自身负责产生的期望测试信号适配的目标激励字段内容;

34、激励信号产生模块,用于基于提取出的所述目标激励字段内容产生所述期望测试信号所指向的目标激励信号;

35、芯片测试控制模块,用于检测当前设备状态是否处于芯片验证触发状态,并在检测到当前设备状态处于芯片验证触发状态时,将产生的目标激励信号发送给所述待验证芯片进行芯片功能验证和/或芯片性能验证。

36、第六方面,本技术提供一种芯片验证系统,所述芯片验证系统包括关联激励输出控制设备及多个激励产生设备,其中每个激励产生设备用于针对待验证芯片产生作为测试信号的激励信号,每种测试信号对应一个激励产生设备;

37、所述关联激励输出控制设备可与多个激励产生设备通信连接,并与所述多个激励产生设备协同作业,以实现前述实施方式中任意一项所述的芯片验证方法。

38、第七方面,本技术提供一种可读存储介质,其上存储有计算机程序,所述计算机程序被运行时,驱动芯片验证系统实现前述实施方式中任意一项所述的芯片验证方法,其中所述驱动芯片验证系统包括关联激励输出控制设备及多个激励产生设备。

39、在此情况下,本技术实施例的有益效果可以包括以下内容:

40、本技术通过关联激励输出控制设备获取针对待验证芯片的存在数据关联关系的多种目标测试信号之间的激励字段约束关系,并对应构建出目标激励控制信号,使目标激励控制信号包括前述多种目标测试信号各自的满足该激励字段约束关系的目标激励字段内容,而后建立该关联激励输出控制设备与前述多种目标测试信号各自对应的目标激励产生设备之间的通信连接,并将构建出的该目标激励控制信号同步地发送给各个目标激励产生设备,使每个目标激励产生设备得以基于自身适配的目标激励字段内容生成目标激励信号,并将生成的目标激励信号发送给待验证芯片进行芯片功能验证和/或芯片性能验证,从而通过同一管理设备统一地对存在数据关联关系的多种测试信号进行激励字段内容约束,使多种测试信号各自对应的激励产生设备所生成的作用于待验证芯片的激励信号实质满足关联约束关系,以降低激励出错概率,并有效提升芯片验证效率和芯片验证质量。

41、为使本技术的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

- 还没有人留言评论。精彩留言会获得点赞!