指令处理方法、处理器、可读存储介质及电子设备与流程

本技术涉及计算机,特别是涉及一种指令处理方法、处理器、可读存储介质及电子设备。

背景技术:

1、中央处理器(central processing unit,简称cpu)是计算机系统的运算和控制核心。可以理解的,cpu能够处理指令。在cpu中,加载存储单元(load-store unit,lsu)是负责处理内存加载和存储操作的模块。即,lsu可以基于lsu指令将数据存储器(data memory)内的数据加载到寄存器堆(register file)的各个寄存器中,或者,将寄存器堆中的数据写入到数据存储器中。在一些情况下,当lsu在执行lsu指令时,会涉及到地址转换(addresstranslation),即根据lsu指令得到当前指令中涉及数据存储器的虚拟地址,然后根据虚拟地址找到对应数据存储器所要使用的物理地址,从而根据得到的物理地址对数据存储器加载或者写入。

2、可以理解的,地址变换高速缓存(translation lookaside buffer,tlb)可用于虚拟地址与物理地址之间的交互,即存储有虚拟地址(virtual address)和物理地址(physical address)的映射关系,支持虚拟地址和物理地址之间转换。

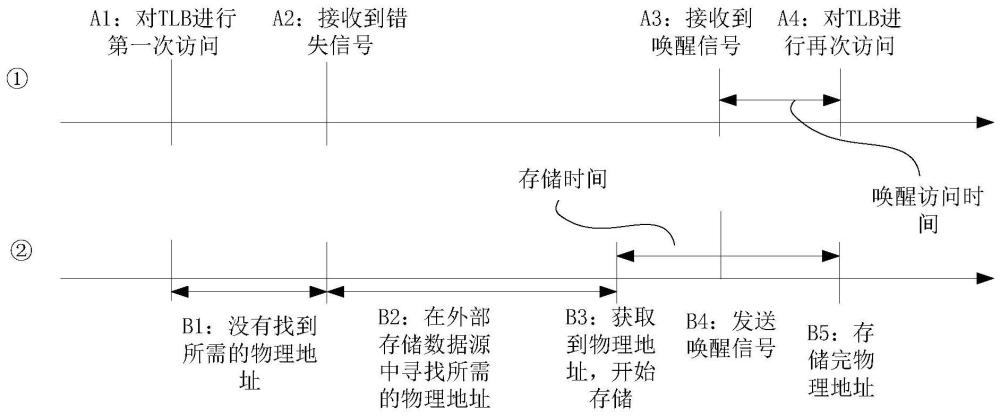

3、目前,当lsu执行lsu指令时,会对tlb访问以获取当前lsu指令中的虚拟地址所对应的物理地址。tlb中可能会没有存储当前lsu指令所需要的地址映射内容。可以理解的,由于lsu执行指令的过程采用流水线方式,在lsu无法获取到所需的物理地址的情况下,lsu会在流水线操作的某一个周期停止,即停滞。此时,tlb会从其他存储数据源中获取并且花费一段时间存储完所需的物理地址内容,然后在存储完成后给lsu一个唤醒信号以唤醒当前停滞的lsu。lsu接收到唤醒信号后需要花费一段时间重新执行上一次访问tlb之前所进行的操作(为了方便阐述,将lsu需要重新执行的上一次访问tlb之前所进行的操作简称为“回放操作”),例如,lsu对获取的lsu指令使用逻辑运算得到虚拟地址的操作过程。然后,lsu才能再次对tlb访问,以获取所需的物理地址内容。

4、但是,lsu在停滞之后需要花费较长时间才能再次从tlb中获取所需的物理地址内容,导致lsu执行当前指令的速度降低。

技术实现思路

1、为了解决上述问题,本技术提供了一种指令处理方法、处理器、可读存储介质及电子设备。

2、第一方面,本技术实施例提供了一种指令处理方法,应用于处理器,处理器包括加载存储单元和地址缓存单元,方法包括:加载存储单元获取第一指令;在地址缓存单元不存在对应第一指令的第一物理地址的情况下,加载存储单元接收地址缓存单元发送的第一错失信号;地址缓存单元从外部存储数据源中获取第一物理地址,并且向加载存储单元发送第一唤醒信号;地址缓存单元存储第一物理地址;加载存储单元基于第一唤醒信号,从地址缓存单元中获取第一物理地址;加载存储单元基于第一物理地址对第一指令进行处理。

3、可以理解的,当地址缓存单元(例如,下文的地址变换高速缓存)从外部存储数据源中获取第一物理地址,并且向加载存储单元发送第一唤醒信号,然后地址缓存单元再存储第一物理地址时,此时加载存储单元会提前获取到第一唤醒信号,避免在地址缓存单元存储完第一物理地址后,才获取到唤醒信号。因此,加载存储单元此时可以提前获取到所需的物理地址从而缩短地址缓存单元执行第一指令的处理时间,提高性能。

4、在上述第一方面的一种可能的实现中,地址缓存单元从外部存储数据源中获取第一物理地址,并且向加载存储单元发送第一唤醒信号,包括:地址缓存单元在从外部存储数据源中获取到第一物理地址后,经过第一发送时间,向加载存储单元发送第一唤醒信号。

5、可以理解的,第一发送时间可以预先根据当前处理器的性能进行配置。例如,可以使第一发送时间尽可能的小,此时,加载存储单元能够尽早接收到唤醒信号,从而加快执行对第一指令的处理。通过设置第一发送时间的方式,能够合理、科学的缩短第一指令的处理时间。

6、在上述第一方面的一种可能的实现中,第一发送时间大于等于第一发送时间阈值并且小于等于第二发送时间阈值,其中,第一发送时间阈值为第二存储时间与第三唤醒访问时间的差值,第二发送时间阈值为第三唤醒访问时间;并且,第二存储时间为地址缓存单元从外部存储数据源中获取到第一物理地址并且存储完第一物理地址所花费的时长;第三唤醒访问时间为加载存储单元接收到第一唤醒信号到对地址缓存单元进行第二访问所花费的时长;第二存储时间大于等于第三唤醒访问时间。

7、可以理解的,在第二存储时间大于等于第三唤醒访问时间时,第一发送时间大于等于第一发送时间阈值并且小于等于第二发送时间阈值。此时,可避免由于地址缓存单元还没有存储完第一物理地址,导致加载存储单元对地址缓存单元访问时无法得到第一物理地址的情况。

8、在上述第一方面的一种可能的实现中,第一发送时间小于等于第二存储时间,第二存储时间为地址缓存单元从外部存储数据源中获取到第一物理地址并且存储完第一物理地址所花费的时长。

9、在上述第一方面的一种可能的实现中,加载存储单元获取第一指令,包括:加载存储单元获取第一指令,并且基于第一指令得到第一虚拟地址;加载存储单元基于第一虚拟地址,对地址缓存单元进行第一访问。

10、在上述第一方面的一种可能的实现中,在地址缓存单元不存在对应第一指令的第一物理地址的情况下,加载存储单元接收地址缓存单元发送的第一错失信号,包括:地址缓存单元接收第一指令所对应的第一虚拟地址;地址缓存单元根据第一虚拟地址中的第一标识,在自身缓存单元中查找与第一标识匹配的物理地址;在地址缓存单元没有查找到与第一标识匹配的物理地址的情况下,确定地址缓存单元不存在第一物理地址;地址缓存单元向加载存储单元发送第一错失信号。

11、在上述第一方面的一种可能的实现中,加载存储单元基于第一唤醒信号,从地址缓存单元中获取第一物理地址,包括:加载存储单元根据第一唤醒信号,重新根据第一指令得到第一虚拟地址;加载存储单元根据第一虚拟地址对地址缓存单元进行第二访问,加载存储单元从地址缓存单元获取第一物理地址。

12、在上述第一方面的一种可能的实现中,还包括:加载存储单元基于第一指令得到第一寄存器地址编号;并且,加载存储单元基于第一物理地址对第一指令进行处理,包括:加载存储单元根据第一物理地址从数据存储器中加载待处理的数据,并且将待处理数据写入到对应第一寄存器地址编号的寄存器中;或者,加载存储单元根据第一寄存器地址编号从寄存器中加载待处理的数据,并且将待处理数据写入到对应第一物理地址的数据存储器中。

13、第二方面,本技术实施例提供了一种处理器,包括加载存储单元和地址缓存单元,加载存储单元被配置为获取第一指令;并且,在地址缓存单元不存在对应第一指令的第一物理地址的情况下,接收来自地址缓存单元的第一错失信号;地址缓存单元被配置为从外部存储数据源中获取第一物理地址,向加载存储单元发送第一唤醒信号并存储第一物理地址;以及加载存储单元还基于第一唤醒信号,从地址缓存单元中获取第一物理地址,并基于第一物理地址对第一指令进行处理。

14、第三方面,本技术实施例提供了一种计算机可读存储介质,计算机可读存储介质上存储有指令,该指令在电子设备执行上述第一方面以及第一方面的各种可能实现中的任一项的指令处理方法。

15、第三方面,本技术实施例提供了一种电子设备,包括:存储器,用于存储指令,以及一个或多个处理器,指令被一个或多个处理器执行时,处理器执行上述第一方面以及第一方面的各种可能实现中的任一项的指令处理方法。

16、第四方面,本技术实施例提供了一种计算机程序产品,计算机程序包含指令或者程序,当计算机程序产品在计算机上运行时,使得计算机执行如上述第一方面以及第一方面的各种可能实现中的任一项的指令处理方法。

- 还没有人留言评论。精彩留言会获得点赞!