一种设备中复杂可编程逻辑器件的升级方法、系统与流程

本发明涉及服务器,具体为一种设备中复杂可编程逻辑器件的升级方法、系统。

背景技术:

1、复杂可编程逻辑器件(complex programmable logic device,简称cpld)作为一种用户可根据自身需求自行构造逻辑功能的大规模数字集成电路,广泛应用于服务器主板中,承担服务器的电源开关控制、上电时序控制、异常监控等功能。

2、在服务器使用过程中,由于cpld程序存在功能优化、需求定制、异常问题等不同需求,需要对cpld中的fw(firmware,固件)进行升级,而目前通过基板管理控制器(boardmanagement controller,简称bmc)控制cpld在线升级的方法中,当cpld重新加载升级后的fw时,bmc复位信号会出现高电平-低电平-高电平的变化过程,即导致bmc被复位重启,从而使主板出现掉电异常,严重影响服务器性能的同时,降低了用户的使用体验。

技术实现思路

1、本发明实施例的目的在于提供一种设备中复杂可编程逻辑器件的升级方法、系统,解决现有技术中复杂可编程逻辑器件在升级过程中,基板管理控制器的被复位重启,导致主板出现掉电异常的问题,具体技术方案如下:

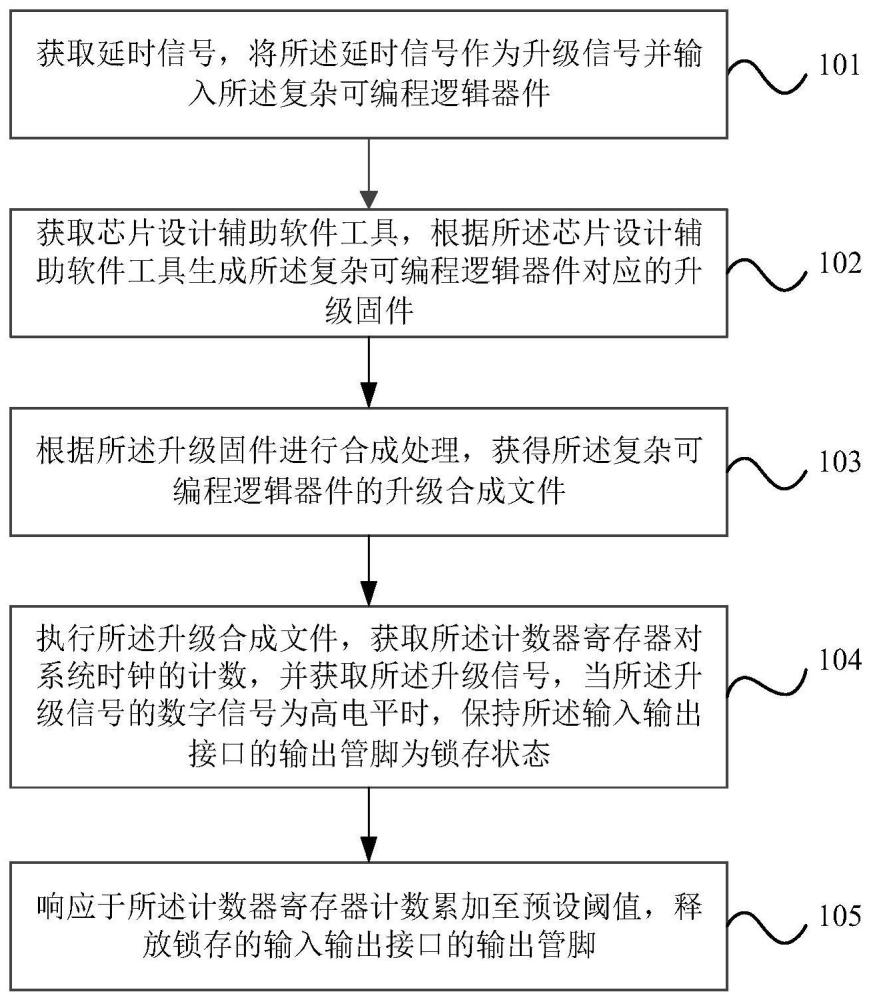

2、根据本技术实施例的第一方面,提供一种设备中复杂可编程逻辑器件的升级方法,所述设备包括基板管理控制器、复杂可编程逻辑器件,所述基板管理控制器与所述复杂可编程逻辑器件通信连接,所述复杂可编程逻辑器件中至少包括静态随机存取存储器、计数器寄存器、输入输出接口,所述方法包括:

3、获取延时信号,将所述延时信号作为升级信号并输入所述复杂可编程逻辑器件;

4、获取芯片设计辅助软件工具,根据所述芯片设计辅助软件工具生成所述复杂可编程逻辑器件对应的升级固件;

5、根据所述升级固件进行合成处理,获得所述复杂可编程逻辑器件的升级合成文件;

6、执行所述升级合成文件,获取所述计数器寄存器对系统时钟的计数,并获取所述升级信号,当所述升级信号的数字信号为高电平时,保持所述输入输出接口的输出管脚为锁存状态;

7、响应于所述计数器寄存器计数累加至预设阈值,释放锁存的输入输出接口的输出管脚。

8、可选地,在所述获取延时信号之前,还包括:

9、获取待机电压信号;

10、将经过延时芯片处理的待机电压信号设置为所述延时信号。

11、可选地,所述根据所述芯片设计辅助软件工具生成所述复杂可编程逻辑器件对应的升级固件,包括:

12、获取所述复杂可编程逻辑器件对应的升级代码,根据所述芯片设计辅助软件工具对所述升级代码进行编译,生成基层文件;

13、通过所述芯片设计辅助软件工具对所述基层文件进行转换,生成所述复杂可编程逻辑器件对应的升级固件。

14、可选地,所述升级合成文件由所述升级固件依次拼接生成,所述升级固件包括背景升级文件、芯片输出文件、代码管控文件、控制权收回文件、控制权转移文件,所述执行所述升级合成文件,包括:

15、通过所述基板管理控制器将所述升级合成文件发送至联合测试工作组接口,根据联合测试工作组接口执行所述升级合成文件;

16、其中,所述根据联合测试工作组接口执行所述升级合成文件,包括:

17、根据所述控制权收回文件获取所述复杂可编程逻辑器件的闪存控制权;

18、根据所述背景升级文件,对所述复杂可编程逻辑器件的闪存进行升级;

19、根据所述芯片输出文件,保持所述输入输出接口的输出管脚为锁存状态,并对所述复杂可编程逻辑器件的静态随机存取存储器进行升级;

20、根据所述代码管控文件下发代码指令,根据所述代码指令对所述输入输出接口的输出管脚进行状态控制;

21、根据所述控制权转移文件,控制所述基本管理控制器释放所述复杂可编程逻辑器件的闪存控制权。

22、可选地,所述获取所述计数器寄存器对系统时钟的计数,并获取所述升级信号,包括:

23、启动所述计数器寄存器;

24、根据系统时钟的上升沿数量,增加所述计数器寄存器的计数数值,当所述计数器寄存器的计数数值达到预设数值时,获取所述升级信号;

25、其中,所述计数器寄存器启动计数经过一段预设时间后,所述计数器寄存器的计数数值达到所述预设阈值。

26、可选地,在启动所述计数器寄存器之前,还包括:

27、响应于所述升级合成文件执行完成,对所述复杂可编程逻辑器件进行复位,并保持所述输入输出接口的输出管脚为锁存状态。

28、可选地,在所述释放锁存的输入输出接口的输出管脚之前,还包括:

29、当所述升级信号的数字信号为低电平时,所述复杂可编程逻辑器件未进行升级,释放所述锁存的输入输出接口的输出管脚。

30、根据本技术实施例的第二方面,提供一种设备中复杂可编程逻辑器件的升级系统,所述系统包括:

31、延时信号模块,用于获取延时信号,将所述延时信号作为升级信号并输入所述复杂可编程逻辑器件;

32、固件生成模块,用于获取所述复杂可编程逻辑器件对应的芯片设计辅助软件工具,根据所述芯片设计辅助软件工具生成所述复杂可编程逻辑器件对应的升级固件;

33、文件合成模块,用于根据所述升级固件进行合成处理,获得所述复杂可编程逻辑器件的升级合成文件;

34、执行模块,用于执行所述升级合成文件;

35、输出管脚控制模块,用于获取所述计数器寄存器对系统时钟的计数,并获取所述升级信号,当所述升级信号的数字信号为高电平时,保持所述输入输出接口的输出管脚为锁存状态;响应于所述计数器寄存器计数累加至预设阈值,释放锁存的输入输出接口的输出管脚。

36、根据本技术实施例的第三方面,提供一种电子设备,包括:

37、存储器、处理器及存储在所述存储器上并可在所述处理器上运行的程序;

38、其中,所述处理器被配置为读取所述存储器上的程序,实现如第一方面所述的设备中复杂可编程逻辑器件的升级方法。

39、根据本技术实施例的第四方面,提供一种非易失性可读存储介质,当所述非易失性可读存储介质中的指令由电子设备的处理器执行时,使得所述电子设备能够执行如第一方面所述的设备中复杂可编程逻辑器件的升级方法。

40、本技术实施例提供的技术方案可以包括以下有益效果:

41、本技术实施例公开的设备中复杂可编程逻辑器件的升级方法,其中,所述设备包括通信连接的基板管理控制器、复杂可编程逻辑器件,所述复杂可编程逻辑器件中至少包括静态随机存取存储器、计数器寄存器、输入输出接口,通过获取延时信号,将所述延时信号作为升级信号并输入所述复杂可编程逻辑器件;获取芯片设计辅助软件工具,根据所述芯片设计辅助软件工具生成所述复杂可编程逻辑器件对应的升级固件;根据所述升级固件进行合成处理,获得所述复杂可编程逻辑器件的升级合成文件;执行所述升级合成文件,获取所述计数器寄存器对系统时钟的计数,并获取所述升级信号,当所述升级信号的数字信号为高电平时,保持所述输入输出接口的输出管脚为锁存状态;响应于所述计数器寄存器计数累加至预设阈值,释放锁存的输入输出接口的输出管脚。本技术通过芯片设计辅助软件工具生成复杂可编程逻辑器件升级所需的升级固件,在复杂可编程逻辑器件重新加载固件的过程中,保持输入输出接口的输出管脚的锁存状态,有效避免复杂可编程逻辑器件发生信号复位时,输出信号对基板管理控制器的复位信号产生影响,进而导致服务器主板出现掉电异常现象,在寄存器稳定运行后,释放输入输出接口,重新按照执行逻辑进行信号输出,依据输出信号的状态保持实现复杂可编程逻辑器件的无感升级,从而保障在升级前与升级后,基板管理控制器的工作状态正常,提高用户体验的同时,提高服务器的性能。

42、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本技术。

- 还没有人留言评论。精彩留言会获得点赞!