低功耗芯片和电子设备的制作方法

本发明涉及芯片,尤其涉及一种低功耗芯片和一种电子设备。

背景技术:

1、随着芯片技术的快速发展和一些特殊场景的应用,低功耗技术越来越受到重视。在多种低功耗技术中,功耗控制和寄存器保持技术是较为常用的低功耗技术。

2、相关技术中,在芯片进入低功耗状态的过程中,状态数据存储通常使用单路读写的方式,芯片进入低功耗状态的时间较长。另外,芯片中存储的状态数据在存储器中可能出现数据翻转等错误,可靠性较差。

技术实现思路

1、本发明旨在至少在一定程度上解决相关技术中的技术问题之一。为此,本发明的第一个目的在于提出一种低功耗芯片。

2、本发明的第二个目的在于提出一种电子设备。

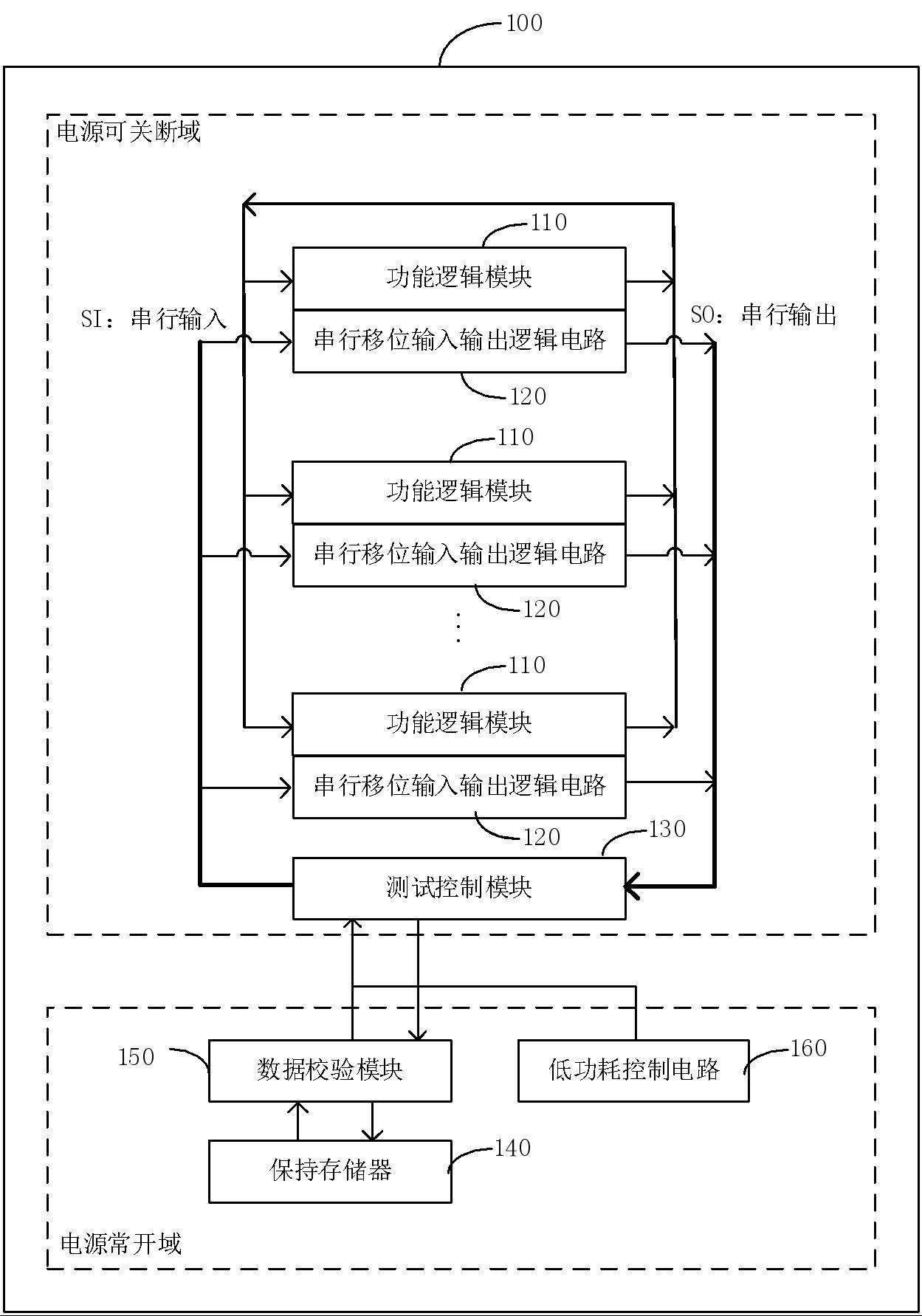

3、为达到上述目的,本发明第一方面实施例提出了一种低功耗芯片,包括:设置在电源可关断域的多个功能逻辑模块、多个串行移位输入输出逻辑电路、测试控制模块,每个所述串行移位输入输出逻辑电路对应一个功能逻辑模块设置,每个所述串行移位输入输出逻辑电路适于将对应的功能逻辑模块的状态数据输出给所述测试控制模块;设置在电源常开域的保持存储器、数据校验模块和低功耗控制电路,所述低功耗控制电路被配置为在所述芯片进入低功耗保持状态的情况下,控制所述数据校验模块与所述测试控制模块之间的第一数据传输通道打通,以便所述测试控制模块通过至少部分串行移位输入输出逻辑电路将对应的功能逻辑模块的状态数据整合后,再通过所述第一数据传输通道将整合后的状态数据发送给所述数据校验模块,所述数据校验模块被配置为对所述整合后的状态数据进行校验,以生成校验码,并将所述整合后的状态数据和所述校验码发送给所述保持存储器进行存储。

4、根据本发明实施例的低功耗芯片,在芯片需要进入低功耗保持状态时,低功耗控制电路控制数据校验模块与测试控制模块之间的第一数据传输通道打通,每个串行移位输入输出逻辑电路将存储在对应的功能逻辑模块中的状态数据串行输出至测试控制模块,测试控制模块将状态数据进行整合后,再将整合后的状态数据通过第一数据传输通道发送给数据校验模块以进行数据校验,并生成相应的校验码,数据校验模块将整合后的状态数据和校验码发送给保持存储器进行存储。由此,该芯片在进入低功耗保持状态时,多个串行移位输入输出逻辑电路通过多条链路读写的方式与测试控制模块进行对接,使得芯片进入低功耗保持状态的时间大大缩短,并且在存储状态数据之前对状态数据进行校验,提高了芯片的可靠性。

5、另外,根据本发明上述实施例的低功耗芯片,还可以具有如下的附加技术特征:

6、根据本发明的一个实施例,所述低功耗控制电路还被配置为,在所述芯片退出低功耗保持状态的情况下,控制所述数据校验模块与所述测试控制模块之间的第二数据传输通道打通,以便所述数据校验模块通过所述第二数据传输通道将校验通过的状态数据发送给所述测试控制模块,所述测试控制模块还被配置为对校验通过的状态数据进行整合,并将整合后的状态数据导入相应的串行移位输入输出逻辑电路,以便对应的功能逻辑模块调用。

7、根据本发明的一个实施例,上述的低功耗芯片,还包括:功能安全处理模块,适于处理所述芯片安全功能的报错,并对所述数据校验模块是否工作进行配置。

8、根据本发明的一个实施例,所述第一数据传输通道上设有第一选通器,所述第一选通器的第一端与所述测试控制模块的第一输出端相连,所述第一选通器的第二端分别与任意一个功能逻辑模块的输出端相连,所述第一选通器的第三端与所述数据校验模块的第一输入端相连,其中,所述低功耗控制电路在所述芯片进入低功耗保持状态的情况下,控制所述第一选通器的第一端与第三端连通,以便所述测试控制模块通过所述第一数据传输通道将整合后的状态数据发送给所述数据校验模块。

9、根据本发明的一个实施例,所述低功耗控制电路还被配置为,在所述芯片处于正常工作状态的情况下,如果所述数据校验模块被配置为处于停止工作状态,则控制所述第一选通器的第二端与第三端连通,以便各个功能逻辑模块将相应逻辑数据发送给所述保持存储器进行存储,并控制所述数据校验模块与各个功能逻辑模块之间的第三数据传输通道打通,以便各个功能逻辑模块调用所述保持存储器存储的逻辑数据。

10、根据本发明的一个实施例,所述第三数据传输通道设有第一与门,所述第一与门的第一输入端与所述数据校验模块的第一输出端相连,所述第一与门的第二输入端通过反相后与所述低功耗控制电路的存储器输入输出控制端相连,所述第一与门的输出端分别与各个功能逻辑模块的输入端相连,其中,在所述芯片处于正常工作状态的情况下,所述第一与门在所述低功耗控制电路的控制下,处于打通状态;在所述芯片进入低功耗保持状态的情况下,所述第一与门在所述低功耗控制电路的控制下,处于关闭状态。

11、根据本发明的一个实施例,所述第二数据传输通道设有第二与门,所述第二与门的第一输入端与所述数据校验模块的第一输出端相连,所述第二与门的第二输入端与所述低功耗控制电路的存储器输入输出控制端相连,所述第二与门的输出端与所述测试控制模块的第一输入端相连,其中,在所述芯片退出低功耗保持状态的情况下,所述第二与门在所述低功耗控制电路的控制下,处于打通状态。

12、根据本发明的一个实施例,所述功能逻辑模块包括:第三与门,所述第三与门的第一输入端和第二输入端作为所述功能逻辑模块的输入端,所述第三与门的输出端与对应的串行移位输入输出逻辑电路相连;第一与非门,所述第一与非门的第一输入端与所述第三与门的输出端相连,所述第一与非门的第二输入端与所述串行移位输入输出逻辑电路相连,所述第一与非门的输出端与所述串行移位输入输出逻辑电路相连;第一或门,所述第一或门的第一输入端与所述第三与门的第一输入端相连,所述第一或门的第二输入端与所述串行移位输入输出逻辑电路相连;第四与门,所述第四与门的第一输入端与所述第一或门的输出端相连,所述第四与门的第二输入端与所述串行移位输入输出逻辑电路相连,所述第四与门的输出端与所述串行移位输入输出逻辑电路相连;第二或门,所述第二或门的第一输入端与所述第四与门的第一输入端相连,所述第二或门的第二输入端与所述串行移位输入输出逻辑电路相连,所述第二或门的输出端作为所述功能逻辑模块的输出端。

13、根据本发明的一个实施例,所述串行移位输入输出逻辑电路包括:第二选通器,所述第二选通器的第一输入端与所述第三与门的输出端相连,所述第二选通器的第二输入端作为所述串行移位输入输出逻辑电路的扫描输入端;第一触发器,所述第一触发器的输入端与所述第二选通器的输出端相连,所述第一触发器的输出端与所述第一与非门的第二输入端相连;第三选通器,所述第三选通器的第一输入端与所述第一与非门的输出端相连,所述第三选通器的第二输入端与所述第一触发器的输出端相连;第二触发器,所述第二触发器的输入端与所述第三选通器的输出端相连,所述第二触发器的输出端与所述第四与门的第二输入端相连;第四选通器,所述第四选通器的第一输入端与所述第四与门的输出端相连,所述第四选通器的第二输入端与所述第二触发器的输出端相连;第三触发器,所述第三触发器的输入端与所述第四选通器的输出端相连,所述第三触发器的输出端与所述第二或门的第二输入端相连,且作为所述串行移位输入输出逻辑电路的输出端;其中,所述第二选通器的使能端、所述第三选通器的使能端和所述第四选通器的使能端相连,并适于接收使能信号;所述第一触发器的时钟端、所述第二触发器的时钟端和所述第三触发器的时钟端相连,并适于接收时钟信号。

14、为达到上述目的,本发明第二方面实施例提出了一种电子设备,包括上述的低功耗芯片。

15、根据本发明实施例的电子设备,通过上述的低功耗芯片,能够大大缩短进入低功耗保持状态的时间,并能够提高设备的可靠性。

16、本发明附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

- 还没有人留言评论。精彩留言会获得点赞!