一种用于实现高能效乘法运算的存内计算电路

本发明涉及一种用于实现高能效乘法运算的存内计算电路。

背景技术:

1、人工智能(artificial intelligence,ai)在各个领域得到了广泛的应用,同时也推动着“算力时代”的到来。与ai相关的算法,如深度神经网络(deep neural networks,dnn)、卷积神经网络(convolutional neural networks,cnn)等需要进行大量的数据处理。然而,大多数现代计算系统是以传统的冯诺依曼结构为基础建立的,物理结构上包括独立的计算单元和数据锁存单元,其在执行各种计算任务的过程中,需要在存储器和计算单元之间反复传输大量的数据,这将导致巨大的延迟和能量损耗,从而限制了数据处理的效率。由于处理器和存储设备长期非均衡的发展,使得存储器和处理器之间的速度差距越来越大,这种差距被称为“内存墙”,由此产生众所周知的冯·诺依曼瓶颈。只有解决冯诺依曼瓶颈,才能将人工智能应用到能耗和面积有严格限制的设备中(如物联网设备、可移动设备、可穿戴设备等),实现“人工智能无处不在”。为了克服传统冯诺依曼结构带来的计算限制,存内计算(computing in memory,cim)应运而生,其不需要将数据从存储器传输到处理器,直接将运算部分整合到存储阵列内部执行计算,这不仅减少了中间数据的传输,还减轻了处理器的运算量。在存内计算架构中,由于总线的带宽不再是吞吐量的限制因素,从而显著的提高了吞吐量和能效。存内计算的另一个显著的优势是能够实现多行读取,从而减少了存储访问的次数,增加了数据吞吐量。随着存内计算成为一个热门的研究领域,越来越多的学者开始从事这方面的研究,乘法计算、加减法运算以及逻辑运算都已通过存内计算实现。实现存内计算的载体包括静态随机存取存储器(static random-access memory,sram)、动态随机存储器(dynamic random-access memory,dram)、阻变随机存储器(resistiverandom access memory,rram)、相变随机存取存储器(phase change random accessmemory,pram)、闪存(flash memory)等多种易失性和非易失性存储器。由于静态随机存取存储器(static random-access memory,sram)数据锁存单元稳定性高、读取速度快、可擦写次数高,而且sram的制造工艺与先进的逻辑工艺兼容,基于sram的存内计算受到了学术界和工业界的广泛关注。

2、现有技术方案:现有的基于sram的存内计算实现技术可分为模拟存内计算(analog computing in memory,acim)和数字存内计算(analog computing in memory,dcim)两种。acim通常需要将输入的数字信号转换为模拟信号,与数据锁存单元存储的逻辑值进行单比特的模拟乘法运算,构成一个乘累加单元,同时激活多条字线,同一列上的乘累加单元产生的放电电流就可以进行求和,经模数转换电路转换为数字信号后,可供后级电路进行下一步运算操作。数字存内计算一般则是将数据锁存单元复用为逻辑运算单元,将单比特乘法(即按位与)转移到存内实现,在存储阵列外围实现移位累加器和加法器电路,完成乘累加运算。acim的优势是具有很高的能效,但是模拟计算的特性也导致其很容易受到工艺偏差、电压波动、电路噪声等因素的影响,因此计算精度通常都在8bit以下。acim架构中外围的数模转换和模数转换电路也带来了额外的开销。dcim避免了数据转换器的开销,也不存在计算精度损失,但是其能效比和面效比通常比模拟存内计算芯片差。

技术实现思路

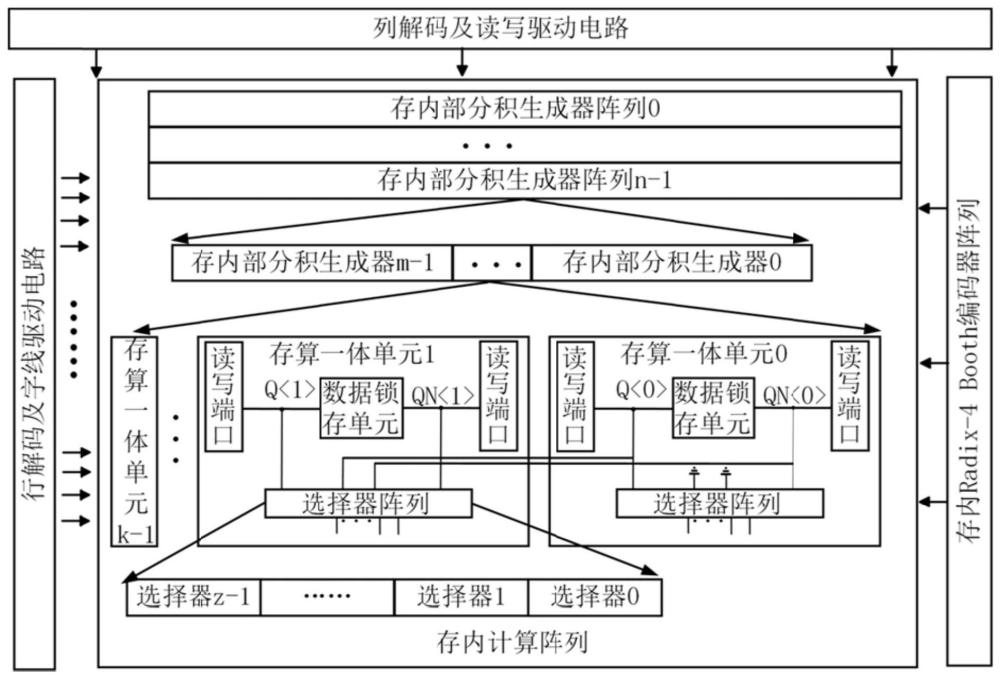

1、发明目的:本发明所要解决的技术问题是针对现有技术的不足,提供一种用于实现高能效乘法运算的存内计算电路,包括存内booth编码器阵列、行解码器及字线驱动电路、列解码器及读写驱动电路和存内计算阵列;

2、不同于传统的乘法器电路设计,本发明的上述所有部件都在存储器内部或紧邻存储器实现,因此可以消除或降低数据在乘法单元和存储器之间传输的开销。

3、所述存内计算电路有三种工作模式,分别是读、写和计算;

4、读、写模式下,行解码器的功能是选择存储器芯片中的特定行或单元以进行读取或写入,如果行解码器选择了某一行,字线驱动电路会生成必要的控制信号来激活所述行,从所述行读取数据或向所述行写入数据;列解码器的功能是选择已经被行解码器选中的存储器行中的特定列,当存储器系统接收到地址信号后,列解码器将进一步解码地址信号以确定要访问的存储器列;列解码器确保只有选定的存储器列上的数据被读取或写入;读写驱动电路控制数据的读取和写入操作,对于读操作,读写驱动电路将选择的存储器单元中的数据放大和输出给数据总线;对于写操作,读写驱动电路将数据从数据总线写入所选的存储器单元;读写驱动电路还包括数据的写入和读取时序控制;行解码器和列解码器协同工作以选择存储器中的特定数据单元,而字线驱动电路和读写驱动电路则负责激活和处理所选数据单元以进行读取或写入操作。这些组件在存储器系统中起到关键作用,确保数据能够有效地存储和检索。

5、计算模式下,存内booth编码器阵列接收乘数信号,输出booth编码信号;存内计算阵列在booth编码信号的控制下,对存储器存储的被乘数进行取反、移位操作,输出乘数与被乘数相乘所产生的所有部分积信号。

6、所述存内计算阵列包括n个存内部分积生成器阵列,每个存内部分积生成器阵列包括m个存内部分积生成器,每个存内部分积生成器包括k个存算一体单元;其中,n是存内计算阵列的行数,k是被乘数的位宽,k*m是存内计算阵列的列数。

7、每个存算一体单元包括一个数据锁存单元、一对以上的读写端口和一个数据选择器阵列,数据选择器阵列包括z个数据选择器。

8、第i个数据锁存单元有两个互补的数据锁存节点q[i]和qn[i],其中i表示数据锁存单元的位置,0<<i<<k-1,k个数据锁存单元按照从低位到高位的顺序,从右到左存储k比特的被乘数。

9、读写端口在外围电路的控制下对存内计算阵列进行读写操作。

10、每个数据选择器都包括四个控制信号输入端two,twon,neg,negn,四个数据输入端w、2w、2wn和wn,一个数据输出端out;

11、two、twon、neg、negn由存内booth编码器阵列所产生,w、2w、2wn和wn由存算一体单元的数据锁存单元所产生。

12、利用存储器本身存在的互补锁存信号,并设计从右到左逐个级联k个存算一体单元的方式,在存内以零晶体管开销实现存内左移一位电路,进而产生radix-4 booth算法中所有可能的非零部分积待选信号。

13、在每个存内部分积生成器中存储一个被乘数,利用数据锁存单元中两个互补的锁存节点代表被乘数和被乘数的相反数,用临近数据锁存单元的两个互补锁存节点代表被乘数的两倍和被乘数的两倍的相反数,不增加额外的晶体管开销即实现取反和移位,产生基4booth算法所有可能的非零部分积,具体的实现方式是:第0个存算一体单元的数据选择器阵列的所有数据选择器的2w输入端接地,第0个存算一体单元的数据选择器阵列的所有数据选择器的2wn输入端接地,第0个存算一体单元的数据选择器阵列的所有数据选择器的w输入端与第0个存算一体单元的q[0]节点相连,第0个存算一体单元的数据选择器阵列的所有数据选择器的wn输入端与第0个存算一体单元的qn[0]节点相连;第x个存算一体单元的数据选择器阵列的所有数据选择器的2w输入端与第x-1个存算一体单元的q[x-1]节点相连,第x个存算一体单元的数据选择器阵列的所有数据选择器的2wn输入端与第x-1个存算一体单元的qn[x-1]节点相连,第x个存算一体单元的数据选择器阵列的所有数据选择器的w输入端与第x个存算一体单元的q[x]节点相连,第x个存算一体单元的数据选择器阵列的所有数据选择器的w输入端与第x个存算一体单元的qn[x]节点相连,其中,1<<x<<k-1。

14、每个存算一体单元的z个数据选择器各有一组独立的控制输入端,即{neg[0],negn[0],two[0],twon[0]}、{neg[1],negn[1],two[1],twon[1]},...,{neg[z-1],negn[z-1],two[z-1],twon[z-1]。其中neg[0],negn[0],two[0],twon[0]是第0个数据选择器的控制信号,以此类推;

15、每个存算一体单元的数据选择器都有独立的输出端,第x个存算一体单元的z个数据选择器的输出端记为{out0[x],out1[x],...,outz-1[x]},out0[x]是第x个存算一体单元的第0个数据选择器的输出信号。

16、k个存算一体单元的相同序号的部分积比特构成一个完整的部分积即{out0[0],out0[1],...,out0[k-1]}构成第0个部分积,{out1[0],out1[1],...,out1[k-1]}构成第1个部分积,以此类推,{outz-1[0],outz-1[1],...,outz-1[k-1]}构成第z-1个部分积;

17、所述存内部分积生成器能够在单个时钟周期同时生成z个部分积。

18、有益效果:(1)与现有的模拟存内计算电路的区别:本发明是全数字实现,不需要模数转换器将输入数据转换成数字信号,也不需要数模转换器将运算结果转换为数字信号,因而省去了数据转换器的面积和功耗开销;本发明所提出的方案抗干扰能力强,不易受到工艺偏差、电压波动、温度变化的影响,也不存在运算精度的损失。

19、(2)与现有的数字存内计算电路的区别:对于两个多比特数的乘法运算:i*w,其中i有n bits,w有m bits,现有的全数字实现方案是在单个时钟周期利用与门或者或非门实现单比特乘法,需要n个时钟周期得到n个部分积,然后将部分积移位求和,得到最终的乘法运算结果。而本发明在存内实现radix-4 booth算法,并且计算并行度可以根具体工艺和应用需求而定。本发明所提出的存内部分积生成器可以在最多n/2个时钟周期内得到所有部分积。相较于现有的串行计算方案,本发明的吞吐量至少可以提升2倍。由于经过booth编码以后部分积总数量减少了一半,能耗也得到了有效降低。因此本发明可以在有效提升运算速度的同时提升计算能效。

20、(3)本发明所提出的存内部分积生成器与现有booth乘法电路的区别:本发明有效利用数据锁存单元本身存在的互补信号以及存储器规整的阵列结构,以较低开销实现移位电路和多位选择器电路,以更低的面积和功耗获得部分积。

- 还没有人留言评论。精彩留言会获得点赞!