时钟延时调整电路、时钟延时调整方法、芯片及电子设备与流程

本技术涉及集成电路,特别是涉及一种时钟延时调整电路、时钟延时调整方法、芯片及电子设备。

背景技术:

1、在集成电路设计中,时钟信号是非常关键的,因为它用于协调各个部件的操作,确保数据在正确的时间被采样和处理。

2、然而,信号在从芯片到芯片、从板上的不同部分传输时会经历不同的延迟。这些板级延迟可能是由于信号通过不同的传输媒介(例如跨越不同的电路板、连接器、线缆等)而引起的。

3、因此,为了确保时钟信号和数据在各个芯片上同步,需要对时钟信号进行延迟调整。

技术实现思路

1、基于此,本技术提供了一种时钟延时调整电路、时钟延时调整方法、芯片及电子设备,用于对时钟信号进行延迟调整。

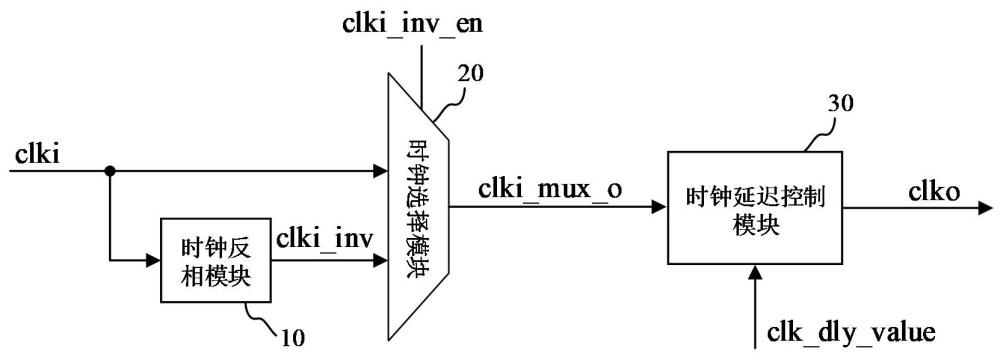

2、根据一些实施例,本技术一方面提供了一种时钟延时调整电路,包括时钟反相模块、时钟选择模块和时钟延迟控制模块;

3、所述时钟反相模块用于接入初始时钟信号,并输出反相初始时钟信号;

4、所述时钟选择模块包括第一输入端、第二输入端和第一输出端;所述时钟选择模块经所述第一输入端接入所述初始时钟信号,并经所述第二输入端与所述时钟反相模块相连接,以接入所述反相初始时钟信号;所述时钟选择模块响应于控制信号选择所述初始时钟信号或所述反相初始时钟信号作为中间时钟信号,并输出所述中间时钟信号;

5、所述时钟延迟控制模块包括第三输入端和第二输出端;所述时钟延迟控制模块经所述第三输入端与所述时钟选择模块的所述第一输出端相连接,以接入所述中间时钟信号;所述时钟延迟控制模块响应于延迟值配置信号对所述中间时钟信号进行延迟,形成目标时钟信号,并输出所述目标时钟信号。

6、在一些实施例中,所述延迟值配置信号的位宽为n;

7、所述时钟延迟控制模块包括2n-1个时钟延迟缓冲器和n-1级时钟选择器阵列;

8、2n-1个所述时钟延迟缓冲器依次相连,用于产生2n级单位延迟值;其中,每个所述时钟延迟缓冲器包括第四输入端和第三输出端,第一个所述时钟延迟缓冲器经所述第四输入端接入所述中间时钟信号,且任一所述时钟延迟缓冲器的所述第三输出端与相邻的下一所述时钟延迟缓冲器的所述第四输入端相连接;

9、n-1级所述时钟选择器阵列依次相连,用于选择并输出所述目标时钟信号;第一级所述时钟选择器阵列、第二级所述时钟选择器阵列…第n-1级所述时钟选择器阵列分别包括2n-1个、2n-2个…20个所述时钟选择器,每个所述时钟选择器包括两个时钟选择输入端和一个时钟选择输出端;且第一级所述时钟选择器阵列、第二级所述时钟选择器阵列…第n-1级所述时钟选择器阵列中的各所述时钟选择器分别以所述延迟值配置信号的第零位、第一位…第n-1位作为选择信号;

10、第一级所述时钟选择器阵列通过多个所述时钟选择输入端中的第一个所述时钟选择输入端接入所述中间时钟信号,且相邻的下一所述时钟选择输入端依次与2n-1个所述时钟延迟缓冲器中的第一个所述时钟延迟缓冲器、第二个所述时钟延迟缓冲器…第2n-1个所述时钟延迟缓冲器的所述第三输出端相连接;相邻的上一级所述时钟选择器阵列的多个所述时钟选择输出端中,每两个所述时钟选择输出端按照排列顺序分别对应连接至相邻的下一级所述时钟选择器阵列的一个时钟选择输入端;第n级所述时钟选择器阵列的所述时钟选择器的输出信号作为所述目标时钟信号。

11、在一些实施例中,所述时钟选择模块被配置为:

12、所述控制信号为0时,选择所述初始时钟信号作为中间时钟信号,并输出所述中间时钟信号;

13、所述控制信号为1时,选择所述反相初始时钟信号作为中间时钟信号,并输出所述中间时钟信号。

14、在一些实施例中,所述控制信号为0时,所述目标时钟信号相对于所述初始时钟信号的延迟值基于如下的公式确定:

15、tdelay=tclki_mux+n*tmux+clk_dly_value*tbuf;

16、其中,tdelay为所述目标时钟信号相对于所述初始时钟信号的延迟值,tclki_mux为所述时钟选择模块的延迟值,tmux为所述时钟选择器的延迟值,clk_dly_value为所述延迟值配置信号的值,tbuf为所述时钟延迟缓冲器的延迟值。

17、在一些实施例中,所述控制信号为1时,所述目标时钟信号相对于所述初始时钟信号的延迟值基于如下的公式确定:

18、tdelay=tinv+tclki_mux+n*tmux+clk_dly_value*tbuf-tclki/2;

19、其中,tdelay为所述目标时钟信号相对于所述初始时钟信号的延迟值,tinv为所述时钟反相模块的延迟值,tclki_mux为所述时钟选择模块的延迟值,tmux为所述时钟选择器的延迟值,clk_dly_value为所述延迟值配置信号的值,tbuf为所述时钟延迟缓冲器的延迟值,tclki为所述初始时钟信号的周期。

20、在一些实施例中,所述延迟值配置信号的位宽根据数据采样建立时间而设置;所述目标时钟信号的数据采样保持时间覆盖所述数据采样建立时间。

21、在一些实施例中,所述数据采样建立时间大于或等于20ns;所述初始时钟信号的频率大于或等于10m;

22、所述延迟值配置信号的位宽大于或等于7。

23、在一些实施例中,所述数据采样建立时间大于或等于20ns;所述初始时钟信号的频率大于或等于10m;

24、所述延迟值配置信号的位宽大于或等于7;所述延迟值配置信号的值大于或等于23。

25、根据一些实施例,本技术另一方面还提供了一种时钟延时调整方法,包括:

26、获取数据采样建立时间;

27、提供如前述实施例中所述的时钟延时调整电路,并根据所述数据采样建立时间对n的值进行设置,以使所述目标时钟信号的数据采样保持时间覆盖所述数据采样建立时间。

28、根据一些实施例,本技术又一方面还提供了一种芯片,包括如前述实施例中所述的时钟延时调整电路。

29、根据一些实施例,本技术再一方面还提供了一种电子设备,包括如前述实施例中所述的时钟延时调整电路,或者如前述实施例中所述的芯片。

30、本技术提供的时钟延时调整电路、时钟延时调整方法、芯片及电子设备可以/至少具有以下意想不到的优点:

31、在本技术实施例中,时钟反相模块用于接入初始时钟信号,并输出反相初始时钟信号;时钟选择模块可以响应于控制信号选择初始时钟信号或反相初始时钟信号作为中间时钟信号,并输出中间时钟信号至时钟延迟控制模块;时钟延迟控制模块响应于延迟值配置信号对中间时钟信号进行延迟,形成目标时钟信号,并输出目标时钟信号。如此,通过设置时钟反相模块并在控制信号的作用下可以实现目标时钟信号相对于初始时钟信号的正延迟控制或负延迟控制,并且还可以通过延迟值配置信号对时钟延迟控制模块的延迟值进行配置,从而对目标时钟信号相对于初始时钟信号的延迟值进行调整,以对初始时钟信号进行精确的延迟调整。本技术实施例结构简单易于实现,制造成本较低;且能够覆盖较宽的频率范围,具有较高的兼容性。

- 还没有人留言评论。精彩留言会获得点赞!