数据读取装置、方法、设备和存储介质与流程

本申请涉及计算机,尤其涉及一种数据读取装置、方法、设备和存储介质。

背景技术:

1、psram(pseudo static random access memory,伪静态随机存储器)通常以独立颗粒形态出现,其数据接口无法像内嵌sram那样任意扩充数据总线宽度,而且在特定工艺下io(input/output,输入输出)的设计会限制psram的最高工作频率。数据总线宽度和工作频率的限制使得单个psram的带宽通常低于手机应用存储数据所需的总带宽,这时候需要增加psram并行工作来增加带宽。

2、在增加psram之后,将两个psram作为一个整体看待,由两个psram结合着存储数据,例如:将一个数据拆分为d0和d1,d0存储到psram#1,d1存储到psram#2。虽然在存储数据时使用两个psram可以增加带宽,但是在从两个psram中读取数据时却存在数据无法对齐的问题。这是因为即便两个psram型号一样,两个psram的内在物理特性也不完全相同,物理特性的不同将导致两个psram的读取延时可能不同,在这种情况下,就会出现两个psram针对同一个地址返回的数据无法被同时刻读取出的问题。

3、例如:以图1为例,读命令(inst)和读地址{a2,a1,a0}被同时发送到psram#1和psram#2的接口端,预期同时读出d0和d1,以便将各8bit的数据d0和d1组合成一个16bit的数据,再将该16bit的数据发送给显示模块。但是,由于psram#1和psram#2的读取延时不同且时间差无法预期,导致d0和d1无法同时刻被读出,其中:psram#1的读取延时为delaycycle1,psram#2的读取延时为delay cycle2,delay cycle1小于delay cycle2,d0先被读出,d1后被读出,d0和d1未对齐,导致d0和d1无法组合成一个更大位宽的数据,由于读取延时的存在,d1和d4被同时读出,d1和d4将组合成一个数据,最终出现数据错位的问题。

技术实现思路

1、本申请提供了一种数据读取装置、方法、设备和存储介质,以解决多psram读数据的情况下,容易无法对齐数据的问题。

2、针对上述技术问题,本申请技术方案是通过如下实施例来解决的:

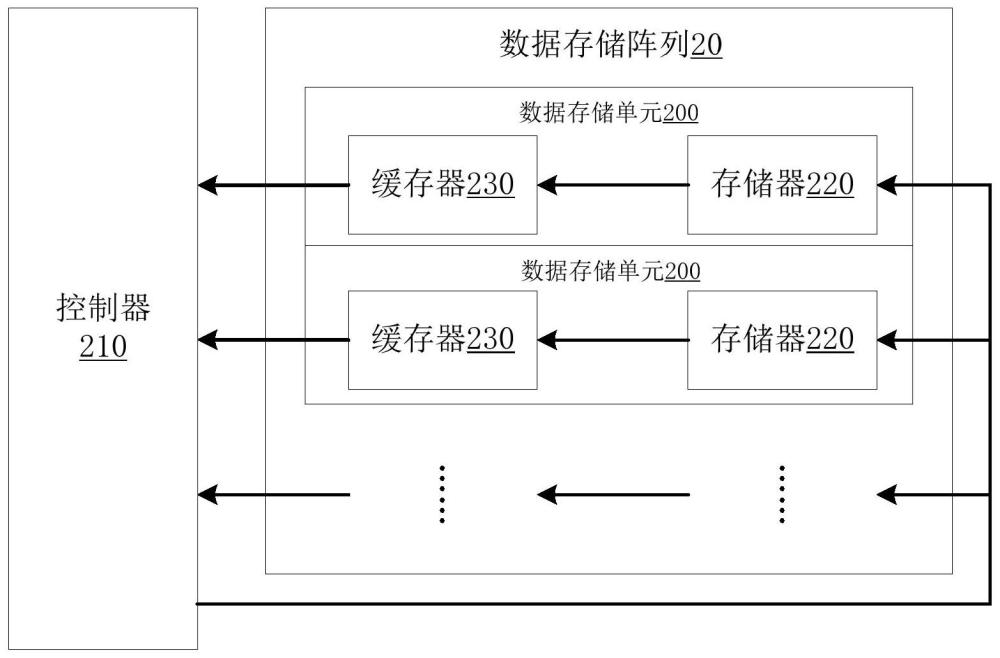

3、本申请实施例提供了一种数据读取装置,包括:控制器和数据存储阵列,所述数据存储阵列包括若干个数据存储单元,每个所述数据存储单元包括相互连接的存储器和缓存器;所述控制器的输出端连接每个所述存储器的输入端;所述控制器的输入端连接每个所述缓存器的输出端。

4、其中,所述存储器的类型包括:伪静态随机存储器psram和双倍速率ddr存储器;所述缓存器的类型为先进先出fifo缓存器。

5、本申请实施例还提供了一种基于上述所述装置执行的数据读取方法,包括:同时向多个存储器发送读命令和读地址;其中,针对每个所述存储器,所述存储器执行所述读命令,从所述读地址开始读取数据并写入所述存储器对应的缓存器中;在预设时间长度后,从多个所述缓存器分别获取数据;其中,所述预设时间长度大于或者等于数据读取时长;所述数据读取时长为读命令周期、读地址周期和多个所述存储器对应的最大延时周期的和;根据从多个所述缓存器分别获取的数据,生成对齐数据。

6、其中,多个所述缓存器都为fifo缓存器;其中,针对每个所述存储器,所述存储器从所述读地址开始在每个目标时钟沿读取一个数据并写入对应的fifo缓存器中;所述在预设时间长度后,从多个所述缓存器分别获取数据,包括:在预设时间长度后,在每个目标时钟沿从多个所述fifo缓存器的相同位置分别获取数据。

7、其中,所述根据从多个所述缓存器分别获取的数据,生成对齐数据,包括:将在相同目标时钟沿从多个所述fifo缓存器的相同位置获取的数据作为一个数据组合,并且,利用所述数据组合生成一个对齐数据。

8、其中,在下一次同时向多个存储器发送读命令和读地址之前,所述方法还包括:清空多个所述缓存器中未被获取的冗余数据。

9、本申请实施例还提供了一种基于上述所述装置执行的数据读取方法,包括:接收来自于控制器的读命令和读地址;执行所述读命令,从所述读地址开始读取数据;每读取一个数据,将所述数据写入到与所述存储器对应的缓存器中,以便所述控制器在预设时间长度后,从所述缓存器中获取所述数据。

10、其中,所述缓存器为fifo缓存器;所述从所述读地址开始读取数据,包括:从所述读地址开始,在每个目标时钟沿读取一个数据并写入对应的fifo缓存器中。

11、本申请实施例还提供一种基于上述任一项所述装置执行的数据读取方法,包括:控制器同时向多个存储器发送读命令和读地址;每个所述存储器接收来自于所述控制器的读命令和读地址;执行所述读命令,从所述读地址开始读取数据;每读取一个数据,将所述数据写入到与所述存储器对应的缓存器中;所述控制器在预设时间长度后,从多个所述缓存器分别获取数据;根据从多个所述缓存器分别获取的数据,生成对齐数据;其中,所述预设时间长度大于或者等于数据读取时长;所述数据读取时长为读命令周期、读地址周期和多个所述存储器对应的最大延时周期的和。

12、本申请实施例还提供了一种数据读取设备,包括:至少一个通信接口;与所述至少一个通信接口相连接的至少一个总线;与所述至少一个总线相连接的至少一个处理器;与所述至少一个总线相连接的至少一个存储单元,其中,所述处理器被配置为:执行所述存储单元中存储的数据读取程序,以实现上述的数据读取方法。

13、本申请实施例还提供了一种计算机可读存储介质,所述计算机可读存储介质存储有计算机可执行指令,所述计算机可执行指令被执行,以实现上述的数据读取方法。

14、本申请实施例提供的上述技术方案与现有技术相比具有如下优点:在本申请实施例中,该装置包括:控制器和数据存储阵列,所述数据存储阵列包括若干个数据存储单元,每个所述数据存储单元包括相互连接的存储器和缓存器;所述控制器的输出端连接每个所述存储器的输入端;所述控制器的输入端连接每个所述缓存器的输出端。控制器同时向多个存储器发送读命令和读地址;其中,针对每个所述存储器,所述存储器执行所述读命令,从所述读地址开始读取数据并写入所述存储器对应的缓存器中;在预设时间长度后,从多个所述缓存器分别获取数据;其中,所述预设时间长度大于或者等于数据读取时长;所述数据读取时长为读命令周期、读地址周期和多个所述存储器对应的最大延时周期的和;根据从多个所述缓存器分别获取的数据,生成对齐数据。本申请实施例将从存储器读取的数据先缓存到缓存器,利用缓存器对数据做中间缓冲,等待来自于不同存储器的同一存储地址的数据都到齐之后,从缓存器获取来自不同存储器相同存储地址的数据,此时来自不同存储器相同存储地址的数据就实现了对齐,避免来自不同存储器相同存储地址的数据无法同时被读出,而出现的数据无法对齐的问题。

技术特征:

1.一种数据读取装置,其特征在于,包括:

2.根据权利要求1所述的装置,其特征在于,

3.一种基于权利要求1-2中任一项所述装置执行的数据读取方法,其特征在于,包括:

4.根据权利要求3所述的方法,其特征在于,

5.根据权利要求4所述的方法,其特征在于,所述根据从多个所述缓存器分别获取的数据,生成对齐数据,包括:

6.根据权利要求3所述的方法,其特征在于,在下一次同时向多个存储器发送读命令和读地址之前,所述方法还包括:

7.一种基于权利要求1-2中任一项所述装置执行的数据读取方法,其特征在于,包括:

8.根据权利要求7所述的方法,其特征在于,

9.一种基于权利要求1-2中任一项所述装置执行的数据读取方法,其特征在于,包括:

10.一种数据读取设备,其特征在于,包括:至少一个通信接口;与所述至少一个通信接口相连接的至少一个总线;与所述至少一个总线相连接的至少一个处理器;与所述至少一个总线相连接的至少一个存储单元,其中,所述处理器被配置为:执行所述存储单元中存储的数据读取程序,以实现权利要求3-8中任一项所述的数据读取方法。

11.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质存储有计算机可执行指令,所述计算机可执行指令被执行,以实现权利要求3-8中任一项所述的数据读取方法。

技术总结

本申请涉及一种数据读取装置、方法、设备和存储介质。该装置包括:控制器和数据存储阵列,所述数据存储阵列包括若干个数据存储单元,每个所述数据存储单元包括相互连接的存储器和缓存器;所述控制器的输出端连接每个所述存储器的输入端;所述控制器的输入端连接每个所述缓存器的输出端。本申请利用缓存器做中间缓冲,等待来自于不同存储器的同一存储地址的数据都到齐之后,从缓存器获取来自不同存储器相同存储地址的数据,避免来自不同存储器相同存储地址的数据无法同时被读出,而出现的数据无法对齐的问题。

技术研发人员:陈锋,吴凌云,张海越

受保护的技术使用者:上海水木蓝鲸半导体技术有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!