数据比较器、数据处理方法、芯片及电子设备与流程

本发明涉及计算机,特别是涉及一种数据比较器、数据处理方法、芯片及电子设备。

背景技术:

1、随着数字电子技术的不断发展,各类人工智能(artificial intelligence,ai)芯片的快速发展对于高性能数字比较器的要求也越来越高。神经网络算法作为智能芯片广泛应用的算法之一,其需要多次用到数据比较器进行数据大小比较运算。

2、通常,数据比较器主要是针对一些浮点数以及定点数进行比较运算,并不能对浮定点类型的数据进行比较运算,即数据比较器并不能对除浮点数以及定点数以外其它类型的数据进行比较运算,从而导致数据比较器的通用性较低。

技术实现思路

1、基于此,有必要针对上述技术问题,提供一种数据比较器、数据处理方法、芯片及电子设备。

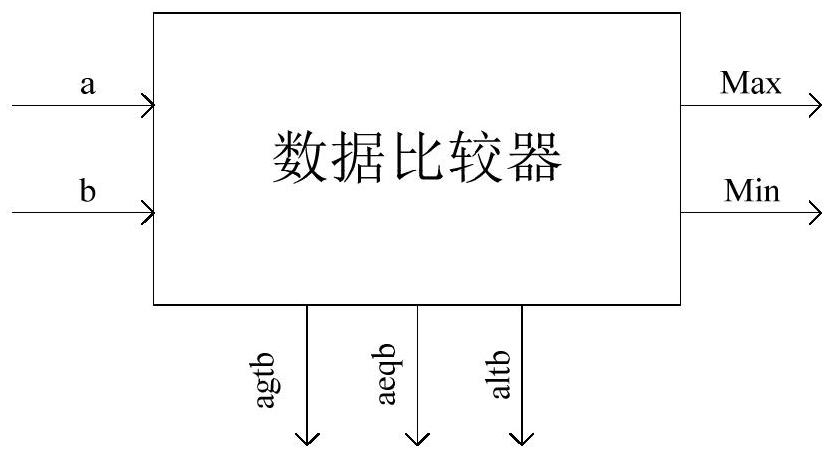

2、本发明实施例提供一种数据比较器,所述数据比较器包括:数据拆分电路、最高非零位比较电路以及数据比较电路,所述数据拆分电路的输出端与所述最高非零位比较电路的输入端连接,所述最高非零位比较电路的输出端与所述数据比较电路的输入端连接;

3、其中,所述数据拆分电路用于对接收到的第一数据以及第二数据分别进行拆分处理,得到所述第一数据中的第一尾数位数据和第一指数位数据,以及所述第二数据中的第二尾数位数据和第二指数位数据,所述最高非零位比较电路用于对接收到的所述第一尾数位数据和所述第二尾数位数据中,最高非零位的数位大小进行比较,所述数据比较电路用于对接收到的指数位数据和/或尾数位数据大小进行比较。

4、在其中一个实施例中,所述数据拆分电路包括数据输入端口、第一尾数位数据输出端口以及第一指数位数据输出端口;其中,所述数据输入端口用于输入所述第一数据以及所述第二数据,所述第一尾数位数据输出端口用于输出对所述第一数据以及所述第二数据进行拆分处理后,得到的第一尾数位数据以及第二尾数位数据,所述第一指数位数据输出端口用于输出对所述第一数据以及所述第二数据进行拆分处理后,得到的第一指数位数据以及第二指数位数据。

5、在其中一个实施例中,所述最高非零位比较电路包括:第一尾数位数据输入端口、第一指数位数据输入端口、第二尾数位数据输出端口、第二指数位数据输出端口、最高非零位逻辑判断信号输出端口、最高非零位比较结果输出端口;

6、其中,所述第一尾数位数据输入端口用于接收所述数据拆分电路输入的所述第一尾数位数据以及所述第二尾数位数据,所述第一指数位数据输入端口用于接收所述数据拆分电路输入的所述第一指数位数据以及所述第二指数位数据,所述第二尾数位数据输出端口用于输出所述第一尾数位数据以及所述第二尾数位数据,所述第二指数位数据输出端口用于输出所述第一指数位数据以及所述第二指数位数据,所述最高非零位逻辑判断信号输出端口用于输出逻辑判断信号,所述最高非零位比较结果输出端口用于输出所述第一尾数位数据以及所述第二尾数位数据中,最高非零位的数位大小的比较结果。

7、在其中一个实施例中,所述数据比较电路包括指数位比较模块以及尾数位比较模块,指数位比较模块的输出端与尾数位比较模块的输入端连接;其中,所述指数位比较模块用于对接收到的所述第一指数位数据以及所述第二指数位数据进行比较处理,所述尾数位比较模块用于对接收到的所述第一尾数位数据以及所述第二尾数位数据进行比较处理。

8、在其中一个实施例中,所述指数位比较模块包括:第二尾数位数据输入端口、第二指数位数据输入端口、第三尾数位数据输出端口、指数位逻辑判断信号输出端口、指数位比较结果输出端口;

9、其中,所述第二尾数位数据输入端口用于接收所述最高非零位比较电路,输入的所述第一尾数位数据以及所述第二尾数位数据,所述第二指数位数据输入端口用于接收所述最高非零位比较电路,输入的所述第一指数位数据以及所述第二指数位数据,所述第三尾数位数据输出端口用于输出所述第一尾数位数据以及所述第二尾数位数据,所述指数位逻辑判断信号输出端口用于输出逻辑判断信号,所述指数位比较结果输出端口用于输出所述第一指数位数据以及所述第二指数位数据的大小比较结果。

10、在其中一个实施例中,所述尾数位比较模块包括:第三尾数位数据输入端口、尾数位比较结果输出端口;其中,所述第三尾数位数据输入端口用于接收所述指数位比较模块输入的所述第一尾数位数据以及所述第二尾数位数据,所述尾数位比较结果输出端口用于输出所述第一尾数位数据和所述第二尾数位数据的大小比较结果。

11、本实施例提供的一种数据比较器,数据拆分电路用于对接收到的所述第一数据以及所述第二数据进行拆分处理,得到第一尾数位数据,第二尾数位数据,第一指数位数据以及第二指数位数据,并将第一尾数位数据和第二尾数位数据输入至尾数位最高非零位比较电路,对尾数位数据中最高非零位的数位进行比较运算得到比较结果,并根据该比较结果就可以确定接收到的数据是否需要通过下一数据比较电路,对两个尾数位数据和/或两个指数位数据进行比较处理,如果不需要进行下一数据比较电路处理,则结束运算获得运算结果,否则数据拆分电路就会继续将得到的两个尾数位数据和两个指数位数据,输入至数据比较电路中,当数据比较电路输出高电平信号时,结束运算获得运算结果,该过程可以减少运算量,节省运算时间;另外,该数据比较器能够对浮定点数进行比较运算,提高了数据比较器的通用性。

12、本发明实施例提供一种数据处理方法,所述方法包括:

13、接收待处理数据;

14、对所述待处理数据进行拆分处理,得到所述待处理数据中的指数位数据以及尾数位数据;

15、通过最高非零位比较电路,对所述尾数位数据中最高非零位的数位进行比较处理,得到比较结果;

16、根据所述比较结果,判断所述指数位数据和/或尾数位数据是否需要通过数据比较电路进行比较处理;

17、若需要,则所述最高非零位比较电路将所述指数位数据和所述尾数位数据,输入至所述数据比较电路,通过所述数据比较电路比较所述指数位数据和/或所述尾数位数据大小,得到运算结果。

18、在其中一个实施例中,所述根据所述比较结果,判断所述指数位数据和/或尾数位数据是否需要通过数据比较电路进行比较处理,包括:若所述比较结果为高电平信号,则判断所述指数位数据和/或尾数位数据不需要通过所述数据比较电路进行比较处理;若所述比较结果为低电平信号,则判断所述指数位数据和/或尾数位数据需要通过所述数据比较电路进行比较处理。

19、在其中一个实施例中,所述根据所述比较结果,判断所述指数位数据和/或尾数位数据是否需要通过数据比较电路进行比较处理之后,还包括:若不需要通过数据比较电路进行比较处理,则得到运算结果。

20、在其中一个实施例中,所述最高非零位比较电路将所述指数位数据和所述尾数位数据,输入至所述数据比较电路,通过所述数据比较电路比较所述指数位数据和/或所述尾数位数据大小,得到运算结果,包括:

21、通过指数位比较模块比较所述指数位数据是否相等;

22、若所述指数位数据相等,则通过所述尾数位比较模块比较所述尾数位数据是否相等;

23、若所述尾数位数据相等,则得到运算结果,结束运算。

24、在其中一个实施例中,所述通过所述比较模块比较所述指数位数据是否相等之后,还包括:若所述指数位数据不相等,则得到运算结果,结束运算。

25、在其中一个实施例中,所述通过所述尾数位比较模块比较所述尾数位数据是否相等之后,还包括:若所述尾数位数据不相等,则得到运算结果,结束运算。

26、本实施例提供的一种数据处理方法,通过指数位比较模块比较所述指数位数据是否相等,若所述指数位数据相等,则通过所述尾数位比较模块比较所述尾数位数据是否相等,若所述尾数位数据相等,则得到运算结果,结束运算,该方法可以对接收到的浮定点数进行比较运算,有效提高数据比较器的通用性。

27、本发明实施例提供的一种机器学习运算装置,该机器学习运算装置包括一个或者多个所述的数据比较器;该机器学习运算装置用于从其它处理装置中获取待运算数据和控制信息,并执行指定的机器学习运算,将执行结果通过i/o接口传递给其它处理装置;

28、当所述机器学习运算装置包含多个所述数据比较器时,所述多个所述数据比较器间可以通过特定的结构进行链接并传输数据;

29、其中,多个所述数据比较器通过pcie总线进行互联并传输数据,以支持更大规模的机器学习的运算;多个所述数据比较器共享同一控制系统或拥有各自的控制系统;多个所述数据比较器共享内存或者拥有各自的内存;多个所述数据比较器的互联方式是任意互联拓扑。

30、本发明实施例提供的一种组合处理装置,该组合处理装置包括如所述的机器学习处理装置、通用互联接口,和其它处理装置;该机器学习运算装置与上述其它处理装置进行交互,共同完成用户指定的操作;该组合处理装置还可以包括存储装置,该存储装置分别与所述机器学习运算装置和所述其它处理装置连接,用于保存所述机器学习运算装置和所述其它处理装置的数据。

31、本发明实施例提供的一种神经网络芯片,该神经网络芯片包括上述所述的数据比较器、上述所述的机器学习运算装置或者上述所述的组合处理装置。

32、本发明实施例提供的一种神经网络芯片封装结构,该神经网络芯片封装结构包括上述所述的神经网络芯片。

33、本发明实施例提供的一种板卡,该板卡包括上述所述的神经网络芯片封装结构。

34、本发明实施例提供了一种电子装置,该电子装置包括上述所述的神经网络芯片或者上述所述的板卡。

35、本发明实施例提供的一种芯片,包括至少一个如上述任一项所述的数据比较器。

36、本发明实施例提供的一种电子设备,包括如所述的芯片。

- 还没有人留言评论。精彩留言会获得点赞!