基于ATE设备的MCU内部时钟校准方法、系统及芯片与流程

本发明涉及半导体,尤其涉及的是一种基于ate设备的mcu内部时钟校准方法、系统及芯片。

背景技术:

1、目前,随着科技的飞速发展,微控制器芯片(microcontroller unit,mcu),又称单片机,在智能家居、医疗、汽车等领域的需求越来越大,对mcu芯片的精度要求也越来越高。为了在mcu外部无需设计震荡电路就能正常工作,mcu厂商都会设计一个或多个内部时钟信号,也就是内部rc振荡器。由于制造工艺的原因,相比外部时钟,内部时钟的精度和稳定性比较低,为了达到正常运作的要求,通常需要对时钟进行校准。

2、在现有的基于定时器(timer,简称tim)捕获的方案中,有的是通过增加分频电路,将mcu内部被校准时钟信号通过分频电路输出,该方案由于分频电路分频会产生一定的误差,倍频操作会进一步加大误差,而且当调整内部时钟的寄存器的位数较多时,算法过于繁杂,校准耗时较长,且成本较高。有的是通过由外部提供一个时钟信号源,mcu内部启动两个计数单元,第一计数单元用于累计外部基准时钟数目,第二计数单元用于累计监控芯片内部时钟产生组件的时钟数目,然后计算两个时钟数目的差值,并基于差值修调内部寄存器值进行校准。该方案需要利用外部时钟产生高频高精度的时钟信号,成本较高且校准耗时较长。

技术实现思路

1、鉴于上述现有技术的不足,本发明的目的在于提供一种基于ate设备的mcu内部时钟校准方法、系统及芯片,旨在解决现有的基于定时器捕获的方案需要额外增加分频电路或外部高频高精度时钟,致使成本高且校准耗时长的问题。

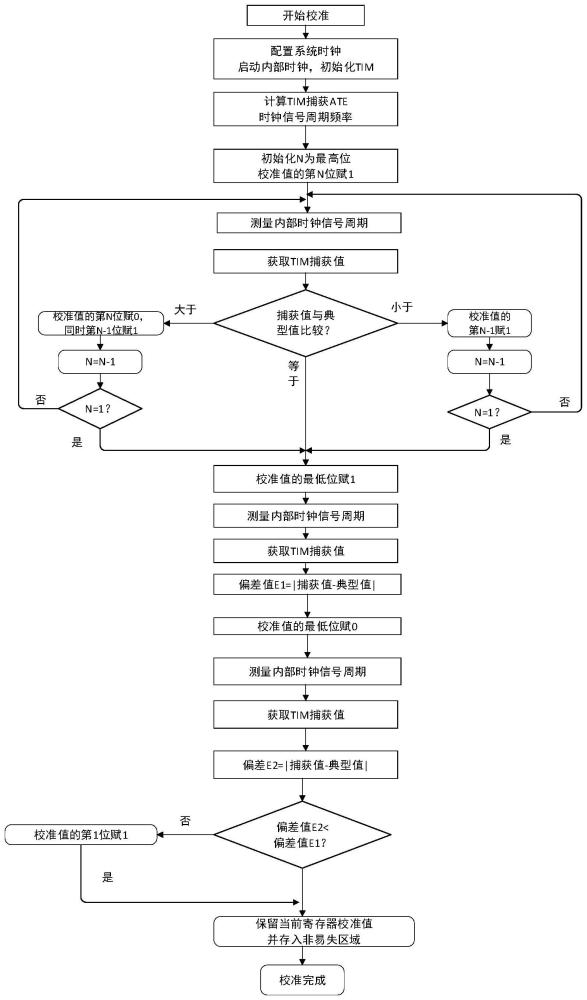

2、为了实现上述目的,本发明第一方面提供一种基于ate设备的mcu内部时钟校准方法,包括:

3、启动mcu的内部时钟,并获取所述内部时钟的目标校准频率;

4、基于所述目标校准频率,确定ate时钟的频率,所述ate时钟的频率为参考频率;

5、基于所述参考频率及所述目标校准频率,获得典型值;

6、利用所述内部时钟捕获所述ate时钟的实时频率,初始化所述内部时钟的寄存器的各个位的值,并基于所述实时频率和所述典型值,构建二分操作规则,从高位开始向低位逐位轮循调整相应位的值,获得校准后的内部时钟。

7、可选的,所述初始化所述内部时钟的寄存器的各个位的值,并基于所述实时频率和所述典型值,构建二分操作规则,从高位开始向低位逐位轮循调整相应位的值,获得校准后的内部时钟,包括:

8、初始化所述内部时钟的寄存器的各个位的值,获得所述寄存器在二进制下的中间值;

9、基于所述中间值,利用所述内部时钟捕获所述ate时钟的实时频率,并基于所述实时频率和所述目标校准频率,获得捕获值;

10、将所述捕获值和所述典型值进行比较,根据所述捕获值和所述典型值的对比结果,利用所述二分操作规则,从高位开始向低位逐位轮循调整相应位的值,直至所述捕获值等于所述典型值,或者调整到所述寄存器的最低位;

11、若调整的所述位为所述最低位,则分别调整所述最低位的值为0或1,获得在不同取值下对应的校准误差,根据所述校准误差确定所述最低位的值,并获得校准后的内部时钟。

12、可选的,所述根据所述捕获值和所述典型值的对比结果,利用所述二分操作规则,从高位开始向低位逐位轮循调整相应位的值,直至所述捕获值等于所述典型值,或者调整到所述寄存器的最低位,包括:

13、若所述捕获值大于所述典型值,则将所述寄存器的当前位赋值为0,将当前位的下一位赋值为1;若所述捕获值小于所述典型值,则将所述寄存器的当前位的下一位赋值为1,并跳转至所述下一位,继续轮循调整,直至所述捕获值等于所述典型值,或者调整到所述寄存器的最低位。

14、可选的,所述基于所述最低位在不同取值下对应的校准误差,确定所述最低位的值,包括:

15、调整所述最低位为1,利用所述内部时钟捕获所述ate时钟的实时频率,获得第一捕获值;计算所述第一捕获值与所述典型值之差的绝对值,获得第一绝对差值;

16、调整所述最低位为0,利用所述内部时钟捕获所述ate时钟的实时频率,获得第二捕获值;计算所述第二捕获值与所述典型值之差的绝对值,获得第二绝对差值;

17、比较所述第一绝对差值与所述第二绝对差值,若所述第一绝对差值小于所述第二绝对差值,则将所述最低位赋值为1,否则将所述最低位赋值为0。

18、可选的,所述初始化所述内部时钟的寄存器的各个位的值,获得所述寄存器在二进制下的中间值,包括:

19、获取所述内部时钟的寄存器的所有位,确定所述寄存器在十进制下的最大值和最小值;

20、基于所述最大值和所述最小值,确定所述寄存器在十进制下的标准中间值;

21、基于所述标准中间值,确定所述寄存器的各个位在二进制下的值,获得所述寄存器在二进制下的中间值。

22、可选的,所述基于所述中间值,利用所述内部时钟捕获所述ate时钟的实时频率,并基于所述实时频率和所述目标校准频率,获得捕获值,包括:

23、基于所述中间值,确定所述内部时钟的时钟周期,并基于所述时钟周期,利用所述内部时钟捕获所述ate时钟的实时频率;

24、计算所述实时频率与所述目标校准频率的比值,获得所述捕获值。

25、可选的,所述基于所述参考频率及所述目标校准频率,获得典型值,包括:

26、获取所述内部时钟的稳定度和细调步进比例,并获取所述ate时钟的精度;

27、基于所述参考频率与所述目标校准频率的比值,获得典型值;

28、若所述典型值小于所述细调步进比例,则基于所述稳定度、所述细调步进比例及所述ate时钟的精度,获得典型值;

29、若所述典型值大于或等于所述细调步进比例,则基于所述稳定度、所述典型值及所述ate时钟的精度,获得典型值。

30、本发明第二方面提供一种基于ate设备的mcu内部时钟校准系统,所述系统包括:

31、目标校准频率获取模块,用于启动mcu的内部时钟,并获取所述内部时钟的目标校准频率;

32、参考频率获取模块,用于基于所述目标校准频率,确定ate时钟的频率,所述ate时钟的频率为参考频率;

33、典型值生成模块,用于基于所述参考频率及所述目标校准频率,获得典型值;

34、校准模块,用于利用所述内部时钟捕获所述ate时钟的实时频率,初始化所述内部时钟的寄存器的各个位的值,并基于所述实时频率和所述典型值,构建二分操作规则,从高位开始向低位逐位轮循调整相应位的值,获得校准后的内部时钟。

35、本发明第三方面提供一种芯片,所述芯片包括存储器、处理器、内部时钟以及存储在所述存储器上并可在所述处理器上运行的基于ate设备的mcu内部时钟校准程序,所述基于ate设备的mcu内部时钟校准程序被所述处理器执行时实现任意一项上述基于ate设备的mcu内部时钟校准方法的步骤。

36、本发明第四方面提供一种计算机可读存储介质,所述计算机可读存储介质上存储有基于ate设备的mcu内部时钟校准程序,所述基于ate设备的mcu内部时钟校准程序被处理器执行时实现任意一项上述基于ate设备的mcu内部时钟校准方法的步骤。

37、与现有技术相比,本方案的有益效果如下:

38、本发明的方法通过将被校准mcu的内部时钟作为定时器的工作时钟,去捕获由ate产生的高精度时钟,基于参考频率及目标校准频率,获得校准的参考对象,即典型值;通过初始化内部时钟的寄存器的各个位的值,并基于定时器捕获到的ate时钟的实时频率和典型值,构建二分操作规则,从高位开始向低位逐位轮循调整相应位的值,获得校准后的内部时钟。该方案在保证校准精度的前提下,能够降低测试成本;能够解决没有分频电路的mcu的内部时钟的矫正,无需设计分频电路,能够降低芯片制造成本;对ate设备的性能要求较低,提高了ate设备的适用范围,从而进一步降低了测试成本。

- 还没有人留言评论。精彩留言会获得点赞!