数据处理方法、装置、电子设备及介质

本公开涉及计算机领域和数据存储领域,具体地涉及一种数据处理方法、装置、电子设备及介质。

背景技术:

1、随着人工智能技术的快速发展,深度学习应用对硬件资源,尤其是内存的需求非常巨大,加剧了内存带宽和容量限制导致的性能瓶颈问题。深度学习应用作为服务器应用之一,表现出了更加广泛随机的数据访问特征,导致了数据访问的时间局限性较低。在时间局限性较差的情况下,行缓存机制的命中率低,会增加数据访问延迟和能耗。

技术实现思路

1、鉴于上述问题,本公开提供了一种数据处理方法、装置、电子设备及介质。

2、根据本公开的第一个方面,提供了一种数据处理方法,应用于缓存装置,上述缓存装置包括目标缓存区域和地址缓存区域,上述缓存装置与处理器通信连接,上述方法包括:

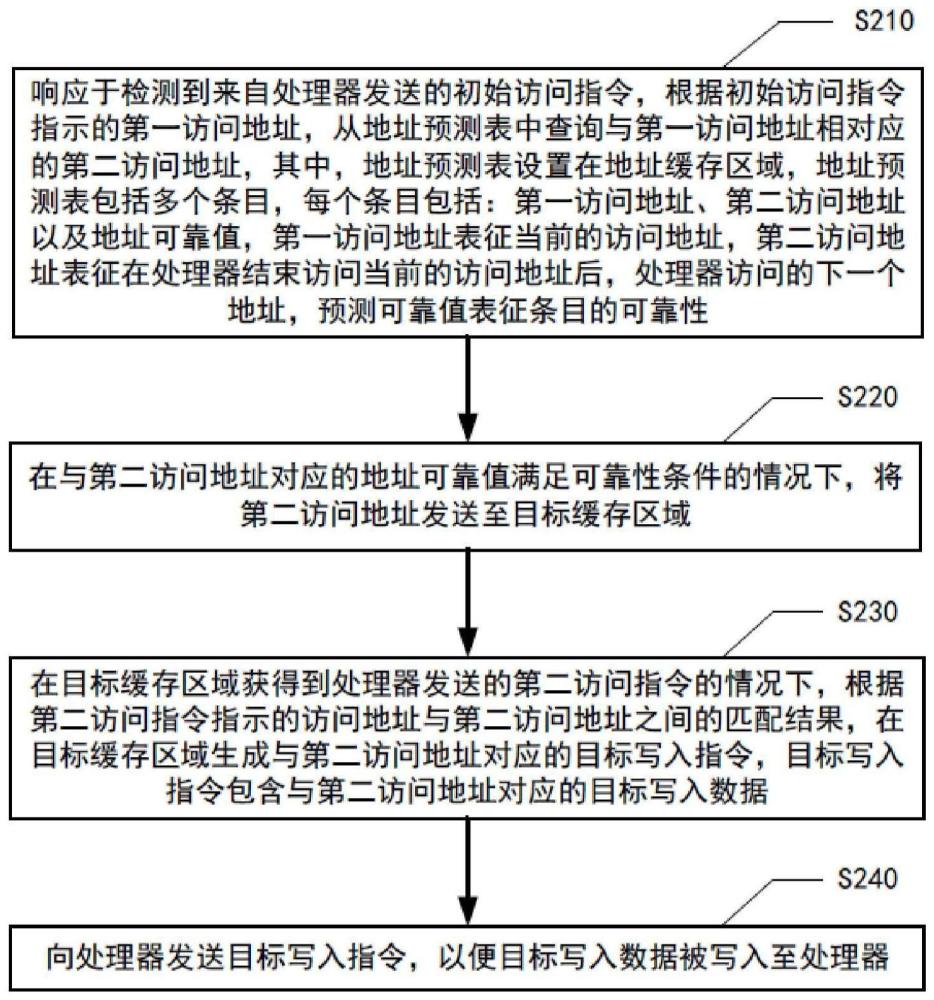

3、响应于检测到来自处理器发送的初始访问指令,根据上述初始访问指令指示的第一访问地址,从地址预测表中查询与上述第一访问地址相对应的第二访问地址,其中,上述地址预测表设置在上述地址缓存区域,上述地址预测表包括多个条目,上述每个条目包括:

4、上述第一访问地址、上述第二访问地址以及地址可靠值,上述第一访问地址表征当前的访问地址,上述第二访问地址表征在上述处理器结束访问上述当前的访问地址后,上述处理器访问的下一个地址,上述预测可靠值表征上述条目的可靠性;

5、在与上述第二访问地址对应的上述地址可靠值满足可靠性条件的情况下,将上述第二访问地址发送至上述目标缓存区域;

6、在上述目标缓存区域获得到上述处理器发送的第二访问指令的情况下,根据上述第二访问指令指示的访问地址与上述第二访问地址之间的匹配结果,在上述目标缓存区域生成与上述第二访问地址对应的目标写入指令,上述目标写入指令包含与上述第二访问地址对应的目标写入数据;以及

7、向上述处理器发送上述目标写入指令,以便上述目标写入数据被写入至上述处理器。

8、根据本公开的实施例,上述地址预测表是通过以下方式确定的,上述方式包括:

9、根据发送至上述地址缓存区域的第一时刻访问指令,确定第一时刻访问地址;

10、在初始地址预测表中确定与上述第一时刻访问地址对应的初始条目,其中,上述初始地址预测表包括上述初始条目,上述初始条目包括相关联的第一访问地址、第二访问地址和上述初始地址可靠值;

11、将与上述第一时刻访问地址对应的初始地址可靠值和预设阈值进行比较,得到比较结果;

12、在上述比较结果表征上述初始地址可靠值大于上述预设阈值的情况下,将与上述第一时刻访问地址相关联的第二访问地址输入上述目标缓存区域;

13、根据发送至上述地址缓存区域的第二时刻访问指令,确定第二时刻访问地址,其中,上述第二时刻访问指令与上述第一时刻访问指令为上述处理器在相邻的两个时刻发送的;

14、将上述第二时刻访问地址和与上述第一时刻访问地址对应的上述初始条目中的第二访问地址进行比对,得到的地址比对结果;以及

15、根据上述地址比对结果更新与上述第一时刻访问地址对应的上述初始条目中的初始地址可靠值,得到更新后的地址可靠值。

16、根据本公开的实施例,根据上述地址比对结果更新与上述第一时刻访问地址对应的上述初始条目中的初始地址可靠值包括:

17、在上述地址比对结果表征相匹配的情况下,基于预设正更新值更新与上述第一时刻访问地址对应的上述初始条目中的初始地址可靠值,得到更新后的第一地址可靠值;

18、在上述地址比对结果表征不匹配的情况下,基于预设负更新值更新与上述第一时刻访问地址对应的上述初始条目中的初始地址可靠值,得到更新后的第二地址可靠值,上述地址可靠值包括上述的第一地址可靠值和上述第二地址可靠值。

19、根据本公开的实施例,上述方式还包括:

20、在上述地址预测表中不存在上述第一时刻访问地址相匹配的初始条目的情况下,根据上述第一时刻访问地址更新上述地址预测表的至少一个空的初始条目。

21、根据本公开的实施例,上述方式还包括:

22、在发送至上述地址缓存区域的第二时刻访问指令,表征上述第二时刻访问指令包含的第二时刻访问地址与上述初始条目的第二访问地址不相同的情况下,在上述初始地址预测表中创建空的初始条目;以及

23、根据上述初始条目的第一访问地址和上述第二时刻访问地址更新上述空的初始条目。

24、根据本公开的实施例,根据上述第二访问指令指示的访问地址与上述第二访问地址之间的匹配结果,在上述目标缓存区域生成与上述第二访问地址对应的目标写入指令包括:

25、在上述匹配结果表征相匹配的情况下,在上述目标缓存区域生成与上述第二访问地址对应的上述目标写入指令。

26、根据本公开的实施例,还包括:

27、在上述匹配结果表征不匹配的情况下,将上述第二访问指令指示的访问地址发送至上述地址缓存区域。

28、本公开的第二方面提供了一种数据处理装置,包括:

29、第二访问地址查询模块,用于响应于检测到来自处理器发送的初始访问指令,根据上述初始访问指令指示的第一访问地址,从地址预测表中查询与上述第一访问地址相对应的第二访问地址,其中,上述地址预测表设置在上述地址缓存区域,上述地址预测表包括多个条目,上述每个条目包括:

30、上述第一访问地址、上述第二访问地址以及地址可靠值,上述第一访问地址表征当前的访问地址,上述第二访问地址表征在上述处理器结束访问上述当前的访问地址后,上述处理器访问的下一个地址,上述预测可靠值表征上述条目的可靠性;

31、第二访问地址发送模块,用于在与上述第二访问地址对应的上述地址可靠值满足可靠性条件的情况下,将上述第二访问地址发送至上述目标缓存区域;

32、目标写入指令生成模块,用于在上述目标缓存区域获得到上述处理器发送的第二访问指令的情况下,根据上述第二访问指令指示的访问地址与上述第二访问地址之间的匹配结果,在上述目标缓存区域生成与上述第二访问地址对应的目标写入指令,上述目标写入指令包含与上述第二访问地址对应的目标写入数据;以及

33、目标写入数据写入模块,用于向上述处理器发送上述目标写入指令,以便上述目标写入数据被写入至上述处理器。

34、本公开的第四方面还提供了一种计算机可读存储介质,其上存储有可执行指令,该指令被处理器执行时使处理器执行上述方法。

35、本公开的第五方面还提供了一种计算机程序产品,包括计算机程序,该计算机程序被处理器执行时实现上述方法。

36、根据本公开提供的一种数据处理方法、装置、电子设备及介质,该方法应用于缓存装置,缓存装置包括目标缓存区域和地址缓存区域,通过响应于检测到来自处理器发送的初始访问指令,根据初始访问指令指示的第一访问地址,在地址预测表中查询到与第一访问地址对应的第二访问地址,在第二访问地址对应的地址可靠值满足可靠性的条件下,将第二访问地址发送到目标缓存区域,在目标缓存区域获取到处理器发送的第二访问指令的情况下,根据第二访问指令指示的访问地址与第二访问地址一致的情况下,处理器会直接访问目标缓存区域中的数据,避免了处理器从访问延迟更大的地址缓存区域访问数据的步骤,从而可以有效降低数据处理中(dynamic random access memory,dram)访问延迟的问题,提升系统访问处理效率与整体效能。

- 还没有人留言评论。精彩留言会获得点赞!