一种内存排布位置确定方法、装置、设备及存储介质与流程

本技术属于电子设计,具体涉及一种内存排布位置确定方法、装置、设备及存储介质。

背景技术:

1、在电子设计自动化工具的自动布线过程中,各个数字模块标准单元的分布是有一定规律的,其中数字模块标准单元会聚集到关联的内存附近,如果这些内存布局较乱,那么关联的模块标准单元就会交错分布,标准单元之间的信号线也会交错连接,这样会导致区域绕线资源紧张,进而产生区域绕线阻塞。例如,在视频编解码模块中,存储内存占用了非常大的面积,数量也达到几百个。为了节省存储面积,前端设计在代码中会大量复用内存的情况,复用的内存会被多个模块调用,代码层次中不好把这些复用的内存划分到具体模块,所以都放在了缓存的靠前层次中。这样会导致后端在内存布局过程中,内存分类不明确,摆放不合理,从而产生严重的绕线阻塞问题。

2、相关技术中,可以降低内存的排布密度,增加内存之间的间隔来增加绕线资源,以解决绕线阻塞问题。

3、但是这种方法会增加内存之间的布线长度,从而增加了内存的通讯延时,导致硬件性能较低。

技术实现思路

1、本技术实施例的目的是提供一种内存排布位置确定方法、装置、设备及存储介质,能够解决相关技术中内存布线会导致通讯延时增大的问题。

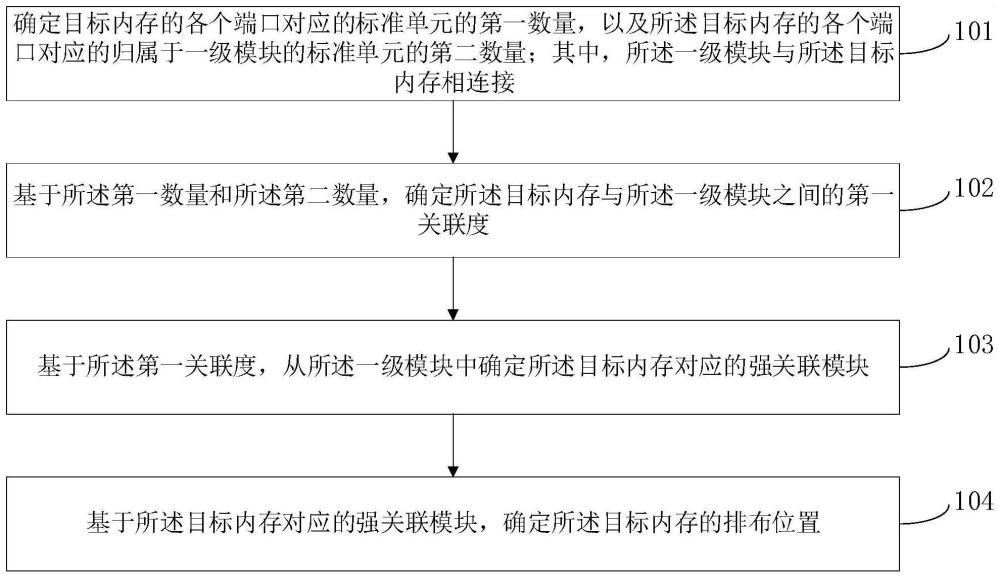

2、第一方面,本技术实施例提供了一种内存排布位置确定方法,所述方法包括:

3、确定目标内存的各个端口对应的标准单元的第一数量,以及所述目标内存的各个端口对应的归属于一级模块的标准单元的第二数量;其中,所述一级模块与所述目标内存相连接;

4、基于所述第一数量和所述第二数量,确定所述目标内存与所述一级模块之间的第一关联度;

5、基于所述第一关联度,从所述一级模块中确定所述目标内存对应的强关联模块;

6、基于所述目标内存对应的强关联模块,确定所述目标内存的排布位置。

7、可选地,所述基于所述第一数量和所述第二数量,确定所述目标内存与所述一级模块之间的第一关联度,包括:

8、基于所述第一数量和所述第二数量,确定所述目标内存的各个端口与所述一级模块分别对应的第一关联系数;

9、基于所述第一关联系数,确定所述目标内存与所述一级模块之间的第一关联度。

10、可选地,所述基于所述第一数量和所述第二数量,确定所述目标内存的各个端口与所述一级模块分别对应的第一关联系数,包括:

11、确定所述目标内存的各个端口对应的第一数量和所述各个端口对应所述一级模块的第二数量的第一差值;其中,所述第一差值与所述目标内存的端口和所述一级模块相对应;

12、确定所述第一差值的第一最小值和所述第一差值的第一最大值;

13、基于所述第一差值、所述第一最小值和所述第一最大值确定所述目标内存的各个端口与所述一级模块分别对应的第一关联系数。

14、可选地,所述基于所述第一关联系数,确定所述目标内存与所述一级模块之间的第一关联度,包括:

15、从所述第一关联系数中确定所述一级模块分别对应的关联系数;

16、对所述一级模块分别对应的第一关联系数分别求平均数,得到所述目标内存与所述一级模块之间的第一关联度。

17、可选地,所述基于所述第一关联度,从所述一级模块中确定所述目标内存对应的强关联模块,包括:

18、从所述第一关联度中确定大于或等于第一阈值的第二关联度;

19、基于所述第二关联度和所述一级模块的对应关系确定所述目标内存对应的强关联模块。

20、可选地,所述基于所述目标内存对应的强关联模块,确定所述目标内存的排布位置,包括:

21、在所述强关联模块的模块数量等于1的情况下,确定所述目标内存的排布位置为所述强关联模块的中间位置;

22、在所述强关联模块的模块数量大于1的情况下,将所述目标内存的排布位置,定为第一强关联模块与所述强关联模块中除所述第一强关联模块之外的其他强关联模块的交接处。

23、可选地,所述确定所述目标内存的排布位置为所述强关联模块的中间位置,包括:

24、确定所述目标内存的各个端口对应的归属于所述强关联模块的标准单元的第三数量,确定所述目标内存的各个端口对应的归属于二级模块的标准单元的第四数量;其中,所述二级模块归属于所述强关联模块,且与所述目标内存相连接;

25、基于所述第三数量和第四数量确定所述目标内存与所述二级模块之间的第二关联系数;

26、基于所述第二关联系数确定所述目标内存与所述二级模块之间的第三关联度;

27、基于所述第三关联度,从所述二级模块中确定所述目标内存对应的强关联二级模块;

28、基于所述目标内存对应的强关联二级模块,确定所述目标内存的排布位置为所述强关联模块的中间位置中与所述强关联二级模块相关联的对应位置。

29、可选地,所述将所述目标内存的排布位置,定为第一强关联模块与所述强关联模块中除所述第一强关联模块之外的其他强关联模块的交接处,包括:

30、确定所述第二关联度的最大值;

31、在所述第二关联度中确定与所述最大值差值最小的第四关联度;

32、确定所述目标内存的排布位置为第一强关联模块与所述第四关联度对应的强关联模块的交接处。

33、第二方面,本技术实施例提供了一种内存排布位置确定装置,所述装置包括:

34、第一确定模块,用于确定目标内存的各个端口对应的标准单元的第一数量,以及所述目标内存的各个端口对应的归属于一级模块的标准单元的第二数量;其中,所述一级模块与所述目标内存相连接;

35、第二确定模块,用于基于所述第一数量和所述第二数量,确定所述目标内存与所述一级模块之间的第一关联度;

36、第三确定模块,用于基于所述第一关联度,从所述一级模块中确定所述目标内存对应的强关联模块;

37、第四确定模块,用于基于所述目标内存对应的强关联模块,确定所述目标内存的排布位置。

38、可选地,所述第二确定模块,包括:

39、第一确定子模块,用于基于所述第一数量和所述第二数量,确定所述目标内存的各个端口与所述一级模块分别对应的第一关联系数;

40、第二确定子模块,用于基于所述第一关联系数,确定所述目标内存与所述一级模块之间的第一关联度。

41、可选地,所述第一确定子模块,包括:

42、第一确定单元,用于确定所述目标内存的各个端口对应的第一数量和所述各个端口对应所述一级模块的第二数量的第一差值;其中,所述第一差值与所述目标内存的端口和所述一级模块相对应;

43、第二确定单元,用于确定所述第一差值的第一最小值和所述第一差值的第一最大值;

44、第三确定单元,用于基于所述第一差值、所述第一最小值和所述第一最大值确定所述目标内存的各个端口与所述一级模块分别对应的第一关联系数。

45、可选地,所述第二确定子模块,包括:

46、第四确定单元,用于从所述第一关联系数中确定所述一级模块分别对应的关联系数;

47、第五确定单元,用于对所述一级模块分别对应的第一关联系数分别求平均数,得到所述目标内存与所述一级模块之间的第一关联度。

48、可选地,所述第三确定模块,包括:

49、第三确定子模块,用于从所述第一关联度中确定大于或等于第一阈值的第二关联度;

50、第四确定子模块,用于基于所述第二关联度和所述一级模块的对应关系确定所述目标内存对应的强关联模块。

51、可选地,所述第四确定模块,包括:

52、第五确定子模块,用于在所述强关联模块的模块数量等于1的情况下,确定所述目标内存的排布位置为所述强关联模块的中间位置;

53、第六确定子模块,用于在所述强关联模块的模块数量大于1的情况下,将所述目标内存的排布位置,定为第一强关联模块与所述强关联模块中除所述第一强关联模块之外的其他强关联模块的交接处。

54、可选地,所述第五确定子模块,包括:

55、第六确定单元,用于确定所述目标内存的各个端口对应的归属于所述强关联模块的标准单元的第三数量,确定所述目标内存的各个端口对应的归属于二级模块的标准单元的第四数量;其中,所述二级模块归属于所述强关联模块,且与所述目标内存相连接;

56、第七确定单元,基于所述第三数量和第四数量确定所述目标内存与所述二级模块之间的第二关联系数;

57、第八确定单元,用于基于所述第二关联系数确定所述目标内存与所述二级模块之间的第三关联度;

58、第九确定单元,用于基于所述第三关联度,从所述二级模块中确定所述目标内存对应的强关联二级模块;

59、第十确定单元,用于基于所述目标内存对应的强关联二级模块,确定所述目标内存的排布位置为所述强关联模块的中间位置中与所述强关联二级模块相关联的对应位置。

60、可选地,所述第六确定子模块,包括:

61、第十一确定单元,用于确定所述第二关联度的最大值;

62、第十二确定单元,用于在所述第二关联度中确定与所述最大值差值最小的第四关联度;

63、第十三确定单元,用于确定所述目标内存的排布位置为第一强关联模块与所述第四关联度对应的强关联模块的交接处。

64、第三方面,本技术实施例提供了一种电子设备,包括如上所述的内存排布位置确定装置,用以实现如上任一所述的内存排布位置确定方法。

65、第四方面,本技术实施例提供了一种可读存储介质,所述可读存储介质上存储程序或指令,所述程序或指令被处理器执行时实现如上任一所述的内存排布位置确定方法。

66、在本技术实施例中,提供一种内存排布位置确定方法,包括:确定目标内存的各个端口对应的标准单元的第一数量,以及目标内存的各个端口对应的归属于一级模块的标准单元的第二数量;其中,一级模块与目标内存相连接;基于第一数量和第二数量,确定目标内存与一级模块之间的第一关联度;基于第一关联度,从一级模块中确定目标内存对应的强关联模块;基于目标内存对应的强关联模块,确定目标内存的排布位置,可以根据内存和一级模块的关联度确定内存的最佳排布位置,能够减小各个模块及内存之间的布线长度,从而减小了线的延时和单元延时,提升了硬件性能。

- 还没有人留言评论。精彩留言会获得点赞!