自动化测试芯片中的测试单元、芯片、系统及测试方法与流程

本技术涉及芯片,特别涉及一种自动化测试芯片中的测试单元、芯片、系统及测试方法。

背景技术:

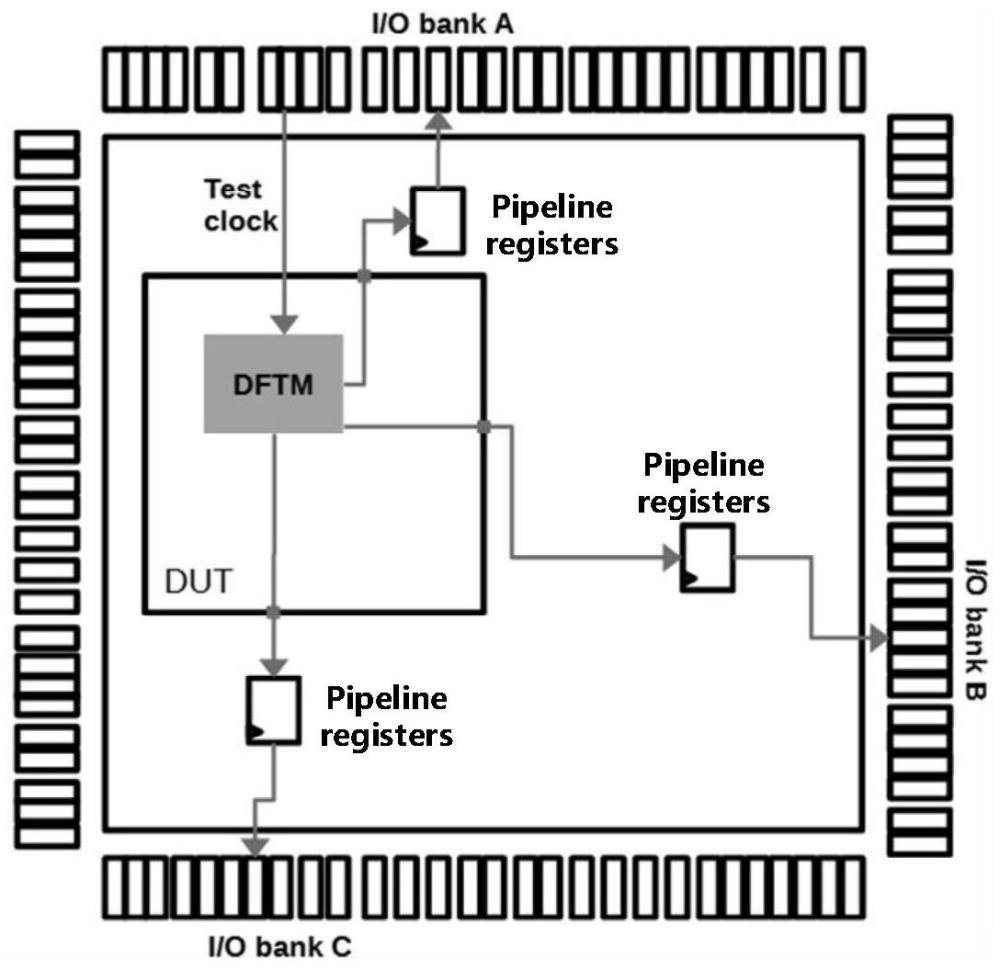

1、目前,soc(system on chip,片上系统)/mcu(microcontrollerunit,微控制单元)芯片的ate(automatic testequipment,自动化测试设备)测试原理如下:自动测试机台将时钟信号和测试数据等信号通过芯片i/o(input/output,输入输出接口)管脚输入到dut(device undertest,待测试模块)中的dftm(design-for-testmodule,测试逻辑控制模块)中,dftm通过解压缩逻辑对测试数据生成相应的测试向量(testpattern),再通过芯片中的扫描测试链(scan chain)将测试向量逐位移入芯片内部的寄存器中,接着对电路逻辑进行一次运算采样,将采样完的数据通过扫描测试链再送回到dftm中的压缩逻辑进行压缩,最终将压缩完的测试结果通过芯片i/o管脚返回自动测试机台进行观测,以验证测试是否通过。

2、当dut对应的i/o管脚位置分布较分散时,从扫描测试链上的寄存器穿过dftm中压缩解压缩逻辑到i/o管脚的路径会很长,导致延时很大,形成测试速率上限的瓶颈。为了解决这一问题,通常会在压缩解压缩逻辑和i/o管脚之间插入流水线寄存器(pipelineregister)来减小这段路径的延时,从而提高测试频率,降低测试成本。

3、当dut需要用到的i/o管脚数量较多,且多个i/o管脚分散在芯片的上下左右各个方向时,由于所有流水线寄存器都共用同一个dftm给出的测试时钟信号,而流水线寄存器的位置无法同时靠近所有i/o管脚,因此,存在某些流水线寄存器到i/o管脚的时序路径(timingpath)走线较长、延时过大的问题。而测试时钟频率受最长的路径的延时所决定,这使得最终能实现的测试最高频率变慢,芯片测试时间受此瓶颈限制无法缩短,最终导致测试成本增加。

技术实现思路

1、本技术提供了一种自动化测试芯片中的测试单元、芯片、系统及测试方法,用于解决相关技术中的i/o管脚分散在芯片的各个方向,且流水线寄存器无法同时靠近所有i/o管脚,导致测试时间较长,增加了测试成本的问题。所述技术方案如下:

2、根据本技术的第一方面,提供了一种自动化测试芯片中的测试单元,所述测试单元包括:一个待测试模块、n个流水线寄存器和n个i/o模块,n为正整数;其中,每个i/o模块中包括至少一个i/o管脚,且每个流水线寄存器位于对应的i/o模块与所述待测试模块组成的最短路径上;

3、所述待测试模块的时钟信号输入管脚与自动测试机台的时钟信号输出管脚相连,所述待测试模块的时钟信号输出管脚分别与n个流水线寄存器的时钟信号输入管脚相连;

4、所述待测试模块的测试数据输入管脚与自动测试机台的测试数据输出管脚相连,所述待测试模块的测试采样数据输出管脚分别与n个流水线寄存器的测试采样数据输入管脚相连;所述待测试模块用于根据所述测试数据生成测试采样数据;

5、每个流水线寄存器的测试采样数据输出管脚分别与对应的i/o模块的测试采样数据输入管脚相连。

6、在一种可能的实现方式中,所述待测试模块包括测试逻辑控制模块、扫描测试链和n个时钟门控逻辑模块;

7、所述测试逻辑控制模块的时钟信号输入管脚是所述待测试模块的时钟信号输入管脚,所述测试逻辑控制模块的测试数据输入管脚是所述待测试模块的测试数据输入管脚;

8、所述测试逻辑控制模块的测试向量输出管脚与所述扫描测试链的测试向量输入管脚相连,所述扫描测试链的测试采样数据输出管脚与所述测试逻辑控制模块的测试采样数据输入管脚相连;所述测试逻辑控制模块的测试采样数据输出管脚是所述待测试模块的测试采样数据输出管脚;

9、所述测试逻辑控制模块的时钟信号输出管脚分别与n个时钟门控逻辑模块的时钟信号输入管脚相连;

10、所述n个时钟门控逻辑模块的时钟信号输出管脚是所述待测试模块的时钟信号输出管脚。

11、在一种可能的实现方式中,所述测试逻辑控制模块用于将所述测试数据转换为所述测试向量;

12、所述扫描测试链用于根据所述测试向量进行运算采样,得到测试采样数据。

13、在一种可能的实现方式中,所述i/o模块的测试采样数据输出管脚与所述自动测试机台的测试采样数据输入管脚相连。

14、根据本技术的第二方面,提供了一种自动化测试芯片,所述自动化测试芯片包括:m个如上所述的测试单元,m为正整数。

15、根据本技术的第三方面,提供了一种自动化测试系统,所述自动化测试系统包括:如上所述的自动化测试芯片和自动测试机台。

16、根据本技术的第四方面,提供了一种自动化测试芯片中的测试方法,用于如上所述的自动化测试芯片中,所述方法包括:

17、所述待测试模块获取所述自动测试机台发送的时钟信号和测试数据;

18、所述待测试模块根据所述测试数据生成测试采样数据,并将所述时钟信号和所述测试采样数据分别发送给n个流水线寄存器;

19、每个流水线寄存器根据所述时钟信号将所述测试采样数据发送给对应的i/o模块进行输出。

20、在一种可能的实现方式中,当所述待测试模块中包括测试逻辑控制模块、扫描测试链和n个时钟门控逻辑模块时,所述待测试模块根据所述测试数据生成测试采样数据,并将所述时钟信号和所述测试采样数据分别发送给n个流水线寄存器,包括:

21、所述测试逻辑控制模块将所述测试数据转换为测试向量,将所述测试向量发送给所述扫描测试链;

22、所述扫描测试链根据所述测试向量进行运算采样,将得到的测试采样数据发送给所述测试逻辑控制模块,所述测试逻辑控制模块将所述测试采样数据分别发送给n个流水线寄存器;

23、所述测试逻辑控制模块将所述时钟信号分别发送给n个时钟门控逻辑模块;

24、每个时钟门控逻辑模块将所述时钟信号发送给对应的流水线寄存器。

25、在一种可能的实现方式中,所述测试逻辑控制模块将所述测试数据转换为测试向量,包括:

26、所述测试逻辑控制模块对所述测试数据进行解压缩,得到解压后的测试数据;

27、所述测试逻辑控制模块将所述解压后的测试数据转换为测试向量。

28、在一种可能的实现方式中,所述测试逻辑控制模块将所述测试采样数据分别发送给n个流水线寄存器:

29、所述测试逻辑控制模块对所述测试采样数据进行压缩,得到压缩后的测试采样数据;

30、所述测试逻辑控制模块将所述压缩后的测试采样数据分别发送给n个流水线寄存器。

31、本技术提供的技术方案的有益效果至少包括:

32、测试单元中包括n个流水线寄存器和n个i/o模块,将时钟信号和测试数据分别复制n份后,每个i/o模块对应于一个流水线寄存器、一组时钟信号和一组测试数据,这样,对应于不同的i/o模块,可以自由地调节待测试模块的时钟信号输出管脚和流水线寄存器的位置,不受其它i/o模块的位置的限制和影响,也就可以将流水线寄存器放置于对应的i/o模块与待测试模块组成的最短路径上,从而最大限度地缩短测试数据的输出路径,尽可能地减小测试数据到各i/o模块的时延,提高测试速率,减少测试时间,并降低测试成本。

- 还没有人留言评论。精彩留言会获得点赞!