串行接收器、串行收发器、芯片以及数据对齐方法与流程

本申请涉及数据传输,具体涉及一种串行接收器、串行收发器、芯片以及数据对齐方法。

背景技术:

1、在串行通道并行组合的场景下,由于印制电路板(printed circuit board,pcb)传输长度差异、跨通道电缆长度不匹配或者物态变化(例如压力(pressure)、体积(volume)以及温度(temperature)的变化,简称pvt变化)等原因,串行接收器接收到的多组串行数据之间可能会存在偏斜。即同一时刻发送的多组串行数据在不同时刻到达串行接收器。

2、针对多组串行数据之间的偏斜问题,相关技术将多组串行数据存入先入先出(first in first out,fifo),并采用对fifo内的缓存空间进行读写控制的方式消除多组串行数据之间的偏斜。这种偏斜消除方式会导致fifo的面积和功耗较大。

技术实现思路

1、本申请实施例致力于提供一种串行接收器、串行收发器、芯片以及数据对齐方法,以降低fifo的面积和功耗。

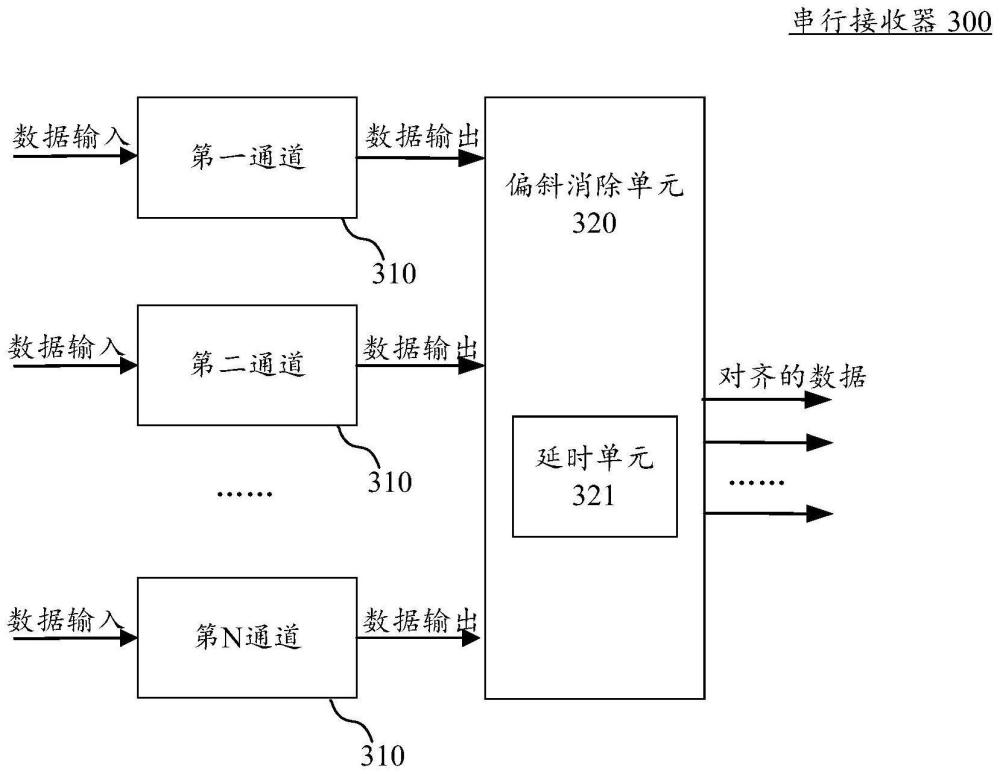

2、第一方面,本申请提供了一种串行接收器。该串行接收器包括:多个串行通道,用于并行地接收多组串行数据;偏斜消除单元,偏斜消除单元包括多个配置管理单元和主体控制单元,多个配置管理单元分别与多个串行通道相连,且多个配置管理单元均与主体控制单元相连,多个配置管理单元中的每个配置管理单元包括延时单元;其中,主体控制单元用于检测多组串行数据之间的相对延时,并根据多组串行数据之间的相对延时配置多个配置管理单元的延时参数;多个配置管理单元用于根据主体控制单元配置的延时参数,通过多个延时单元对多组串行数据进行延时处理,使得多组串行数据处于对齐状态。

3、在一些实施例中,多个配置管理单元中的每个配置管理单元包括检测单元;检测单元用于:检测每个配置管理单元对应的串行数据中的通道对齐字符;响应于检测到通道对齐字符,向主体控制单元发送触发信号,以触发主体控制单元确定多组串行数据是否处于对齐状态。

4、在一些实施例中,主体控制单元用于:响应于检测单元检测到通道对齐字符,创建对应的串行通道的时刻记录表;在每个串行通道的时刻记录表均创建成功的情况下,检测多组串行数据之间的相对延时,并根据多组串行数据之间的相对延时配置多个配置管理单元的延时参数。

5、在一些实施例中,主体控制单元还用于:响应于触发信号,从空闲状态进入工作状态,以确定多组串行数据是否处于对齐状态。

6、在一些实施例中,主体控制单元还用于:响应于触发信号,确定多组串行数据是否处于对齐状态;如果多组串行数据处于对齐状态,则从工作状态进入空闲状态。

7、第二方面,本申请提供了一种串行收发器。该串行收发器包括:串行发射器以及如第一方面的串行接收器。

8、第三方面,本申请提供了一种芯片。该芯片包括:如第一方面的串行接收器。

9、第四方面,本申请提供了一种数据对齐方法,该方法应用于串行接收器,串行接收器包括:多个串行通道以及偏斜消除单元,偏斜消除单元包括多个配置管理单元和主体控制单元,多个配置管理单元分别与多个串行通道相连,且多个配置管理单元均与主体控制单元相连,多个配置管理单元中的每个配置管理单元包括延时单元,该方法包括:控制多个串行通道并行地接收多组串行数据;控制主体控制单元检测多组串行数据之间的相对延时,并根据多组串行数据之间的相对延时配置多个配置管理单元的延时参数;控制多个配置管理单元根据主体控制单元配置的延时参数,通过多个延时单元对多组串行数据进行延时处理,使得多组串行数据处于对齐状态。

10、在一些实施例中,多个配置管理单元中的每个配置管理单元包括检测单元;该方法还包括:控制检测单元检测每个配置管理单元对应的串行数据中的通道对齐字符;响应于检测到通道对齐字符,控制检测单元向主体控制单元发送触发信号,以触发主体控制单元确定多组串行数据是否处于对齐状态。

11、在一些实施例中,该方法还包括:响应于检测单元检测到通道对齐字符,控制主体控制单元创建对应的串行通道的时刻记录表;在每个串行通道的时刻记录表均创建成功的情况下,控制主体控制单元检测多组串行数据之间的相对延时,并根据多组串行数据之间的相对延时配置多个配置管理单元的延时参数。

12、在一些实施例中,该方法还包括:响应于触发信号,控制主体控制单元从空闲状态进入工作状态,以确定多组串行数据是否处于对齐状态。

13、在一些实施例中,该方法还包括:响应于触发信号,控制主体控制单元确定多组串行数据是否处于对齐状态;如果多组串行数据处于对齐状态,则从工作状态进入空闲状态。

14、相关技术提供的偏斜消除方式需要先将多组串行数据存入fifo,再对fifo内的缓存空间进行读写控制。这种偏斜消除方式势必要求fifo的缓存空间能够容纳多组串行数据,从而导致fifo的面积和功耗较大。不同于该相关技术,本申请在接收多组串行数据的过程中,主动检测该多组串行数据之间的相对延时,一旦确定该多组串行数据的相对延时,则利用延时单元消除多组数据之间的偏斜。由此可见,本申请实施例不需要先将多组串行数据全部存储至fifo之后再开始进行处理,所以降低了对fifo的面积和功耗的要求。此外,由于不需要等待多组串行数据存入fifo之后再开始处理,也会缩短偏斜消除的时间,提高数据的传输效率。

技术特征:

1.一种串行接收器,其特征在于,包括:

2.根据权利要求1所述的串行接收器,其特征在于,所述多个配置管理单元中的每个配置管理单元包括检测单元;

3.根据权利要求2所述串行接收器,其特征在于,所述主体控制单元用于:

4.根据权利要求2所述的串行接收器,其特征在于,所述主体控制单元还用于:

5.根据权利要求2所述的串行接收器,其特征在于,所述主体控制单元还用于:

6.一种串行收发器,其特征在于,包括:

7.一种芯片,其特征在于,包括:

8.一种数据对齐方法,其特征在于,所述方法应用于串行接收器,所述串行接收器包括:多个串行通道以及偏斜消除单元,所述偏斜消除单元包括多个配置管理单元和主体控制单元,所述多个配置管理单元分别与所述多个串行通道相连,且所述多个配置管理单元均与所述主体控制单元相连,所述多个配置管理单元中的每个配置管理单元包括延时单元,所述方法包括:

9.根据权利要求8所述的方法,其特征在于,所述多个配置管理单元中的每个配置管理单元包括检测单元;所述方法还包括:

10.根据权利要求9所述的方法,其特征在于,

技术总结

本申请提供了一种串行接收器、串行收发器、芯片以及数据对齐方法。该串行接收器包括:多个串行通道,用于并行地接收多组串行数据;偏斜消除单元,偏斜消除单元包括多个配置管理单元和主体控制单元,多个配置管理单元分别与多个串行通道相连,且多个配置管理单元均与主体控制单元相连,多个配置管理单元中的每个配置管理单元包括延时单元;其中,主体控制单元用于检测多组串行数据之间的相对延时,并根据多组串行数据之间的相对延时配置多个配置管理单元的延时参数;多个配置管理单元用于根据主体控制单元配置的延时参数,通过多个延时单元对多组串行数据进行延时处理,使得多组串行数据处于对齐状态。本申请可以降低串行接收器的面积和功耗。

技术研发人员:李纪先,李晓朋,雷志明

受保护的技术使用者:飞腾信息技术有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!