一种设计集成电路的布局方法与流程

本发明属于布局设计领域,特别涉及一种设计集成电路的布局方法。

背景技术:

1、设计集成电路(ic)的布局方法在电子行业中具有重要的地位。随着科技的飞速发展,对集成电路性能、尺寸和成本的要求越来越高。为了满足这些需求,集成电路设计者需要采用更高效、更优化的布局方法。本文将介绍一种设计集成电路布局方法的技术背景。

2、集成电路布局方法的发展历程可以追溯到20世纪60年代。当时,手工布图成为主流方法,设计者通过描绘原理图来设计电路。然而,这种方法效率低下,难以应对复杂数字电路的设计。在20世纪70年代,计算机辅助设计(cad)开始应用于集成电路布局,设计者可以通过计算机软件来绘制电路图。尽管这种方法提高了设计效率,但由于计算能力的限制,它仍然无法满足大规模电路设计的需求。

3、随着计算机硬件的不断发展,集成电路布局方法也取得了显著进步。20世纪80年代,自动布局方法开始出现,设计软件可以根据设计规则自动布置元件。这种方法大大提高了设计效率,缩短了产品上市时间。然而,自动布局方法仍然受到设计规则和计算复杂度的限制,对于复杂电路的设计效果并不理想。

4、为了解决这个问题,研究人员开始研究基于人工智能(ai)的集成电路布局方法。这种方法利用机器学习和深度学习技术,可以从大量训练数据中学习有效的布局策略。基于ai的布局方法可以自动优化电路布局,以提高性能、缩小尺寸和降低成本。这种方法具有很高的灵活性,可以根据不同的设计目标和约束自动调整布局策略。

5、基于ai的集成电路布局方法已经取得了显著的成果。例如,深度学习算法可以自动优化电路的线宽、间距和过孔等参数,从而在保证性能的同时降低制造成本。此外,机器学习算法还可以根据电路的特性自动选择合适的布局算法,例如贪心算法、遗传算法等。这些研究成果为集成电路布局方法的发展提供了有力支持。

6、设计集成电路的布局方法经历了从手工布图到计算机辅助设计,再到自动布局和基于ai的布局的发展过程。随着科技的不断进步,未来集成电路布局方法还将继续演进,为电子行业带来更多的创新和突破。

7、因此,现在亟需一种设计集成电路的布局方法。

技术实现思路

1、本发明提出一种设计集成电路的布局方法,解决了现有技术中在设计集成电路布局的时候,通常没有能够进行ai辅助设计,主要依靠设计人员的经验,没有一个完整的智能设计方法的问题。

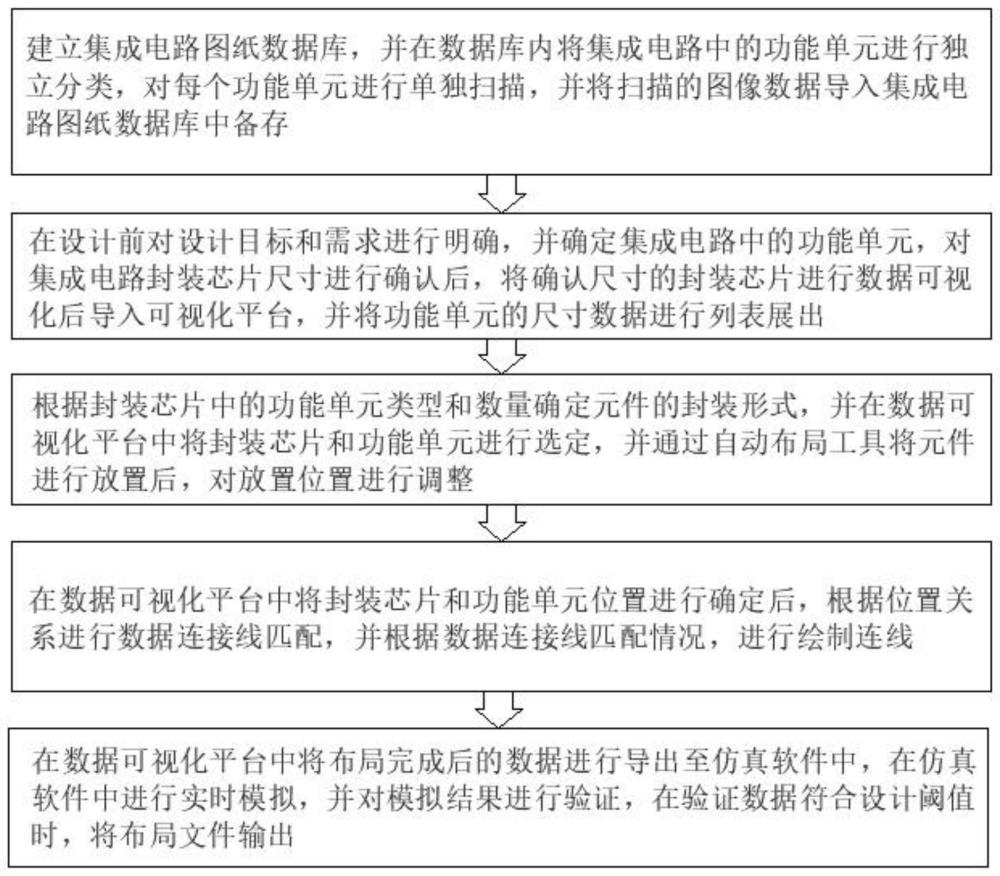

2、本发明的技术方案是这样实现的:一种设计集成电路的布局方法,所述方法包括如下步骤:建立集成电路图纸数据库,并在数据库内将集成电路中的功能单元进行独立分类,对每个功能单元进行单独扫描,并将扫描的图像数据导入集成电路图纸数据库中备存;在设计前对设计目标和需求进行明确,并确定集成电路中的功能单元,对集成电路封装芯片尺寸进行确认后,将确认尺寸的封装芯片进行数据可视化后导入可视化平台,并将功能单元的尺寸数据进行列表展出;根据封装芯片中的功能单元类型和数量确定元件的封装形式,并在数据可视化平台中将封装芯片和功能单元进行选定,并通过自动布局工具将元件进行放置后,对放置位置进行调整;在数据可视化平台中将封装芯片和功能单元位置进行确定后,根据位置关系进行数据连接线匹配,并根据数据连接线匹配情况,进行绘制连线;在数据可视化平台中将布局完成后的数据进行导出至仿真软件中,在仿真软件中进行实时模拟,并对模拟结果进行验证,在验证数据符合设计阈值时,将布局文件输出。

3、本申请文件与现有技术主要区别点在于,独立分类和单独扫描功能单元:现有技术在布局设计时通常是对整个集成电路进行扫描和分类,而该方法首先将功能单元进行独立分类,然后对每个功能单元进行单独扫描,这样可以更精确地管理和控制每个功能单元的设计,提高布局效率和精度。

4、设计目标明确和封装芯片尺寸确认:在设计前,该方法明确了设计目标和需求,并确认了集成电路中的功能单元,同时对集成电路封装芯片尺寸进行了确认。这有助于在设计过程中更准确地控制和调整,避免后期因设计目标不明确或封装尺寸不合适导致的修改和返工。

5、数据可视化和自动布局工具:该方法将确认尺寸的封装芯片进行数据可视化后导入可视化平台,并将功能单元的尺寸数据进行列表展出。通过自动布局工具,可以快速地将元件进行放置并对其位置进行调整,提高布局效率。

6、封装芯片和功能单元位置确定以及数据连接线匹配:该方法在数据可视化平台中根据位置关系进行数据连接线匹配,并根据数据连接线匹配情况,进行绘制连线。这有助于确保电路连接的正确性,避免因连接线不合适导致的电路故障。

7、仿真软件验证和布局文件输出:该方法在数据可视化平台中将布局完成后的数据导出至仿真软件中,进行实时模拟,并对模拟结果进行验证。在验证数据符合设计阈值时,将布局文件输出。这有助于在设计完成后进行及时的验证,确保设计的正确性和可行性。

8、作为一优选的实施方式,在建立集成电路图纸数据库时,从开源厂商公开数据中将图纸数据进行导入,并在导入后对图纸数据进行预处理,并根据集成电路图纸的特点和设计结构,对图纸中的功能单元进行分类。

9、作为一优选的实施方式,在进行图纸数据的预处理时,对图纸数据中的图像进行清晰化,随后将清晰后的图纸图像数据进行去噪,并将边缘空白图像进行裁剪后再进行分类。

10、作为一优选的实施方式,在进行功能单元分类时,通过功能单元的功能简述、参数规格、接口定义、物理布局和电路图示对功能单元进行分类。

11、作为一优选的实施方式,在确定封装形式时,选用dip、soic、plcc中一种进行封装,并在进行数据连接线匹配时对连线的数量、长度、宽度、过孔数量进行对应匹配。

12、作为一优选的实施方式,在将布局文件进行输出时,通过pcb设计软件将布局文件打开后,在布局软件中,选择输出gerber文件的选项,在gerber输出选项中对输出层、孔层、丝印层、焊盘层进行配置,在配置完成后点击生成或导出按钮,将布局文件转换为gerber文件格式。

13、采用了上述技术方案后,本发明的有益效果是:建立集成电路图纸数据库,对功能单元进行分类和备存,可以方便地管理和检索相关信息,提高设计效率。在设计前对设计目标和需求进行明确,有助于明确设计的方向和要求,避免后期修改和调整;确认封装芯片的尺寸后,通过数据可视化平台将封装芯片和功能单元进行可视化展示,方便设计人员对尺寸和布局进行直观的了解和调整;利用自动布局工具进行元件放置和位置调整,可以提高布局的准确性和效率,减少人工操作的错误和繁琐;根据功能单元的位置关系进行数据连接线的匹配和绘制,确保连接的准确性和稳定性;将布局完成后的数据导出至仿真软件进行实时模拟和验证,确保设计的可行性和符合设计阈值的要求。这种设计集成电路的布局方法可以提高设计效率、减少错误,确保设计的准确性和可行性。

技术特征:

1.一种设计集成电路的布局方法,其特征在于,所述方法包括如下步骤:

2.如权利要求1所述的一种设计集成电路的布局方法,其特征在于:在建立集成电路图纸数据库时,从开源厂商公开数据中将图纸数据进行导入,并在导入后对图纸数据进行预处理,并根据集成电路图纸的特点和设计结构,对图纸中的功能单元进行分类。

3.如权利要求2所述的一种设计集成电路的布局方法,其特征在于:在进行图纸数据的预处理时,对图纸数据中的图像进行清晰化,随后将清晰后的图纸图像数据进行去噪,并将边缘空白图像进行裁剪后再进行分类。

4.如权利要求1所述的一种设计集成电路的布局方法,其特征在于:在进行功能单元分类时,通过功能单元的功能简述、参数规格、接口定义、物理布局和电路图示对功能单元进行分类。

5.如权利要求1所述的一种设计集成电路的布局方法,其特征在于:在确定封装形式时,选用dip、soic、plcc中一种进行封装,并在进行数据连接线匹配时对连线的数量、长度、宽度、过孔数量进行对应匹配。

6.如权利要求1所述的一种设计集成电路的布局方法,其特征在于:在将布局文件进行输出时,通过pcb设计软件将布局文件打开后,在布局软件中,选择输出gerber文件的选项,在gerber输出选项中对输出层、孔层、丝印层、焊盘层进行配置,在配置完成后点击生成或导出按钮,将布局文件转换为gerber文件格式。

技术总结

本发明提出了一种设计集成电路的布局方法,所述方法包括如下步骤:建立集成电路图纸数据库,并在数据库内将集成电路中的功能单元进行独立分类,对每个功能单元进行单独扫描,并将扫描的图像数据导入集成电路图纸数据库中备存;在设计前对设计目标和需求进行明确,并确定集成电路中的功能单元,对集成电路封装芯片尺寸进行确认后,将确认尺寸的封装芯片进行数据可视化后导入可视化平台,并将功能单元的尺寸数据进行列表展出;根据封装芯片中的功能单元类型和数量确定元件的封装形式,并在数据可视化平台中将封装芯片和功能单元进行选定,并通过自动布局工具将元件进行放置后,对放置位置进行调整。

技术研发人员:冯瑜,张江永,王龙

受保护的技术使用者:西安智诚微电子科技有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!