一种PXIe模块化系统的FPGA升级方法与流程

本发明涉及pxie模块化系统多组fpga升级,具体为一种pxie模块化系统的fpga升级方法。

背景技术:

1、fpga作为一种常用的逻辑控制器,以其灵活性、可重复性、低成本等特点被广泛应用于通信、汽车电子、工业控制、数据中心、航空航天、测试测量等领域。

2、如需使fpga实现特定的功能任务,对fpga进行固件烧写和升级是必不可少的环节。fpga固件烧写及升级均采用jtag标准接口协议实现,对于多fpga系统而言,fpga升级技术则需要重点考虑。目前,在多fpga系统设计时,通常会采用jtag菊花链方式实现,在节省jtag物理接口的同时优化系统升级时间,jtag菊花链模式通常使用在单板多fpga系统,多板并行系统条件下的fpga升级。但对于多板主从系统或者多板并行非连续系统来讲,使用单环jtag菊花链模式则很难实现。

3、对于pxie模块化系统而言,通常存在多单板多fpga、多模块、单主多从模块、主模块不在首槽等复杂组合情况。这种情况下,如果使用单环jtag菊花链模式进行设计,将很难实现,设计难度大幅提升。如使用多环jtag菊花链模式,则需要使用多个jtag物理接口,将占用pxie模块原本就不富裕的空间,且fpga固件升级时需要分多次进行,增加固件升级复杂度和升级时间。需要针对pxie模块化系统的复杂情况设计一种新型fpga固件升级方法,同时兼容单一jtag物理接口、多环jtag菊花链的优点,实现主从模块组合、多模块级联、多fpga级联、主模块装配位置不固定等复杂情况下的pxie模块化系统fpga快速升级;因此市场急需研制一种pxie模块化系统的fpga升级方法来帮助人们解决现有的问题。

技术实现思路

1、本发明的目的在于提供一种pxie模块化系统的fpga升级方法,以解决上述背景技术中提出的对于pxie模块化系统而言,通常存在多单板多fpga、多模块、单主多从模块、主模块不在首槽等复杂组合情况。这种情况下,如果使用单环jtag菊花链模式进行设计,将很难实现,设计难度大幅提升,如使用多环jtag菊花链模式,则需要使用多个jtag物理接口,将占用pxie模块原本就不富裕的空间,且fpga固件升级时需要分多次进行,增加固件升级复杂度和升级时间的问题。

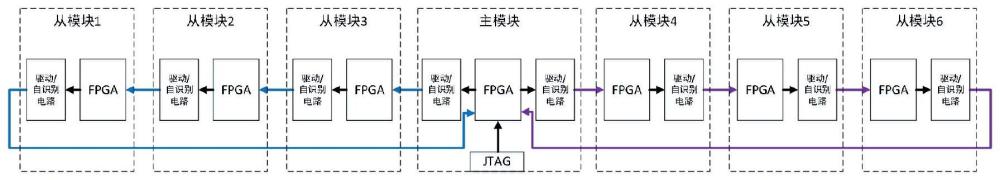

2、为实现上述目的,本发明提供如下技术方案:一种pxie模块化系统的fpga升级方法,包括硬件设计方案、逻辑设计方案和软件设计方案,所述硬件设计方案采用单一jtag标准接口、多环并联自动识别菊花链硬件设计,提供pxie模块化系统中fpga固件升级硬件链路设计方法,实现硬件电气特性连接并自动识别链路中的fpga是否在位,所述逻辑设计方案采用主fpga多路并行jtag链逻辑通道设计,通过主fpga提供多路并行jtag链通道设计,实现并行多环jtag菊花链架构,对并行jtag链进行选择,所述软件设计方案采用多路并行jtag链时序软件模拟设计,对并行jtag菊花链进行协议时序模拟,实现对并行jtag菊花链中的所有fpga进行固件升级。

3、通过上述技术方案,与当前主流的菊花链方案有明显的设计差异,包括电气硬件设计、逻辑设计和软件设计方面,既具备常规多环jtag菊花链方便快捷的优点,同时又优于多环并行jtag菊花链,同时具备节省用户接口、节约布局空间、模块在位自动识别等优点。

4、本发明在一较佳示例中可以进一步配置为:所述硬件设计方案:当主控模块在系统中首槽或末槽时,按照常规单环jtag菊花链方式设计,当主控模块在系统中间槽位时,设计成并联多环jtag菊花链,将系统中剩余从模块全部级联至菊花链中。

5、通过上述技术方案,jtag菊花链数量根据系统模块数量及结构位置关系确定,为保证jtag信号在菊花链中的信号质量,各模块输出端需要设计信号驱动电路,同时设计链路自识别电路,确保jtag菊花链不会因为某一从模块缺失而导致断链。

6、本发明在一较佳示例中可以进一步配置为:所述逻辑设计方案:pcie接口通过dma方式实现上位机与fpga的数据通信,并对fpga逻辑定义的寄存器进行读写操作,再通过片内axi crossbar与多个jtag接口模块进行互连,实现jtag接口扩展。

7、通过上述技术方案,fpga升级方法中,fpga需要实现pcie接口通信、数据解析、jtag接口扩展及数据转发等功能。

8、本发明在一较佳示例中可以进一步配置为:所述软件设计方案:通过建立对tap状态的迁移和跟踪,对jtag设备进行片内编辑的,软件先记录从当前tap状态迁移到特定tap状态所需要的tms电平变化,然后以时钟周期为单位,按比特下发至jtag控制寄存器的特定位,来达到控制tap状态的目的,达到特定的tap状态后,软件先控制fpga片内flash的区域性擦除,然后将fpga镜像文件转化而成的数据流,按照片内flash的最小写入单元从tdi管脚写入,直到完成整个数据流的写入,写入完成后,再利用.jam文件检查写入的正确性。

9、通过上述技术方案,软件模拟jtag协议的主要方法是软件在逻辑根据fpga管脚(clk,tms,tdi,tdo)定义的控制寄存器基础上建立位域模型,控制fpga管脚模拟jtag协议进行数据收发。

10、与现有技术相比,本发明的有益效果是:

11、1.该发明的一种pxie模块化系统的fpga升级方法与当前主流的菊花链方案有明显的设计差异,包括电气硬件设计、逻辑设计和软件设计方面,既具备常规多环jtag菊花链方便快捷的优点,同时又优于多环并行jtag菊花链,同时具备节省用户接口、节约布局空间、模块在位自动识别等优点。

12、2.该发明整个pxie模块化系统仅需开放单一jtag接口,即可完成系统内所有fpga升级,无需担心因模块缺失导致断链不能升级的问题,也不限制主模块装配位置,安装更灵活。

技术特征:

1.一种pxie模块化系统的fpga升级方法,包括硬件设计方案、逻辑设计方案和软件设计方案,其特征在于:所述硬件设计方案采用单一jtag标准接口、多环并联自动识别菊花链硬件设计,提供pxie模块化系统中fpga固件升级硬件链路设计方法,实现硬件电气特性连接并自动识别链路中的fpga是否在位,所述逻辑设计方案采用主fpga多路并行jtag链逻辑通道设计,通过主fpga提供多路并行jtag链通道设计,实现并行多环jtag菊花链架构,对并行jtag链进行选择,所述软件设计方案采用多路并行jtag链时序软件模拟设计,对并行jtag菊花链进行协议时序模拟,实现对并行jtag菊花链中的所有fpga进行固件升级。

2.根据权利要求1所述的一种pxie模块化系统的fpga升级方法,其特征在于:所述硬件设计方案:当主控模块在系统中首槽或末槽时,按照常规单环jtag菊花链方式设计,当主控模块在系统中间槽位时,设计成并联多环jtag菊花链,将系统中剩余从模块全部级联至菊花链中。

3.根据权利要求1所述的一种pxie模块化系统的fpga升级方法,其特征在于:所述逻辑设计方案:pcie接口通过dma方式实现上位机与fpga的数据通信,并对fpga逻辑定义的寄存器进行读写操作,再通过片内axi crossbar与多个jtag接口模块进行互连,实现jtag接口扩展。

4.根据权利要求1所述的一种pxie模块化系统的fpga升级方法,其特征在于:所述软件设计方案:通过建立对tap状态的迁移和跟踪,对jtag设备进行片内编辑的,软件先记录从当前tap状态迁移到特定tap状态所需要的tms电平变化,然后以时钟周期为单位,按比特下发至jtag控制寄存器的特定位,来达到控制tap状态的目的,达到特定的tap状态后,软件先控制fpga片内flash的区域性擦除,然后将fpga镜像文件转化而成的数据流,按照片内flash的最小写入单元从tdi管脚写入,直到完成整个数据流的写入,写入完成后,再利用.jam文件检查写入的正确性。

技术总结

本发明公开了一种PXIe模块化系统的FPGA升级方法,涉及PXIe模块化系统多组FPGA升级技术领域,为解决现有技术中对于PXIe模块化系统而言,通常存在多单板多FPGA、多模块、单主多从模块、主模块不在首槽等复杂组合情况。这种情况下,如果使用单环JTAG菊花链模式进行设计,将很难实现,设计难度大幅提升,如使用多环JTAG菊花链模式,则需要使用多个JTAG物理接口,将占用PXIe模块原本就不富裕的空间,且FPGA固件升级时需要分多次进行,增加固件升级复杂度和升级时间的问题。所述硬件设计方案采用单一JTAG标准接口、多环并联自动识别菊花链硬件设计,提供PXIe模块化系统中FPGA固件升级硬件链路设计方法,实现硬件电气特性连接并自动识别链路中的FPGA是否在位。

技术研发人员:谢强,杨鹏飞,蔡坤

受保护的技术使用者:上海正测通科技股份有限公司

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!