一种指纹阵列结构、指纹传感器芯片及电子设备的制作方法

本申请涉及指纹识别,更加具体来说,本申请涉及一种指纹阵列结构、指纹传感器芯片及电子设备。

背景技术:

1、传感器类芯片多由像素阵列以及多种电路模块等构成,其中像素阵列占比是传感类芯片的关键竞争力之一,且有定义:像素阵列占比=像素阵列面积÷芯片面积。现有技术的电容指纹传感器芯片的像素阵列占比通常在60%~75%之间,尤其是小面积电容指纹传感器芯片像素阵列占比更低。如何提高芯片的像素阵列占比,减小芯片的面积,是本领域技术人员亟待解决的技术问题。

技术实现思路

1、针对现有技术的不足,本申请实施例提供了一种指纹阵列结构、指纹传感器芯片及电子设备,能够解决至少部分上述技术问题。

2、为实现上述的技术目的,本申请实施例第一方面公开了一种指纹阵列结构,包括:

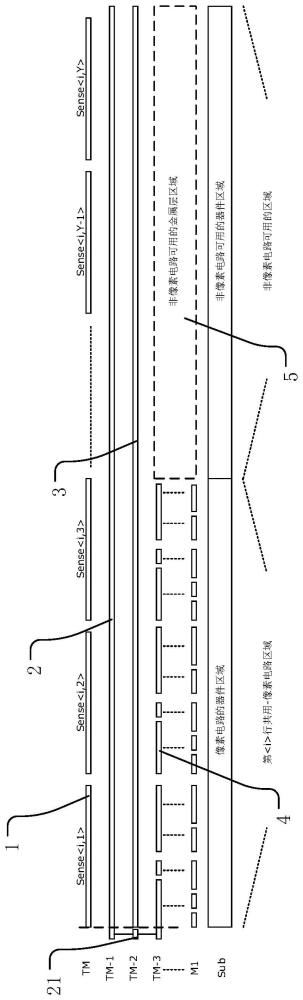

3、像素阵列,包括阵列分布的多个像素单元,多个所述像素单元分成多个像素组,每个所述像素组包括至少两个所述像素单元;

4、电路层,包括多个像素电路和多个非像素电路,所述电路层垂直朝向所述像素阵列的投影的至少一部分与所述像素阵列重叠;

5、连接线组,所述连接线组设置多个,每个所述连接线组包括多条连接线,每条所述连接线连接一个所述像素单元,每个所述像素电路通过一个所述连接线组与一个所述像素组的多个所述像素单元电气连接。

6、进一步地,位于所述像素阵列的同一行或者同一列的所述像素单元构成一个所述像素组。

7、进一步地,多个所述连接线组的接线端子位于同一端。

8、进一步地,多个所述连接线组的接线端子位于所述像素阵列所在区域的外侧。

9、进一步地,所述非像素电路与所述像素电路垂直朝向所述像素阵列的投影都位于所述像素阵列上。

10、进一步地,所述指纹阵列结构还包括屏蔽层,所述屏蔽层垂直朝向所述像素阵列的投影与所述非像素电路垂直朝向所述像素阵列的投影至少部分重叠。

11、进一步地,所述屏蔽层包括电源。

12、进一步地,所述屏蔽层包括地网络。

13、进一步地,所述屏蔽层包括电源和地网络,所述电源和地网络呈长条状相互间隔分布。

14、本申请实施例第二方面公开了一种指纹传感器芯片,包括上述指纹阵列结构。

15、进一步地,所述指纹阵列结构之外的区域设置有io电路。

16、本申请实施例第三方面公开了一种电子设备,包括上述指纹传感器芯片。

17、本申请实施例的有益效果为:

18、本申请实施例通过将电路层至少部分与像素阵列重叠设置可以减小指纹阵列结构的面积,使其应用到芯片时在像素阵列大小规格相同的情况,本申请的像素阵列占比更大、芯片面积更小。

技术特征:

1.一种指纹阵列结构,其特征在于,包括:

2.根据权利要求1所述的指纹阵列结构,其特征在于,位于所述像素阵列的同一行或者同一列的所述像素单元构成一个所述像素组。

3.根据权利要求1所述的指纹阵列结构,其特征在于,多个所述连接线组的接线端子位于同一端。

4.根据权利要求3所述的指纹阵列结构,其特征在于,多个所述连接线组的接线端子位于所述像素阵列所在区域的外侧。

5.根据权利要求1所述的指纹阵列结构,其特征在于,所述非像素电路与所述像素电路垂直朝向所述像素阵列的投影都位于所述像素阵列上。

6.根据权利要求5所述的指纹阵列结构,其特征在于,所述指纹阵列结构还包括屏蔽层,所述屏蔽层垂直朝向所述像素阵列的投影与所述非像素电路垂直朝向所述像素阵列的投影至少部分重叠。

7.根据权利要求6所述的指纹阵列结构,其特征在于,所述屏蔽层包括电源。

8.根据权利要求6所述的指纹阵列结构,其特征在于,所述屏蔽层包括地网络。

9.根据权利要求6所述的指纹阵列结构,其特征在于,所述屏蔽层包括电源和地网络,所述电源和地网络呈长条状相互间隔分布。

10.一种指纹传感器芯片,其特征在于,包括权利要求1-9任一项所述的指纹阵列结构。

11.根据权利要求10所述的指纹传感器芯片,其特征在于,所述指纹阵列结构之外的区域设置有io电路。

12.一种电子设备,其特征在于,包括权利要求10或11所述的指纹传感器芯片。

技术总结

本申请公开了指纹阵列结构、指纹传感器芯片及电子设备,涉及指纹识别技术领域。指纹阵列结构包括:像素阵列,包括阵列分布的多个像素单元,多个像素单元分成多个像素组,每个像素组包括至少两个像素单元;电路层,包括多个像素电路和多个非像素电路,电路层垂直朝向像素阵列的投影的至少一部分与像素阵列重叠;连接线组,连接线组设置多个,每个连接线组包括多条连接线,每条连接线连接一个像素单元,每个像素电路通过一个连接线组与一个像素组的多个像素单元电气连接本申请通过将非像素电路与像素阵列层叠设置可以提高像素阵列占比,使其应用到芯片时在像素阵列大小规格相同的情况,本申请的像素阵列占比更大、芯片面积更小。

技术研发人员:王程左,柳玉平

受保护的技术使用者:深圳市汇顶科技股份有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!