一种时钟树设计方法及相关装置与流程

本发明涉及集成电路,尤其涉及一种时钟树设计方法及相关装置。

背景技术:

1、3d封装是一种叠层芯片封装技术,即在同一个封装体内于垂直方向叠放两个以上晶粒(die)的封装技术,上下不同晶粒的电子信号通过晶粒上的硅穿孔来连结。3d封装比2d封装面积更小、功耗更低,拥有超大带宽。

2、然而,由于晶粒制造存在工艺偏差,同一3d封装体内的多个晶粒可能是在不同的工艺条件下制造的,因此导致不同晶粒上的有源元件的电特性可能存在较大的差异。举例而言,由于工艺偏差对cmos(complementary metal oxide semiconductor,互补金属氧化物半导体)中nmos(n沟道金属氧化物半导体)、pmos(p沟道金属氧化物半导体)的影响有所不同,可以将nmos和pmos晶体管的速度波动范围限制在由四个角所确定的矩形内。这四个角分别是:快nfet(n channel field effect transistor,n沟道场效应晶体管)和快pfet(pchannel field effect transistor,p沟道场效应晶体管)(fast n fast p,ff),慢nfet和慢pfet(slow n slow p,ss),快nfet和慢pfet(fast n slow p,fs),慢nfet和快pfet(slow n fast p,sf)。例如,具有较薄的栅氧、较低阈值电压的晶体管,就落在快角(即上述矩形的四个角中的快nfet快pfet角)附近。

3、如图1所示,在一个3d封装芯片中,晶粒die1和晶粒die2彼此垂直叠放,die1上的寄存器组reg1与die2上的寄存器组reg2之间存在信号交互。由于die1和die2可能处于ss到ff中任何一种工艺角(process corner),die1和die2之间也就可能存在多种可能的组合:ss-ff,ff-ss,sf-fs…,这就导致这两组寄存器进行交互时,延时的不确定性大大增加,往往需要加入巨大的余量margin作为时序约束条件,因此严重降低了芯片性能。而如果对芯片进行非同步时序检查,也会影响芯片性能。

4、针对3d封装中,芯片性能与时序收敛难以同时保证的问题,相关技术中尚无有效的解决方案。

技术实现思路

1、有鉴于此,本发明实施例提供一种时钟树设计方法及相关装置,能够在不影响芯片性能的条件下,使3维封装芯片的时序验证较容易收敛。

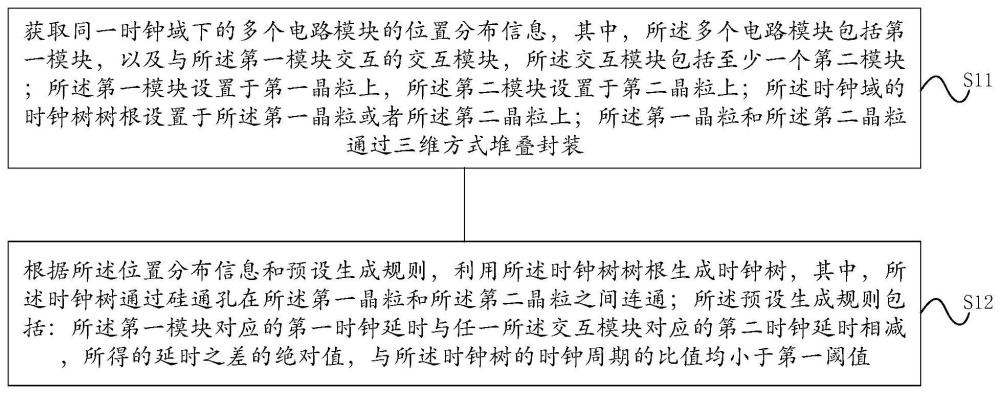

2、第一方面,本发明实施例提供一种时钟树设计方法,所述方法包括:获取同一时钟域下的多个电路模块的位置分布信息,其中,所述多个电路模块包括第一模块,以及与所述第一模块交互的交互模块,所述交互模块包括至少一个第二模块;所述第一模块设置于第一晶粒上,所述第二模块设置于第二晶粒上;所述时钟域的时钟树树根设置于所述第一晶粒或者所述第二晶粒上;所述第一晶粒和所述第二晶粒通过三维方式堆叠封装;根据所述位置分布信息和预设生成规则,利用所述时钟树树根生成时钟树,其中,所述时钟树通过硅通孔在所述第一晶粒和所述第二晶粒之间连通;所述预设生成规则包括:所述第一模块对应的第一时钟延时与任一所述交互模块对应的第二时钟延时相减,所得的延时之差的绝对值,与所述时钟树的时钟周期的比值均小于第一阈值。

3、在一种实施方式中,所述根据所述位置分布信息和预设生成规则,利用所述时钟树树根生成时钟树包括:根据所述第一模块的、及每个所述交互模块的位置分布信息,以所述时钟树树根为起点,为所述第一模块及每个所述交互模块分别生成一条时钟预备路径;确定所述时钟树树根的时钟信号在所述第一模块的时钟预备路径上的第一预备延时,以及所述时钟信号在每个所述交互模块的时钟预备路径上的第二预备延时;分别确定所述第一预备延时与每个所述第二预备延时之间的差值,得到对应的多个预备延时差;分别确定各所述预备延时差的绝对值与所述时钟周期之比所对应的第一比值是否均小于所述第一阈值;在各所述第一比值均小于所述第一阈值的情况下,将所述第一模块的时钟预备路径确定为所述第一模块的时钟路径,将各所述交互模块的时钟预备路径确定为各所述交互模块的时钟路径。

4、在一种实施方式中,所述分别确定各所述预备延时差的绝对值与所述时钟周期之比所对应的第一比值是否均小于所述第一阈值之后,所述方法还包括:在任一所述第一比值大于或等于所述第一阈值的情况下,为所述第一模块及各所述交互模块分别生成一条更新预备路径,其中,至少有一条所述更新预备路径与对应的所述时钟预备路径不同;以所述更新预备路径作为新的所述时钟预备路径,跳转到所述确定所述时钟树树根的时钟信号在所述第一模块的时钟预备路径上的第一预备延时,以及所述时钟信号在每个所述交互模块的时钟预备路径上的第二预备延时的步骤,继续执行,直至为所述第一模块及各所述交互模块分别生成对应的时钟路径为止。

5、在一种实施方式中,所述以所述时钟树树根为起点,为所述第一模块及每个所述交互模块分别生成一条时钟预备路径之后,所述确定所述时钟树树根的时钟信号在所述第一模块的时钟预备路径上的第一预备延时,以及所述时钟信号在每个所述交互模块的时钟预备路径上的第二预备延时之前,所述方法还包括:对每个所述交互模块,分别确定该交互模块的时钟预备路径与所述第一模块的时钟预备路径之间的共享路段和差异路段,其中,所述第一模块的时钟预备路径中,除所述共享路段之外的路段为第一差异路段,所述交互模块的时钟预备路径中,除所述共享路段之外的路段为第二差异路段;每个所述交互模块对应一个所述第一差异路段及所述第二差异路段。

6、在一种实施方式中,所述分别确定所述第一预备延时与每个所述第二预备延时之间的差值,得到对应的多个预备延时差包括:对于每个所述交互模块对应的所述第一差异路段以及所述第二差异路段:获取所述第一差异路段中各电路元件的元件参考延时,以及所述第二差异路段中各电路元件的元件参考延时;根据所述第一差异路段中各电路元件的元件参考延时,确定所述第一差异路段的延时参数,根据所述第二差异路段中各电路元件的元件参考延时,确定所述第二差异路段的延时参数;根据所述第一差异路段的延时参数以及所述第二差异路段的延时参数,确定所述预备延时差。

7、在一种实施方式中,所述各电路元件的元件参考延时与该电路元件的工艺角相关;所述根据所述第一差异路段的延时参数以及所述第二差异路段的延时参数,确定所述预备延时差包括:根据所述第一差异路段中各所述电路元件在慢n型晶体管慢p型晶体管工艺角条件下的延时参数,以及所述第二差异路段中的各电路元件在快n型晶体管快p型晶体管工艺角条件下的延时参数,确定所述预备延时差的第一值;根据所述第一差异路段中各所述电路元件在快n型晶体管快p型晶体管工艺角条件下的延时参数,以及所述第二差异路段中的各电路元件在慢n型晶体管慢p型晶体管工艺角条件下的延时参数,确定所述预备延时差的第二值;所述分别确定各所述预备延时差的绝对值与所述时钟周期之比所对应的第一比值是否均小于所述第一阈值包括:分别确定每个所述预备延时差对应的所述第一值的绝对值及所述第二值的绝对值,与所述时钟周期之比对应的第一比值是否均小于所述第一阈值;所述在各所述第一比值均小于所述第一阈值的情况下,将所述第一模块的时钟预备路径确定为所述第一模块的时钟路径,将各所述交互模块的时钟预备路径确定为各所述交互模块的时钟路径包括:在每个所述预备延时差对应的所述第一值的绝对值及所述第二值的绝对值,与所述时钟周期之比对应的第一比值均小于所述第一阈值的情况下,将所述第一模块的时钟预备路径确定为所述第一模块的时钟路径,将各所述交互模块的时钟预备路径确定为各所述交互模块的时钟路径。

8、在一种实施方式中,所述对每个所述交互模块,分别确定该交互模块的时钟预备路径与所述第一模块的时钟预备路径之间的共享路段和差异路段之后,所述方法还包括:确定所述第一差异路段中的电路元件的数量与所述第二差异路段中的电路元件的数量之差的绝对值是否小于第二阈值,且所述第一差异路段中的电路元件的数量与所述第二差异路段中的电路元件的数量的总和是否小于第三阈值;所述确定所述时钟树树根的时钟信号在所述第一模块的时钟预备路径上的第一预备延时,以及所述时钟信号在每个所述交互模块的时钟预备路径上的第二预备延时包括:在所述数量之差的绝对值小于所述第二阈值且所述总和小于所述第三阈值的情况下,确定所述时钟树树根的时钟信号在所述第一模块的时钟预备路径上的第一预备延时,以及所述时钟信号在每个所述交互模块的时钟预备路径上的第二预备延时。

9、在一种实施方式中,所述方法还包括:响应于所述数量之差的绝对值大于或等于所述第二阈值,或者所述总和大于或等于所述第三阈值,为所述第一模块及各所述交互模块分别生成一条更新预备路径,其中,至少有一条所述更新预备路径与对应的所述时钟预备路径不同;以所述更新预备路径作为新的所述时钟预备路径,跳转到所述确定所述时钟树树根的时钟信号在所述第一模块的时钟预备路径上的第一预备延时,以及所述时钟信号在每个所述交互模块的时钟预备路径上的第二预备延时的步骤,继续执行,直至为所述第一模块及各所述交互模块分别生成对应的时钟路径为止。

10、在一种实施方式中,所述方法还包括:如果所述总和大于或等于所述第三阈值,检测所述第一差异路段和所述第二差异路段中是否均包括时钟门控,在所述第一差异路段和所述第二差异路段中均包括时钟门控的情况下,在所述第一差异路段和所述第二差异路段中,分别删除相同数量的所述时钟门控,并重新计算所述数量之差的绝对值和所述总和。

11、在一种实施方式中,所述交互模块还包括至少一个第三模块,所述第三模块设置于所述第一晶粒上。

12、第二方面,本发明的实施例还提供一种时钟树设计装置,所述装置包括:获取单元,用于获取同一时钟域下的多个电路模块的位置分布信息,其中,所述多个电路模块包括第一模块,以及与所述第一模块交互的交互模块,所述交互模块包括至少一个第二模块;所述第一模块设置于第一晶粒上,所述第二模块设置于第二晶粒上;所述时钟域的时钟树树根设置于所述第一晶粒或者所述第二晶粒上;所述第一晶粒和所述第二晶粒通过三维方式堆叠封装;生成单元,用于根据所述位置分布信息和预设生成规则,利用所述时钟树树根生成时钟树,其中,所述时钟树通过硅通孔在所述第一晶粒和所述第二晶粒之间连通;所述预设生成规则包括:所述第一模块对应的第一时钟延时与任一所述交互模块对应的第二时钟延时相减,所得的延时之差的绝对值,与所述时钟树的时钟周期的比值均小于第一阈值。

13、在一种实施方式中,所述生成单元包括:第一生成模块,用于根据所述第一模块的、及每个所述交互模块的位置分布信息,以所述时钟树树根为起点,为所述第一模块及每个所述交互模块分别生成一条时钟预备路径;第一确定模块,用于确定所述时钟树树根的时钟信号在所述第一模块的时钟预备路径上的第一预备延时,以及所述时钟信号在每个所述交互模块的时钟预备路径上的第二预备延时;第二确定模块,用于分别确定所述第一预备延时与每个所述第二预备延时之间的差值,得到对应的多个预备延时差;第三确定模块,用于分别确定各所述预备延时差的绝对值与所述时钟周期之比所对应的第一比值是否均小于所述第一阈值;第四确定模块,用于在各所述第一比值均小于所述第一阈值的情况下,将所述第一模块的时钟预备路径确定为所述第一模块的时钟路径,将各所述交互模块的时钟预备路径确定为各所述交互模块的时钟路径。

14、在一种实施方式中,所述生成单元还包括:第二生成模块,用于在分别确定各所述预备延时差的绝对值与所述时钟周期之比所对应的第一比值是否均小于所述第一阈值之后,在任一所述第一比值大于或等于所述第一阈值的情况下,为所述第一模块及各所述交互模块分别生成一条更新预备路径,其中,至少有一条所述更新预备路径与对应的所述时钟预备路径不同;第一跳转模块,用于以所述更新预备路径作为新的所述时钟预备路径,跳转到所述确定所述时钟树树根的时钟信号在所述第一模块的时钟预备路径上的第一预备延时,以及所述时钟信号在每个所述交互模块的时钟预备路径上的第二预备延时的步骤,继续执行,直至为所述第一模块及各所述交互模块分别生成对应的时钟路径为止。

15、在一种实施方式中,所述生成单元,还包括:第五确定模块,用于在以所述时钟树树根为起点,为所述第一模块及每个所述交互模块分别生成一条时钟预备路径之后,在确定所述时钟树树根的时钟信号在所述第一模块的时钟预备路径上的第一预备延时,以及所述时钟信号在每个所述交互模块的时钟预备路径上的第二预备延时之前,对每个所述交互模块,分别确定该交互模块的时钟预备路径与所述第一模块的时钟预备路径之间的共享路段和差异路段,其中,所述第一模块的时钟预备路径中,除所述共享路段之外的路段为第一差异路段,所述交互模块的时钟预备路径中,除所述共享路段之外的路段为第二差异路段;每个所述交互模块对应一个所述第一差异路段及所述第二差异路段。

16、在一种实施方式中,所述第二确定模块包括:获取子模块,用于对于每个所述交互模块对应的所述第一差异路段以及所述第二差异路段,获取所述第一差异路段中各电路元件的元件参考延时,以及所述第二差异路段中各电路元件的元件参考延时;第一确定子模块,用于根据所述第一差异路段中各电路元件的元件参考延时,确定所述第一差异路段的延时参数,根据所述第二差异路段中各电路元件的元件参考延时,确定所述第二差异路段的延时参数;第二确定子模块,用于根据所述第一差异路段的延时参数以及所述第二差异路段的延时参数,确定所述预备延时差。

17、在一种实施方式中,所述各电路元件的元件参考延时与该电路元件的工艺角相关;所述第二确定子模块,具体用于:根据所述第一差异路段中各所述电路元件在慢n型晶体管慢p型晶体管工艺角条件下的延时参数,以及所述第二差异路段中的各电路元件在快n型晶体管快p型晶体管工艺角条件下的延时参数,确定所述预备延时差的第一值;根据所述第一差异路段中各所述电路元件在快n型晶体管快p型晶体管工艺角条件下的延时参数,以及所述第二差异路段中的各电路元件在慢n型晶体管慢p型晶体管工艺角条件下的延时参数,确定所述预备延时差的第二值;所述第三确定模块,具体用于分别确定每个所述预备延时差对应的所述第一值的绝对值及所述第二值的绝对值,与所述时钟周期之比对应的第一比值是否均小于所述第一阈值;所述第四确定模块,具体用于在每个所述预备延时差对应的所述第一值的绝对值及所述第二值的绝对值,与所述时钟周期之比对应的第一比值均小于所述第一阈值的情况下,将所述第一模块的时钟预备路径确定为所述第一模块的时钟路径,将各所述交互模块的时钟预备路径确定为各所述交互模块的时钟路径。

18、在一种实施方式中,所述生成单元,还包括:第六确定模块,用于在对每个所述交互模块,分别确定该交互模块的时钟预备路径与所述第一模块的时钟预备路径之间的共享路段和差异路段之后,确定所述第一差异路段中的电路元件的数量与所述第二差异路段中的电路元件的数量之差的绝对值是否小于第二阈值,且所述第一差异路段中的电路元件的数量与所述第二差异路段中的电路元件的数量的总和是否小于第三阈值;所述第一确定模块,具体用于在所述数量之差的绝对值小于所述第二阈值且所述总和小于所述第三阈值的情况下,确定所述时钟树树根的时钟信号在所述第一模块的时钟预备路径上的第一预备延时,以及所述时钟信号在每个所述交互模块的时钟预备路径上的第二预备延时。

19、在一种实施方式中,所述生成单元还包括:第三生成模块,用于响应于所述数量之差的绝对值大于或等于所述第二阈值,或者所述总和大于或等于所述第三阈值,为所述第一模块及各所述交互模块分别生成一条更新预备路径,其中,至少有一条所述更新预备路径与对应的所述时钟预备路径不同;第二跳转模块,用于以所述更新预备路径作为新的所述时钟预备路径,跳转到所述确定所述时钟树树根的时钟信号在所述第一模块的时钟预备路径上的第一预备延时,以及所述时钟信号在每个所述交互模块的时钟预备路径上的第二预备延时的步骤,继续执行,直至为所述第一模块及各所述交互模块分别生成对应的时钟路径为止。

20、在一种实施方式中,所述生成单元还包括:检测模块,用于如果所述总和大于或等于所述第三阈值,检测所述第一差异路段和所述第二差异路段中是否均包括时钟门控;删除模块,用于在所述第一差异路段和所述第二差异路段中均包括时钟门控的情况下,在所述第一差异路段和所述第二差异路段中,分别删除相同数量的所述时钟门控,并重新计算所述数量之差的绝对值和所述总和。

21、在一种实施方式中,所述交互模块还包括至少一个第三模块,所述第三模块设置于所述第一晶粒上。

22、第三方面,本发明的实施例还提供一种处理器,包括:第一晶粒、第二晶粒;所述第一晶粒和所述第二晶粒通过三维方式堆叠封装;所述第一晶粒和所述第二晶粒上,分别包括有至少一个电路模块;所述至少一个电路模块包括:第一模块,以及,与所述第一模块交互的交互模块;所述交互模块包括至少一个第二模块;其中,所述第一模块设置于所述第一晶粒上,所述第二模块设置于所述第二晶粒上;所述第一模块与各所述交互模块由同一时钟树提供时钟信号,其中,所述时钟树的时钟树树根设置于所述第一晶粒上或者所述第二晶粒上;所述时钟树通过硅通孔在所述第一晶粒和所述第二晶粒之间连通;所述第一模块的时钟信号以及任一所述第二模块的时钟信号,从位于第二晶粒上的时钟网的同一位置引出后,分别通过无源时钟通路传入所述第一模块的时钟输入端以及所述第二模块的时钟输入端,其中,所述无源时钟通路包括金属线或硅通孔。

23、在一种实施方式中,所述时钟树树根设置于所述第二晶粒上;所述第一模块对应的无源时钟通路中包括硅通孔,所述第一模块与所述第二模块之间的每条数据通路中均包括硅通孔;每条所述数据通路中的硅通孔的数量与所述第一模块对应的无源时钟通路中的硅通孔的数量相等。

24、在一种实施方式中,所述时钟树树根设置于所述第二晶粒上,所述第一模块对应的无源时钟通路中包括硅通孔;所述交互模块还包括第三模块,所述第三模块设置于所述第一晶粒上;所述第三模块的时钟信号,从所述第一晶粒上的时钟网引出后,传入所述第三模块的时钟输入端;其中,所述第一晶粒上的时钟网由位于所述第一晶粒上的第一时钟驱动组件驱动,所述第一时钟驱动组件通过硅通孔与位于所述第二晶粒上的第二时钟驱动组件电连接。

25、在一种实施方式中,所述第二时钟驱动组件包括至少两级串联的第二反相器,所述第一时钟驱动组件在所述第二时钟驱动组件中的接入点,位于所述第二时钟驱动组件的预设两级第二反相器之间,以使所述接入点到所述第二晶粒的时钟网之间的第二反相器的级数,与所述第二时钟驱动组件中的第二反相器的总级数的比值,处于预设范围内。

26、在一种实施方式中,所述预设范围大于1/4且小于1/2。

27、在一种实施方式中,所述第一时钟驱动组件包括至少两级串联的第一反相器,所述第一反相器的级数等于所述接入点到所述第二晶粒的时钟网之间的第二反相器的级数。

28、第四方面,本发明的实施例还提供一种电子设备,所述电子设备包括:壳体、处理器、存储器、电路板和电源电路,其中,电路板安置在壳体围成的空间内部,处理器和存储器设置在电路板上;电源电路,用于为上述电子设备的各个电路或器件供电;存储器用于存储可执行程序代码;处理器通过读取存储器中存储的可执行程序代码来运行与可执行程序代码对应的程序,用于执行本发明的任一实施例提供的时钟树设计方法。

29、第五方面,本发明的实施例还提供一种计算机可读存储介质,所述计算机可读存储介质存储有一个或者多个程序,所述一个或者多个程序可被一个或者多个处理器执行,以实现本发明的任一实施例提供的时钟树设计方法。

- 还没有人留言评论。精彩留言会获得点赞!