双核锁步电路及芯片设备的制作方法

本发明涉及芯片,尤其涉及一种双核锁步电路及芯片设备。

背景技术:

1、双核锁步在高安全性芯片的设计中很广泛,比如汽车asil(automotive safetyintegrity level,汽车安全完整性等级) d芯片中为了满足随机硬件失效检测,从而最大程度上避免违反功能安全目标的要求,会使用两个功能一致的模块,运行一样的工作,将结果进行比较,假如出错,则认为至少其中一个模块运行出错,模块输出结果不可信,芯片将进行下一步的处理,如进入安全状态。

2、相关技术中,双核锁步电路存在如下问题:

3、第一,只能保护到主逻辑单元与比较逻辑单元,共享的存储器不能被保护到,所以使用ecc(error checking code,错误校验码)保护共享的存储器,需要占据存储器的一部分存储空间;

4、第二,由于存储器(如cache(高速缓冲存储器)、sram(static random accessmemory,静态存储器))是主逻辑单元与比较逻辑单元共享的,所以时序收敛上会更紧张,特别是当功能安全要求主逻辑单元与比较逻辑单元最好要做物理隔离,有要求的最小距离,这对于高速安全芯片来说是很大的挑战。

技术实现思路

1、本发明旨在至少在一定程度上解决相关技术中的技术问题之一。为此,本发明的第一个目的在于提出一种双核锁步电路,使得存储单元可以放置在距离对应的逻辑单元更近的地方,时序收敛上会更轻松。

2、本发明的第二个目的在于提出一种芯片设备。

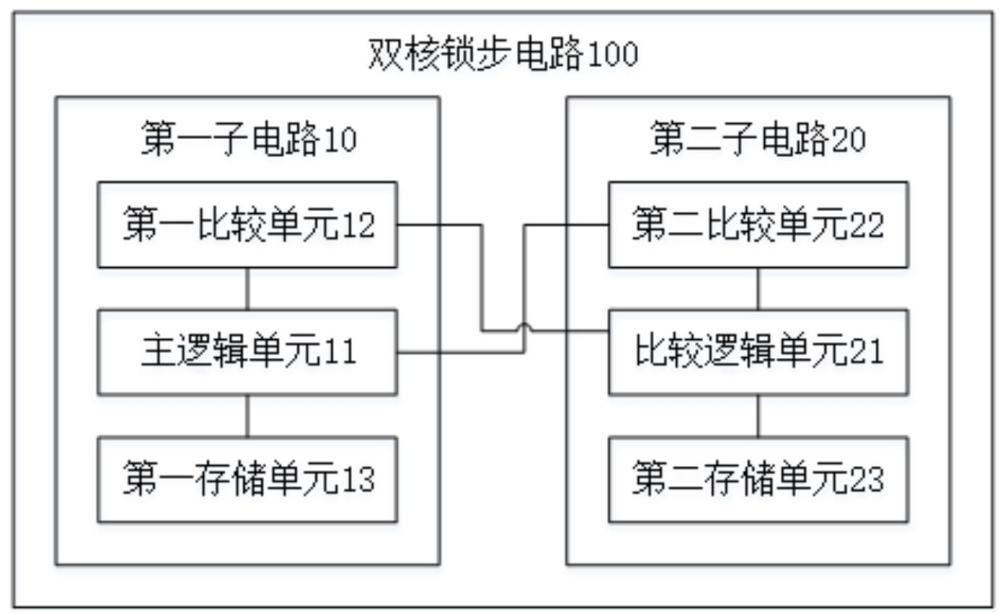

3、为达到上述目的,本发明第一方面实施例提出了一种双核锁步电路,包括:第一子电路,包括主逻辑单元、第一比较单元和第一存储单元,所述主逻辑单元与所述第一比较单元、所述第一存储单元分别连接,用于输出数据分别至所述第一比较单元、所述第一存储单元,并从所述第一存储单元读取数据;第二子电路,包括比较逻辑单元、第二比较单元和第二存储单元,所述比较逻辑单元与所述第二比较单元、所述第二存储单元分别连接,用于输出数据分别至所述第二比较单元、所述第二存储单元,并从所述第二存储单元读取数据;其中,所述第一比较单元与所述第二比较单元并联连接,两者的作用相同,用于将所述主逻辑单元的输出数据与所述比较逻辑单元的输出数据进行比较。

4、根据本发明实施例的双核锁步电路,通过主逻辑单元与比较逻辑单元分别具有各自的存储单元(即第一存储单元和第二存储单元),使得存储单元可以放置在距离对应的逻辑单元更近的地方,时序收敛上会更轻松。

5、为达到上述目的,本发明第二方面实施例提出了一种芯片设备,包括所述双核锁步电路。

6、根据本发明实施例的芯片设备,通过上述的双核锁步电路,使得存储单元可以放置在距离对应的逻辑单元更近的地方,时序收敛上会更轻松。

7、本发明附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

技术特征:

1.一种双核锁步电路,其特征在于,包括:

2.根据权利要求1所述的双核锁步电路,其特征在于,所述电路还包括:

3.根据权利要求2所述的双核锁步电路,其特征在于,所述第一比较单元与所述第二比较单元的结构相同,包括第一比较器、第二比较器、第一延时器和第二延时器;其中,

4.根据权利要求3所述的双核锁步电路,其特征在于,所述电路还包括第一选择子电路,所述第一选择子电路包括:

5.根据权利要求4所述的双核锁步电路,其特征在于,所述电路还包括第二延时子电路和第二选择子电路,所述第二延时子电路的输入端与所述交叉开关、所述第一存储单元分别连接,所述第二选择子电路包括:

6.根据权利要求2所述的双核锁步电路,其特征在于,所述第一延时子电路包括第三延时器,所述第三延时器的输入端与所述交叉开关连接,所述第三延时器的输出端与所述比较逻辑单元连接。

7.根据权利要求5所述的双核锁步电路,其特征在于,所述第二延时子电路包括第四延时器,所述第四延时器的输入端与所述交叉开关、所述第一存储单元分别连接,所述第四延时器的输出端与所述第二多路选择开关的第二输入端连接。

8.根据权利要求1所述的双核锁步电路,其特征在于,所述第一存储单元和所述第二存储单元包括存储阵列,所述存储阵列中设有ecc校验码。

9.根据权利要求2所述的双核锁步电路,其特征在于,对应所述交叉开关设有端到端保护机制。

10.一种芯片设备,其特征在于,包括根据权利要求1-9中任一项所述的双核锁步电路。

技术总结

本发明公开了一种双核锁步电路及芯片设备,电路包括:第一子电路,包括主逻辑单元、第一比较单元和第一存储单元,主逻辑单元,用于输出数据分别至第一比较单元、第一存储单元,并从第一存储单元读取数据;第二子电路,包括比较逻辑单元、第二比较单元和第二存储单元,比较逻辑单元,用于输出数据分别至第二比较单元、第二存储单元,并从第二存储单元读取数据;其中,第一比较单元与第二比较单元并联连接,两者的作用相同,用于将主逻辑单元的输出数据与比较逻辑单元的输出数据进行比较。使得存储单元可以放置在距离对应的逻辑单元更近的地方,时序收敛上会更轻松。

技术研发人员:王霆,徐沛文,孙振玮,石刚

受保护的技术使用者:苏州萨沙迈半导体有限公司

技术研发日:

技术公布日:2024/1/22

- 还没有人留言评论。精彩留言会获得点赞!