用于PCIe信号测试的方法、装置、设备及介质与流程

本申请涉及pcie接口测试,例如涉及一种用于pcie信号测试的方法、装置、设备及介质。

背景技术:

1、pci-express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准,简称pcie。2019年5月29日发布了pcie5.0标准的最终版本,pcie5.0速度是pcie4.0的两倍。但pcie 5.0的设备会有信号完整性问题,因此,对pcie 5.0的信号完整性测试必不可少。

2、目前,测试需要按pcie5.0测试治具的码型切换按钮。其中,切换pcie1.0一次、pcie2.0两次、pcie3.0十次、pcie4.0二十次,然后才到pcie5.0p0码型,要到p9码型,还要再切九次。同时,在测试pcie5.0时,示波器需要手动配置采样率、存储深度、传递函数等一系列参数,配置过程复杂,需要较长时间。

3、在实现本公开实施例的过程中,发现相关技术中至少存在如下问题:

4、pcie5.0信号测试的过程较为繁琐,全部设置下来需要很长的时间,测试的效率较低。

5、需要说明的是,在上述背景技术部分公开的信息仅用于加强对本申请的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现思路

1、为了对披露的实施例的一些方面有基本的理解,下面给出了简单的概括。所述概括不是泛泛评述,也不是要确定关键/重要组成元素或描绘这些实施例的保护范围,而是作为后面的详细说明的序言。

2、本公开实施例提供了一种用于pcie信号测试的方法、装置、设备及介质,以解决pcie信号测试效率较低的技术问题。

3、在一些实施例中,所述用于pcie信号测试的方法包括:

4、响应于接收到开始测试指令,按照预设规则,多次执行以下子测试操作:向pcie测试治具发送当前子测试的码型切换指令;调整当前子测试对应的配置信息,所述配置信息包括采样率、存储深度、传递函数损耗、纵坐标、横坐标;采集并保存当前子测试的波形数据;

5、分析至少一个所述子测试的波形数据,得到pcie信号测试结果。

6、作为一种可能的实施方式,所述波形数据包括tx接口采集的tx数据和clk接口采集的clk数据。

7、作为一种可能的实施方式,所述分析至少一个所述子测试的波形数据,得到pcie信号测试结果,包括:

8、利用预设软件,分析至少一个所述子测试的波形数据,得到pcie信号测试结果,所述预设软件包括sigtest软件和clockjittertool软件。

9、作为一种可能的实施方式,所述子测试包括pcie1.0子测试、pcie2.0子测试、pcie3.0子测试、pcie4.0子测试和/或pcie5.0子测试。

10、在一些实施例中,所述用于pcie信号测试的方法包括:

11、响应于接收到码型切换指令,调整到所述码型切换指令对应的preset码型。

12、在一些实施例中,所述用于pcie信号测试的装置包括:

13、测试模块,用于响应于接收到开始测试指令,按照预设规则,多次执行以下子测试操作:向pcie测试治具发送当前子测试的码型切换指令;调整当前子测试对应的配置信息,所述配置信息包括采样率、存储深度、传递函数损耗、纵坐标、横坐标;采集并保存当前子测试的波形数据;

14、分析模块,用于分析至少一个所述子测试的波形数据,得到pcie信号测试结果。

15、在一些实施例中,所述用于pcie信号测试的装置包括:

16、码型切换模块,用于响应于接收到码型切换指令,调整到所述码型切换指令对应的preset码型。

17、在一些实施例中,所述用于pcie信号测试的系统包括:

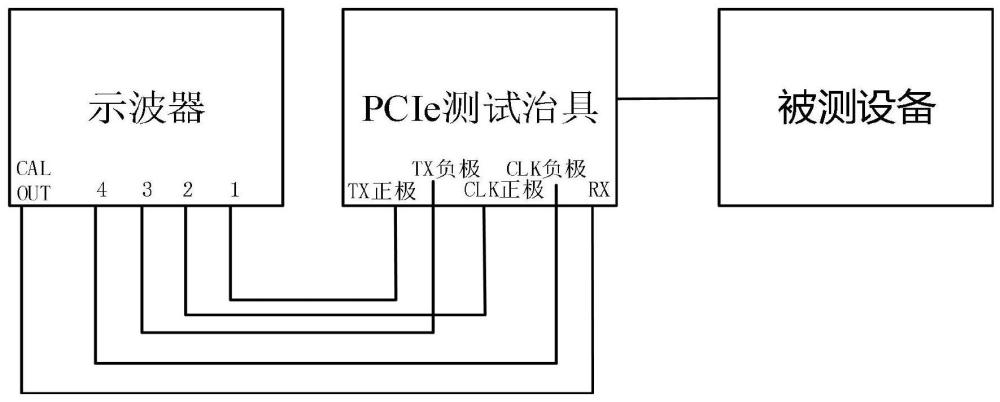

18、示波器、pcie测试治具和被测设备;

19、所述示波器的1、3通道接口分别与所述pcie测试治具tx接口的正极和负极连接,所述示波器的2、4通道接口分别与所述pcie测试治具的clk接口的正极和负极连接,所述示波器的cal out接口与所述pcie测试治具的任一rx接口连接,所述pcie测试治具和所述被测设备连接。

20、在一些实施例中,所述用于pcie信号测试的设备,包括处理器和存储有程序指令的存储器,其特征在于,所述处理器被配置为在运行所述程序指令时,执行如上述方法实施例所述的用于pcie信号测试的方法。

21、在一些实施例中,所述用于pcie信号测试的存储介质,存储有程序指令,其特征在于,所述程序指令在运行时,执行如上述方法实施例所述的用于pcie信号测试的方法。

22、本公开实施例提供的用于pcie信号测试方法、装置、设备及介质,可以实现以下技术效果:照预设规则可以自动让测试治具执行码型切换,同时示波器调整配置,自动采集波形并分析,不需要人工复杂操作,大幅提升了测试效率。

23、以上的总体描述和下文中的描述仅是示例性和解释性的,不用于限制本申请。

技术特征:

1.一种用于pcie信号测试的方法,其特征在于,应用于示波器,包括:

2.根据权利要求1所述的方法,其特征在于,所述波形数据包括tx接口采集的tx数据和clk接口采集的clk数据。

3.根据权利要求1所述的方法,其特征在于,所述分析至少一个所述子测试的波形数据,得到pcie信号测试结果,包括:

4.根据权利要求1所述的方法,其特征在于,所述子测试包括pcie1.0子测试、pcie2.0子测试、pcie3.0子测试、pcie4.0子测试和/或pcie5.0子测试。

5.一种用于pcie信号测试的方法,其特征在于,应用于pcie测试治具,包括:

6.一种用于pcie信号测试的装置,其特征在于,应用于示波器,包括:

7.一种用于pcie信号测试的装置,其特征在于,应用于pcie测试治具,包括:

8.一种用于pcie信号测试的系统,其特征在于,包括:示波器、pcie测试治具和被测设备;

9.一种用于pcie信号测试的设备,包括处理器和存储有程序指令的存储器,其特征在于,所述处理器被配置为在运行所述程序指令时,执行如权利要求1至4或如权利要求5任一项所述的用于pcie信号测试的方法。

10.一种存储介质,存储有程序指令,其特征在于,所述程序指令在运行时,执行如权利要求1至4或如权利要求5任一项所述的用于pcie信号测试的方法。

技术总结

本申请涉及PCIe接口测试技术领域,公开一种用于PCIe信号测试方法,包括:响应于接收到开始测试指令,按照预设规则,多次执行以下子测试操作:向PCIe测试治具发送当前子测试的码型切换指令;调整当前子测试对应的配置信息,所述配置信息包括采样率、存储深度、传递函数损耗、纵坐标、横坐标;采集并保存当前子测试的波形数据;分析至少一个所述子测试的波形数据,得到PCIe信号测试结果。这样,不需要手动按压测试治具的按钮、手动配置参数以及手动调用分析,自动化执行PCIe信号测试流程,提升测试效率。本申请还公开一种用于PCIe信号测试装置、系统、设备及介质。

技术研发人员:周生瑞,李华,王婷

受保护的技术使用者:西安超越申泰信息科技有限公司

技术研发日:

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!