一种基于AXI4-STREAM接口的图像缩放模块及图像缩放方法与流程

本发明涉及图像处理,具体涉及一种基于axi4-stream接口的图像缩放模块及图像缩放方法。

背景技术:

1、图像缩放技术是利用插值算法,将输入图像以一定比例放大或缩小的技术。该技术广泛应用于图像预处理、图像显示拼接等方面。集成了双核armcortex-a9处理器与基于28nm工艺的xilinx-7系列fpga的soc是一种全可编程片上芯片,该芯片集合了arm丰富的系统资源和fpga的灵活性、实时性、可扩展性等优点。通常,在fpga内部开发图像处理算法的优势在于其流水线处理方式,该处理方式具有可忽略不计的处理延时。传统基于行场同步信号的图像传输方式在进行图像缩放时对行场同步信号的消隐期具有较强的需求,对于图像放大而言,当行消隐期较短时,则无法实现较大倍数的图像放大。而对于行消隐期较短的图像而言,其帧频一定的情况下,场消隐期往往较大,因此场消隐期内的时间往往被浪费掉。

技术实现思路

1、本发明针对现有技术中存在的技术问题,提供一种基于axi4-stream接口的图像缩放模块及图像缩放方法,该方法基于axi4-stream接口协议实现,利用ddr真缓存以及各模块之间axi4-stream的握手逻辑,充分利用图像场消隐期的时间,从而突破行场同步信号对图像放大倍数的限制。

2、本发明解决上述技术问题的技术方案如下:

3、一方面,本发明提供一种基于axi4-stream接口的图像缩放模块,包括输入接口、第一存储单元、缩放处理单元、输出接口;

4、所述输入接口采用axi4-stream接口实现与前端ip的连接,所述输出接口通过axi4-stream接口与后端ip连接;

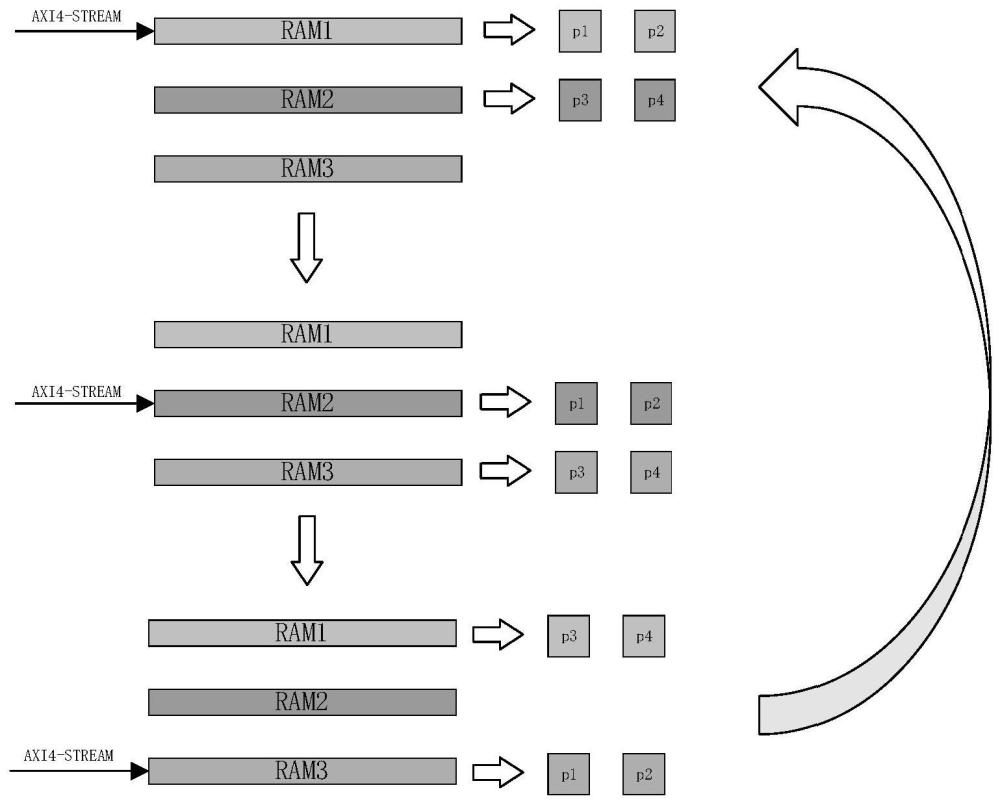

5、所述第一存储单元包含至少三个缓存空间,记为第一缓存、第二缓存和第三缓存;所述第一缓存、第二缓存和第三缓存采用循环存储的方式依次对前端ip输出的图像数据进行缓存;

6、当前缓存的数据接收完毕后,缩放处理单元利用双线性插值算法对当前缓存与上一缓存中的图像数据进行图像缩放处理;在下一缓存的数据接收完毕后,缩放处理单元复用当前缓存中的图像数据,并与下一缓存中的数据共同进行图像缩放处理。

7、进一步的,所述输出接口包括fifo单元,所述fifo单元用于缓存缩放处理单元的处理结果,并在满足axi4-stream接口的握手逻辑的情况下,将处理结果发送给后端ip。

8、进一步的,所述输入接口与前端ip之间还连接有第二存储单元,所述第二存储单元包括第四缓存和第五缓存,所述第四缓存和第五缓存采用乒乓操作方式依次接收前端ip输出的图像数据,并按序将所述图像数据转发至所述输入接口。

9、另一方面,本发明还提供一种图像缩放方法,该方法基于上述的图像缩放模块实现,包括:

10、拉高所述输入接口的tready信号端电平;

11、所述第一缓存、第二缓存和第三缓存采用循环存储的方式依次对前端ip输出的图像数据进行缓存;

12、当前缓存的数据接收完毕后,缩放处理单元利用双线性插值算法对当前缓存与上一缓存中的图像数据进行图像缩放处理;在下一缓存的数据接收完毕后,缩放处理单元复用当前缓存中的图像数据,并与下一缓存中的数据共同进行图像缩放处理。

13、进一步的,若缩放处理单元利用双线性插值算法对当前缓存与上一缓存中的图像数据进行图像缩放处理未结束,且下一缓存的数据已接收完毕,则拉低所述输入接口的tready信号端电平。

14、本发明的有益效果是:使用axi4-stream接口的图像处理算法,能够实现任意比例的图像放大,并且有利于实现图像处理ip的接口统型。

技术特征:

1.一种基于axi4-stream接口的图像缩放模块,其特征在于,包括输入接口、第一存储单元、缩放处理单元、输出接口;

2.根据权利要求1所述的图像缩放模块,其特征在于,所述输出接口包括fifo单元,所述fifo单元用于缓存缩放处理单元的处理结果,并在满足axi4-stream接口的握手逻辑的情况下,将处理结果发送给后端ip。

3.根据权利要求1所述的图像缩放模块,其特征在于,所述输入接口与前端ip之间还连接有第二存储单元,所述第二存储单元包括第四缓存和第五缓存,所述第四缓存和第五缓存采用乒乓操作方式依次接收前端ip输出的图像数据,并按序将所述图像数据转发至所述输入接口。

4.一种图像缩放方法,该方法基于权利要求1所述的图像缩放模块实现,其特征在于,包括:

5.根据权利要求4所述的图像缩放方法,其特征在于,若缩放处理单元利用双线性插值算法对当前缓存与上一缓存中的图像数据进行图像缩放处理未结束,且下一缓存的数据已接收完毕,则拉低所述输入接口的tready信号端电平。

技术总结

本发明涉及一种基于AXI4‑STREAM接口的图像缩放模块及图像缩放方法,该模块包括输入接口、第一存储单元、缩放处理单元、输出接口;所述输入接口采用AXI4‑STREAM接口实现与前端IP的连接,所述输出接口通过AXI4‑STREAM接口与后端IP连接;所述第一存储单元包含至少三个缓存空间,记为第一缓存、第二缓存和第三缓存;所述第一缓存、第二缓存和第三缓存采用循环存储的方式依次对前端IP输出的图像数据进行缓存;当前缓存的数据接收完毕后,缩放处理单元利用双线性插值算法对当前缓存与上一缓存中的图像数据进行图像缩放处理;在下一缓存的数据接收完毕后,缩放处理单元复用当前缓存中的图像数据,并与下一缓存中的数据共同进行图像缩放处理。

技术研发人员:江同源,蒋沅嵩,朱师伦,夏平

受保护的技术使用者:华中光电技术研究所(中国船舶集团有限公司第七一七研究所)

技术研发日:

技术公布日:2024/4/24

- 还没有人留言评论。精彩留言会获得点赞!