读写控制电路及读写控制方法与流程

本公开涉及集成电路,特别是涉及一种读写控制电路及读写控制方法。

背景技术:

1、在集成电路设计中,先入先出(first in first out,简称fifo)读写电路作为常用的数据缓冲器会被大量使用。fifo读写电路中的存储单元通常采用静态随机存储器或者寄存器堆来实现,当存储数据深度较少时通常会选择寄存器堆作为fifo读写电路的存储单元。

2、目前,基于寄存器堆的fifo读写电路可以通过在空闲时关闭读写时钟门控使能来降低功耗。然而,对于读写频率较高且空闲时间较少的fifo读写电路,仅仅通过在空闲时关闭读写时钟门控使能很难实现低功耗。

技术实现思路

1、基于此,本公开提供了一种读写控制电路及读写控制方法,用于降低读写电路的功耗。

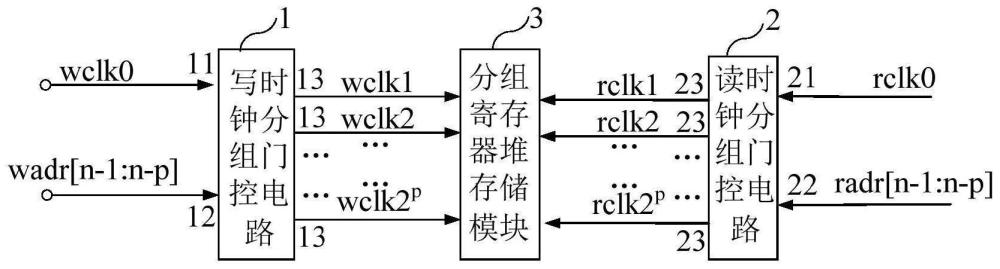

2、本公开一些实施例提供了一种读写控制电路,包括:写时钟分组门控电路、读时钟分组门控电路以及分组寄存器堆存储模块。写时钟分组门控电路被配置为基于第一写时钟输出信号及第一写地址信号生成多个第二写时钟输出信号。读时钟分组门控电路被配置为基于第一读时钟输出信号及第一读地址信号生成多个第二读时钟输出信号。分组寄存器堆存储模块与写时钟分组门控电路的输出端及读时钟分组门控电路的输出端均相连接。

3、本公开实施例中,利用写时钟分组门控电路对第一写地址信号进行分组门控,生成多个第二写时钟输出信号。同时利用读时钟分组门控电路对第一读地址信号进行分组门控,生成多个第二读时钟输出信号。然后利用分组寄存器堆存储模块接收多个第二写时钟输出信号和多个第二读时钟输出信号。如此,通过对第一写地址信号和第一读地址信号进行分组门控可以降低整个读写控制电路的功耗。

4、此外,本公开实施例配合在空闲时关闭读写时钟门控使能,可以进一步降低整个读写控制电路的功耗。

5、在本公开一些实施例中,写时钟分组门控电路包括:第一写时钟输入端、第一写地址输入端以及多个第一写时钟输出端。第一写时钟输入端被配置为接收第一写时钟输出信号。第一写地址输入端被配置为接收第一写地址信号。多个第一写时钟输出端被配置为分别输出多个第二写时钟输出信号。

6、在本公开一些实施例中,写时钟分组门控电路包括:多个写地址比较器以及多个写时钟门控器。各写地址比较器均包括第一比较输入端、第二比较输入端及输出端;多个写地址比较器的第一比较输入端均相连接,共同作为写时钟分组门控制电路的第一写地址输入端;各写地址比较器的第二比较输入端分别接收不同的常量信号。各写时钟门控器均包括第一输入端、第二输入端及输出端;各写时钟门控器的第一输入端均相连接,共同作为写时钟分组门控电路的第一写时钟输入端;多个写时钟门控器与多个写地址比较器一一对应设置,且各写时钟门控器的第二输入端与相对应的写地址比较器的输出端相连接;各写时钟门控器的输出端分别作为写时钟分组门控电路的不同第一写时钟输出端。

7、在本公开一些实施例中,读时钟分组门控电路包括:第一读时钟输入端、第一读地址输入端以及多个第一读时钟输出端。第一读时钟输入端被配置为接收第一读时钟输出信号。第一读地址输入端被配置为接收第一读地址信号。多个第一读时钟输出端被配置为分别输出多个第二读时钟输出信号。

8、在本公开一些实施例中,读时钟分组门控电路包括:多个读地址比较器以及多个读时钟门控器。各读地址比较器均包括第一比较输入端、第二比较输入端及输出端;多个读地址比较器的第一比较输入端均相连接,共同作为读时钟分组门控电路的第一读地址输入端;各读地址比较器的第二比较输入端分别接收不同的常量信号。各读时钟门控器均包括第一输入端、第二输入端及输出端;各读时钟门控器的第一输入端均相连接,共同作为读时钟分组门控电路的第一读时钟输入端;多个读时钟门控器与多个读地址比较器一一对应设置,且各读时钟门控器的第二输入端与相对应的读地址比较器的输出端相连接;各读时钟门控器的输出端分别作为读时钟分组门控电路相对应的第一写时钟输出端。

9、在本公开一些实施例中,分组寄存器堆存储模块包括:多个第二写时钟输入端、第二写地址输入端、写信号输入端、多个第二读时钟输入端、第二读地址输入端、第三读地址输入端以及读数据信号输出端。多个第二写时钟输入端被配置为分别接收多个第二写时钟输出信号。第二写地址输入端被配置为接收第二写地址信号。写信号输入端,被配置为接收写数据信号。多个第二读时钟输入端,被配置为分别接收多个第二读时钟输出信号。第二读地址输入端被配置为接收第一读地址信号。第三读地址输入端被配置为接收第二读地址信号。读数据信号输出端连接至外部读数据信号。

10、在本公开一些实施例中,分组寄存器堆存储模块包括:多个寄存器堆存储单元以及输出数据选择器。各寄存器堆存储单元均包括写时钟输入端、写地址输入端、写数据输入端、读时钟输入端、读地址输入端及输出端。各寄存器堆存储单元的写时钟输入端分别作为分组寄存器堆存储模块的不同第二写时钟信号输入端。各寄存器堆存储单元的写地址输入端均相连接,共同作为分组寄存器堆存储模块的第二写地址输入端。各寄存器堆存储单元的写数据输入端均相连接,共同作为分组寄存器堆存储模块的写信号输入端。各寄存器堆存储单元的读时钟输入端分别作为分组寄存器堆存储模块不同的第二读时钟输入端。各寄存器堆存储单元的读地址输入端均相连接,共同作为分组寄存器堆存储模块的第三读地址输入端。

11、输出数据选择器包括选择输入端、多个数据输入端及输出端。输出数据选择器的选择输入端作为分组寄存器堆存储模块的第二读地址输入端。输出数据选择器的多个数据输入端与多个寄存器堆存储单元的输出端一一对应连接。输出数据选择器的输出端作为分组寄存器堆存储模块的读数据信号输出端。

12、在本公开一些实施例中,读写控制电路还包括:预启动写时钟门控器以及预启动读时钟门控器。预启动写时钟门控器包括第一输入端、第二输入端及输出端。预启动写时钟门控器的第一输入端连接外部写时钟信号。预启动写时钟门控器的第二输入端连接写使能信号。预启动写时钟门控器被配置为:当写使能信号为高电平时,打开预启动写时钟门控器的输出端,并基于外部写时钟信号输出第一写时钟输出信号。当写使能信号为低电平时,关闭预启动写时钟门控器的输出端;

13、预启动读时钟门控器包括第一输入端、第二输入端及输出端;预启动读时钟门控器的第一输入端连接外部读时钟信号。预启动读时钟门控器的第二输入端连接读使能信号。预启动读时钟门控器被配置为:当读使能信号为高电平时,打开预启动读时钟门控器的输出端,并基于外部读时钟信号输出第一读时钟输出信号。当读使能信号为低电平时,关闭预启动读时钟门控器的输出端。

14、本公开一些实施例还提供了一种读写控制方法,基于如前述实施例中所述的读写控制电路而执行,包括以下步骤:

15、写时钟分组门控电路基于第一写时钟输出信号及第一写地址信号,生成多个第二写时钟输出信号并输出至分组寄存器堆存储模块;

16、读时钟分组门控电路基于第一读时钟输出信号及第一读地址信号,生成多个第二时钟输出信号并输出至分组寄存器堆存储模块。

17、本公开实施例中,利用写时钟分组门控电路对第一写地址信号进行分组门控,生成多个第二写时钟输出信号。同时利用读时钟分组门控电路对第一读地址信号进行分组门控,生成多个第二读时钟输出信号。然后利用分组寄存器堆存储模块接收多个第二写时钟输出信号和多个第二读时钟输出信号。如此,通过对第一写地址信号和第一读地址信号进行分组门控可以降低整个读写控制电路的功耗。此外,本公开实施例配合在空闲时关闭读写时钟门控使能,可以进一步降低整个读写控制电路的功耗。

18、本公开一些实施例还提供了一种读写控制方法,基于如前述实施例中所述的读写控制电路而执行,包括以下步骤:

19、预启动写时钟门控器接收外部写时钟信号及写使能信号;当写使能信号为高电平时,打开预启动写时钟门控器的输出端,并基于外部写时钟信号输出第一写时钟输出信号;当写使能信号为低电平时,关闭预启动写时钟门控器的输出端;

20、预启动读时钟门控器接收外部读时钟信号及读使能信号;当读使能信号为高电平时,打开预启动读时钟门控器的输出端,并基于外部读时钟信号输出第一读时钟输出信号;当读使能信号为低电平时,关闭预启动读时钟门控器的输出端;

21、写时钟分组门控电路基于第一写时钟输出信号及第一写地址信号,生成多个第二写时钟输出信号并输出至分组寄存器堆存储模块;

22、读时钟分组门控电路基于第一读时钟输出信号及第一读地址信号,生成多个第二时钟输出信号并输出至分组寄存器堆存储模块。

23、本公开实施例中,利用写时钟分组门控电路对第一写地址信号进行分组门控,当接收到预启动写时钟门控器输出的第一写时钟输出信号时,生成多个第二写时钟输出信号。同时利用读时钟分组门控电路对第一读地址信号进行分组门控,当接收到预启动读时钟门控器输出的第一读时钟输出信号时,生成多个第二读时钟输出信号。然后利用分组寄存器堆存储模块接收多个第二写时钟输出信号和多个第二读时钟输出信号。如此,通过对第一写地址信号和第一读地址信号进行分组门控可以降低整个读写控制电路的功耗。此外,在空闲时关闭读写时钟门控使能,可以进一步降低整个读写控制电路的功耗。

24、本公开的一个或多个实施例的细节在下面的附图和描述中提出。本公开的其他特征、目的和优点将从说明书、附图以及权利要求书变得明显。

- 还没有人留言评论。精彩留言会获得点赞!