数据读取方法、系统、eFlash控制器及存储介质与流程

本发明涉及,尤指一种数据读取方法、系统、eflash控制器及存储介质。

背景技术:

1、随着智能技术如汽车智能化程度的快速发展,嵌入式系统划定安全优先顺序的需求日益迫切,确保安全的启动过程是保护任何嵌入式系统的首要步骤,也是在应用中预防恶意软件壁垒的必要部分。在电动化、智能化、网联化的趋势下,汽车数据安全越来越重要。eflash闪存是嵌入式系统中常用的非易失存储器,存储启动的关键信息,对其中数据的正确读取和正确性校验对系统的安全性尤为重要。为了保证系统能够稳定可靠的启动成功,一般会对eflash数据进行校验或进行冗余设计。

2、冗余设计普遍采用一个主eflash和一个备用eflash;当主eflash无法正常工作时,才会自动切换到另一个备用eflash中工作,这种情况下,当检测到eflash发生故障再切换到副eflash的中间过程需要一定的切换时间,这个换时间对系统读取的实时性会产生一定的影响。因此,需要一种在eflash发生故障时不需要切换时间的数据读取方法。

技术实现思路

1、本发明的目的是提供一种数据读取方法、系统、eflash控制器及存储介质,解决现有技术中eflash发生故障时需要一定切换时间的问题。

2、本发明提供的技术方案如下:

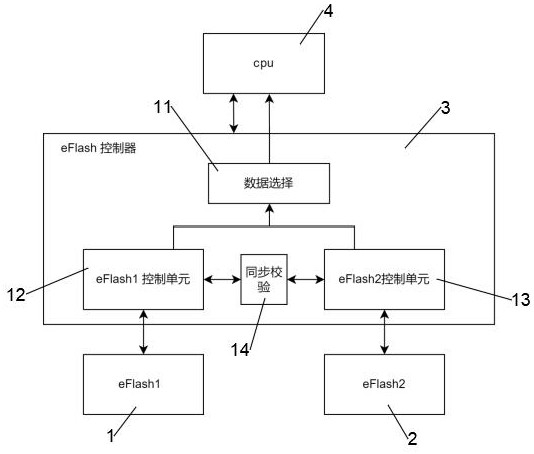

3、本发明提供一种数据读取系统,包括:eflash控制器、一个主eflash和至少一个副eflash,且所述主eflash和所述副eflash在读数据前写入相同数据;

4、所述eflash控制器包括数据选择单元、与所述主eflash对应的第一eflash控制单元,以及与所述副eflash对应的第二eflash控制单元,

5、所述第一eflash控制单元和所述第二eflash控制单元在cpu向所述eflash控制器发起读指令时,同步对其对应的eflash进行读操作;

6、所述数据选择单元根据读取结果选择所述主eflash或所述副eflash的读数据。

7、通过设置第一eflash控制单元和第二eflash控制单元,并在cpu向eflash控制器发起读指令时,同步对主eflash和副eflash进行读操作,使得系统能够根据读取结果选择主eflash或副eflash的读数据,从而即使某个eflash发生故障,也无需进行eflash的切换,省去了eflash的切换时间,提高了数据读取的实时性。

8、在一些实施方式中,所述数据选择单元在所述主eflash和所述副eflash的读数据相同时,选择所述主eflash的读数据。

9、在一些实施方式中,所述第一eflash控制单元和所述第二eflash控制单元还用于记录其对应的eflash的内存纠错信息,所述内存纠错信息包括可纠正错误信息和不可纠正错误信息;

10、所述数据选择单元在所述主eflash和所述副eflash的读数据不同,且至少一个eflash发生不可纠正错误时,选择未发生不可纠正错误的一个eflash的读数据;和/或,

11、所述数据选择单元在所述主eflash和所述副eflash的读数据不同,且各个eflash均未发生不可纠正错误时,丢弃数据;和/或,

12、所述数据选择单元在所述主eflash和所述副eflash的读数据不同,且各个eflash均发生不可纠正错误时,丢弃数据。

13、在一些实施方式中,所述eflash控制器还包括同步校验单元,所述同步校验单元分别与所述第一eflash控制单元、所述第二eflash控制单元连接,用于对所述第一eflash控制单元和所述第二eflash控制单元是否同步进行校验,并在不同步时进行异常中断。

14、通过设置同步校验单元,能够对第一eflash控制单元和第二eflash控制单元是否同步进行校验,以保证主eflash或副eflash的读数据同步,便于进行后续的比较判断;且能够在第一eflash控制单元和第二eflash控制单元不同步时,或主eflash和副eflash均故障进行异常中断或锁步报错,避免系统长时间不能获取准确的读数据。

15、在一些实施方式中,所述同步校验单元在所述第一eflash控制单元和所述第二eflash控制单元行为状态不一致时进行锁步报错;和/或,

16、所述同步校验单元在所述主eflash和所述副eflash的数据使能信号不同时进行锁步报错;和/或,

17、所述同步校验单元在所述主eflash和所述副eflash的读数据不同但均未发生不可纠正错误时进行锁步报错;和/或,

18、所述同步校验单元在所述主eflash和所述副eflash的读数据均包含多bit错误时进行锁步报错。

19、在一些实施方式中,所述主eflash或所述副eflash在发生不可纠正错误时通过ota技术对该eflash的数据进行升级。

20、另外,本发明还提供一种数据读取方法,应用于eflash控制器,所述eflash控制器中包括数据选择单元、第一eflash控制单元和第二eflash控制单元,包括步骤:

21、在接收cpu发送的读指令时,同步控制所述第一eflash控制单元对主eflash,以及所述第二eflash控制单元对副eflash进行读操作,所述主eflash和所述副eflash在读数据前写入相同数据;

22、根据读取结果选择所述主eflash或所述副eflash的读数据。

23、在一些实施方式中,所述的据读取结果选择所述主eflash或所述副eflash的读数据具体包括:

24、在所述主eflash和所述副eflash的读数据相同时,选择所述主eflash的读数据;

25、在所述主eflash和所述副eflash的读数据不同,且至少一个eflash发生不可纠正错误时,选择未发生不可纠正错误的一个eflash的读数据;

26、在所述主eflash和所述副eflash的读数据不同,且各个eflash均未发生不可纠正错误时,丢弃数据;

27、在所述主eflash和所述副eflash的读数据不同,且各个eflash均发生不可纠正错误时,丢弃数据。

28、另外,本发明还提供一种eflash控制器,包括:

29、第一eflash控制单元,与主eflash连接;

30、第二flash控制单元,与副eflash连接,且在接收cpu发送的读指令时,所述第一eflash控制单元和所述第二flash控制单元同步对所述主eflash和所述副eflash进行读操作,所述主eflash和所述副eflash在读数据前写入相同数据;

31、数据选择单元,用于根据读取结果选择所述主eflash或所述副eflash的读数据。

32、另外,本发明还提供一种存储介质,所述存储介质中存储有至少一条指令,所述指令由处理器加载并执行以实现上述的数据读取方法所执行的操作。

33、根据本发明提供的一种数据读取方法、系统、eflash控制器及存储介质,通过设置第一eflash控制单元和第二eflash控制单元,并在cpu向eflash控制器发起读指令时,同步对主eflash和副eflash进行读操作,使得系统能够根据读取结果选择主eflash或副eflash的读数据,从而即使某个eflash发生故障,也无需进行eflash的切换,省去了eflash的切换时间,提高了数据读取的实时性。

- 还没有人留言评论。精彩留言会获得点赞!